貿澤電子 (Mouser Electronics) 即日起開始分銷Integrated Device Technology (IDT) 推出的9FGL PCI Express (PCIe) 時鐘發生器。

2015-07-30 10:14:42 1230

1230 通信線纜,并且為客戶提供解決方案。 Samtec公司搭建的100Gbps數據吞吐量展示方案采用Xilinx Virtex UltraScale FPGA

2017-12-15 11:25:37 1917

1917

業界領先的全新 1.8V 版 VersaClock? 3S 可編程時鐘發生器,為消耗品和計算系統創造具有競爭力的性能、能耗和靈活性。

2017-09-28 10:15:46 8178

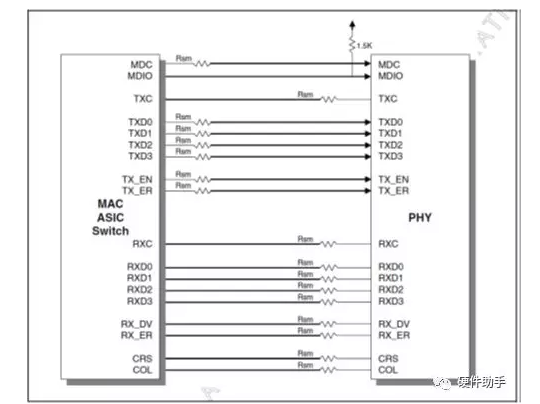

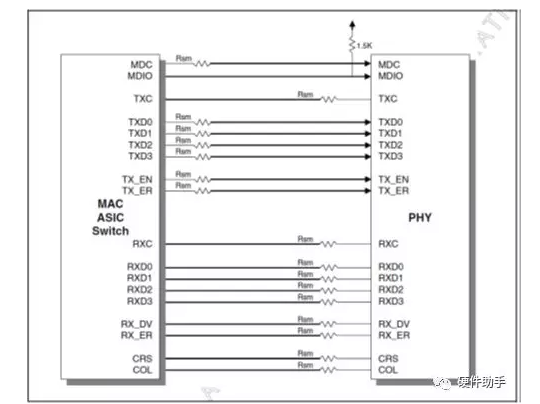

8178 ,下面就針對10Mbps到100Gbps的不同接口進行介紹,最后介紹一下PHY芯片的控制接口MDIO BUS。 1、MII接口 100Mbps速率下,時鐘頻率為25MHz,10M

2020-10-08 00:09:00 8774

8774

新型AEC-Q100認證的時鐘發生器、緩沖器、PCIe時鐘和緩沖器滿足廣泛的車輛自動化應用需求。

2019-09-24 14:25:08 896

896 。XAUI端口通過雙XAUI轉換為SFP +高速夾層卡(HSMC)(從Terasic)到10 Gbps串行以太網,通過低成本SFP +光學可插拔模塊或SFP +直接耦合電纜組件提供網絡接口。該

2018-07-26 16:33:03

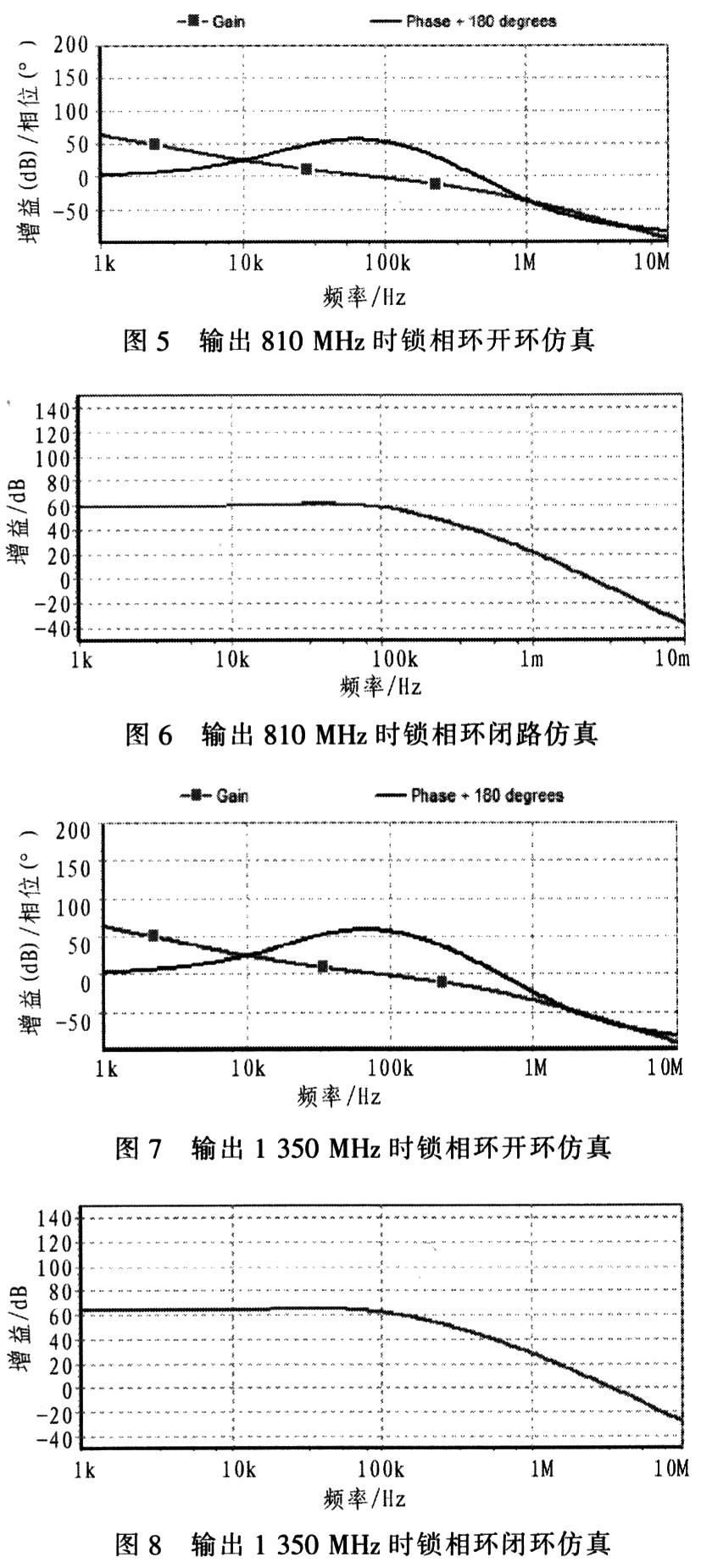

概述:AD9577是一款既提供一個多路輸出時鐘發生器功能,又帶有兩個片上鎖相環內核PLL1和PLL2,專門針對網絡時鐘應用而優化。PLL設計基于ADI公司成熟的高性能、低抖動頻率合成器產品系列,確保實現最高的網

2021-04-06 06:49:57

良好的短期穩定性或抖動。高性能時鐘發生器(如HMC1032LP6GE)可執行頻率轉換操作并提供低抖動時鐘信號,在此基礎上,這些信號可能會分配給各種基站組件。選擇最佳時鐘發生器至關重要,因為欠佳參考時鐘會

2018-10-18 11:29:03

系統設計師通常側重于為應用選擇最合適的數據轉換器,在向數據轉換器提供輸入的時鐘發生器件的選擇上往往少有考慮。然而,如果不慎重考慮時鐘發生器的相位噪聲和抖動性能,數據轉換器動態范圍和線性度性能可能受到嚴重的影響。

2019-07-30 07:57:42

`AD9520-3BCPZ時鐘發生器產品介紹AD9520-3BCPZ詢價熱線AD9520-3BCPZ現貨AD9520-3BCPZ代理王先生***深圳市首質誠科技有限公司, AD9520-3提供多路

2019-07-09 11:50:41

多路輸出時鐘發生器功能,內置專用PLL內核,針對以太網線路卡應用進行了優化。 產品名稱:時鐘發生器 AD9571ACPZPEC特征 全集成VCO/PLL內核 156.25 MHz時,抖動值:0.17

2019-07-09 10:19:09

AKD8140A Ver.2,AK8140??A可編程多時鐘發生器評估板。評估抖動性能和功能很容易

2020-07-27 15:01:46

你好,我是英特爾的Satyajit。我們正在使用CG2 EMAKER(CYPD2103-20FNXIT)在我們的設計中。它類似于無源電纜。我們想用這個設計來攜帶10GbPS霹靂信號。我們的要求

2018-11-09 17:14:16

本應用指南討論了CY2254 PLL時鐘發生器的內部結構,并提出一些使用建議。

2014-09-23 10:00:14

的完整解決方案。今天的云數據中心和企業網采用4個光波長實現100Gbps的通信速率。如圖所示,四個波長收發器在發射和接收方向都使用四套電氣和光器件。如圖可以注意到4個激光驅動器,4個DML激光器,4個

2017-11-30 11:18:44

VL822是一顆USB3.1GEN2(10Gbps)的HUB芯片,有三種封裝分別是QFN88(10x10x0.85 mm);QFN76 9x9x0.85mm ;QFN56(7x7x0.85 mm

2022-09-13 14:17:05

我為 i.MX8M Plus 添加了時鐘發生器 5P49V6965 作為主時鐘源,并更新了設備樹文件,如下所示。我的問題是下面的修改是正確的???imx8mp-evk.dts&i2c4

2023-02-28 08:29:34

概述:MAX3625B是MAXIM公司生產的一款提供三路輸出的低抖動,高精度時鐘發生器。該MAX3625B是為網絡應用而優化的低抖動,高精度時鐘發生器。該器件集成一個晶體振蕩器和鎖相環(PLL)時鐘

2021-05-18 07:39:05

供應 現貨 CG635 斯坦福 時鐘發生器 歐陽R:*** QQ:1226365851溫馨提示:如果您找不到聯系方式,請在瀏覽器上搜索一下,旺貿通儀器儀回收工廠或個人、庫存閑置、二手儀器及附件。長期

2020-08-18 09:08:58

電纜。驅動器提供4種可選擇預加重等級和可選輸入均衡器,在10Gbps時可為長達10英寸的FR-4電路板材料提供補償。 MAX3984還提供SFP兼容的信號丟失(LOS)檢測和TX_DISABLE。可選

2021-05-17 06:16:25

使用100MHz系統時鐘和200MHz系統時鐘,它們都還可以。但是當我想使用160MHz作為系統時鐘時,我無法創建一個具有200MHz輸入和640MHz,160MHz輸出的時鐘發生器,所以我使用兩個時鐘發電機產生

2020-08-11 10:07:25

在我們的設計中,其中一個模塊從外部可配置時鐘發生器芯片接收其時鐘信號。現在在我們的ML507上使用這個時鐘發生器芯片IDT5V9885就在那里任何跳線設置?我們問這個是因為在我們的申請中軟件我們

2019-09-02 08:12:30

云計算、物聯網和虛擬數據中心對以太網速度的要求越來越高,推動著光收發器市場快速增長。當前的10Gbps、40Gbps和100Gbps模塊市場將很快被200Gbps和400Gbps模塊超越。隨著速度

2021-02-24 06:22:34

AD9525 / PCBZ,用于AD9525時鐘發生器的評估板。 AD9525旨在支持長期演進(LTE)和多載波GSM基站設計的轉換器時鐘要求。 AD9525提供低功耗,多輸出,時鐘分配功能和低抖動

2019-02-25 08:38:34

SI52147-EVB,用于PoE無線接入點的時鐘發生器評估板。 Si52147是一款符合PCIe Gen1,Gen2和Gen3標準的9端口PCIe時鐘發生器

2020-08-27 14:27:11

加設輸入多路切換器的分立式單通道 3Gbps SDI 時鐘恢復器。由于無需加設輸入多路切換器,因此美國國家半導體可將引腳數目減少至只有競爭產品的三分一,以及將封裝體積縮小一半。此外,其他的競爭產品必須為每

2018-12-07 10:24:33

小白想請教10Gbps的數據能否傳輸到個人計算機上,通過LABVIEW進行實時處理

2018-08-10 21:30:37

你好,我們想用xc7a35t-2fgg484設計一個10Gbps(最大距離10km)的系統,可以嗎?如果沒有,請推薦一些低價設備?謝謝,Muuu

2020-08-13 09:45:39

的范圍在100fs至300fs之間。這個12kHz-20MHz的標準相位噪聲集成范圍包括鎖相環 (PLL) 頻帶內和頻帶外 (VCO) 噪聲的影響。基準時鐘發生器的相位噪聲性能需要在PLL環路帶寬內

2018-09-05 16:07:30

描述TIDA-00597 可為時鐘發生器提供噪聲非常低的輸出電源。主要特色低噪聲,適用于時鐘發生器輸出電流高達 800mA低相位噪聲輸出功率啟用和禁用

2018-08-22 07:43:40

,以及信號搖擺為800mVp-p的31位PRBS模式(信號的最小數據眼開幅度為600mVp-p)。該測量通過模式發生器的10GHz觸發信號來觸發HP83480A示波器。圖4為來自多路10Gbps數據

2014-12-09 14:36:58

AC1571時鐘發生器一款基于PLL的、適用于5G基站應用的時鐘發生器。采用數字鎖相環技術,以實現最佳的高頻低相噪性能,具有低功耗和高PSRR能力。采用ADPLL技術,管腳兼容843N571,可以

2022-08-11 16:26:33

研究了5Gbps~40Gbps交換技術和IP軟核的實現方法。采用多層結構、模塊化的設計思想,使用Verilog硬件描述語言對40Gbps寬帶交換電路進行編程,實現了一種通用的、容量可變的、可移植

2009-11-27 14:11:39 10

10 AC1571 是用于 5G 基站應用的基于 PLL的時鐘發生器,該芯片采用全數字鎖相環技術,以實現最佳的高頻低相噪性能,并具有低功耗和高PSRR能力。典型應用場景:· 無線基站·

2023-12-12 14:25:17

。時鐘發生器芯片廠家可輸出差分100MHz,125MHz,156.25MHz和單端33.33MHz CPU時鐘,同時輸出6路25MHz緩沖參考時鐘。? 主要特性l 7路單

2023-12-29 09:29:50

。時鐘發生器芯片廠家可輸出差分100MHz,125MHz,156.25MHz和單端33.33MHz CPU時鐘,同時輸出6路25MHz緩沖參考時鐘。? 主要特性l 7路單

2024-02-04 11:41:14

MAX9489/MAX9471多輸出時鐘發生器構建集成時鐘源

摘要:與典型的“本地”時鐘方案相比,集成的多輸出時鐘發生器有許多優勢。本文探討了集中時鐘發生器(如

2008-10-04 20:43:25 922

922

Si5338 業界首個任意頻率、任意輸出的時鐘發生器

高性能模擬與混合信號領導廠商Silicon Laboratories日前發表全新的時鐘發生器和緩沖器系列,可為業

2008-11-10 09:39:44 1763

1763

精密時鐘發生器電路圖

2009-03-25 09:35:22 1054

1054

振蕩器時鐘發生器電路圖

2009-04-13 08:54:22 720

720

摘要:與典型的“本地”時鐘方案相比,集成的多輸出時鐘發生器有許多優勢。本文探討了集中時鐘發生器(如MAX9489和MAX9471)的優點,如:降低系統成本、良好的信號完整性、抑制干

2009-04-22 10:11:53 407

407

摘要:與典型的“本地”時鐘方案相比,集成的多輸出時鐘發生器有許多優勢。本文探討了集中時鐘發生器(如MAX9489和MAX9471)的優點,如:降低系統成本、良好的信號完整性、抑制干

2009-05-03 11:07:05 653

653

MAX3625A 低抖動、精密時鐘發生器,提供三路輸出

2009-08-13 13:01:27 828

828

評估低抖動PLL時鐘發生器的電源噪聲抑制性能

本文介紹了電源噪聲對基于PLL的時鐘發生器的干擾,并討論了幾種用于評估確定性抖動(DJ)的技術方案。推導出的關系式提

2009-09-18 08:46:32 1461

1461

MAX3624 低抖動、精密時鐘發生器,提供四路輸出

概述

MAX3624是一款低抖動精密

2009-09-18 08:56:41 682

682

基于DP標準的擴頻時鐘發生器系統參數研究

1 引言 DP(DisplayPort)接口標準旨在尋求代替計算機的數字視頻接口DVI(Digital Visual Interface)、LCD顯示器的低壓差

2009-11-05 09:23:08 830

830

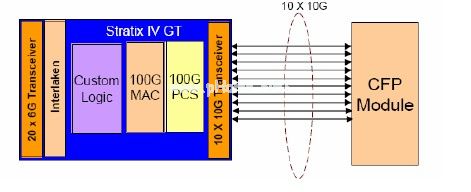

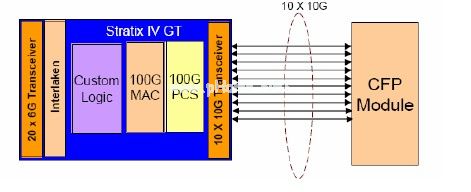

在40G/100G應用中使用10-Gbps收發器

本白皮書介紹向100G 接口過渡的關鍵推動力量,以及怎樣利用FPGA 特有的功能來實現這一高速接口。數據中心以及核心網系統中新

2010-02-04 11:03:41 1290

1290

MAX3625B 抖動僅為0.36ps的PLL時鐘發生器

概述

MAX3625B是一款低抖動、精密時鐘發生器,優化用于網絡設備。器件內置晶體振蕩器和鎖相環(PLL)

2010-03-01 08:56:18 1345

1345

MAX3679A高性能四路輸出時鐘發生器(Maxim)

Maxim推出用于以太網設備的高性能、四路輸出時鐘發生器MAX3679A。器件采用低噪聲

2010-04-14 16:51:49 778

778 如何利用GPS OEM來進行二次開發,產生高精度時鐘發生器是一個研究的熱點問題。在電力系統、CDMA2000、DVB、DMB等系統中,高精度的GPS

2010-07-24 15:45:26 780

780 在電力系統、CDMA2000、DVB、DMB等系統中,高精度的GPS時鐘發生器(GPS同步時鐘)對維持系統正常運轉有至關重要的意義。

那如何利用GPS OEM來進行二次開發,產生高精度時鐘發生

2010-09-17 22:02:44 1273

1273 升特公司(Semtech)宣布推出首個高頻寬100Gbps Gearbox芯片組,用于100Gbps的CFP MSA應用

2011-03-29 09:23:25 2473

2473 IDT面向便攜應用推出全球首款集成可編程時鐘發生器的音頻子系統。新器件通過集成,可實現占板空間的最小化、降低系統成本,同時由于無需長貨期的外部晶體和振蕩器,縮短產品上

2011-08-10 09:01:55 920

920 MAX3636是一個高度靈活,高精度鎖相環(PLL)時鐘發生器為下一代網絡設備的要求低抖動時鐘發生器和強大的高速數據傳輸的分布進行了優化。

2011-10-11 11:15:22 1329

1329

2012年2月23號,北京——Altera公司(NASDAQ:ALTR)今天宣布,使用28-nm Stratix? V GT FPGA成功演示了與100-Gbps光模塊的互操作性,從而支持實現下一代100-Gbps網絡。

2012-02-24 08:41:25 1240

1240 博通(Broadcom)公司宣布,推出業界第一款100Gbps全雙工網絡處理器單元(NPU)。BCM88030

2012-04-28 08:43:39 1236

1236 據外媒報道,繼TeliaSonera升級其泛歐洲網絡后,公司已成為“全球首個建成橫跨歐洲和北美100Gbps網絡的運營商”

2013-03-21 15:12:04 834

834 雙環路時鐘發生器可清除抖動并提供多個高頻輸出

2016-01-04 17:41:13 0

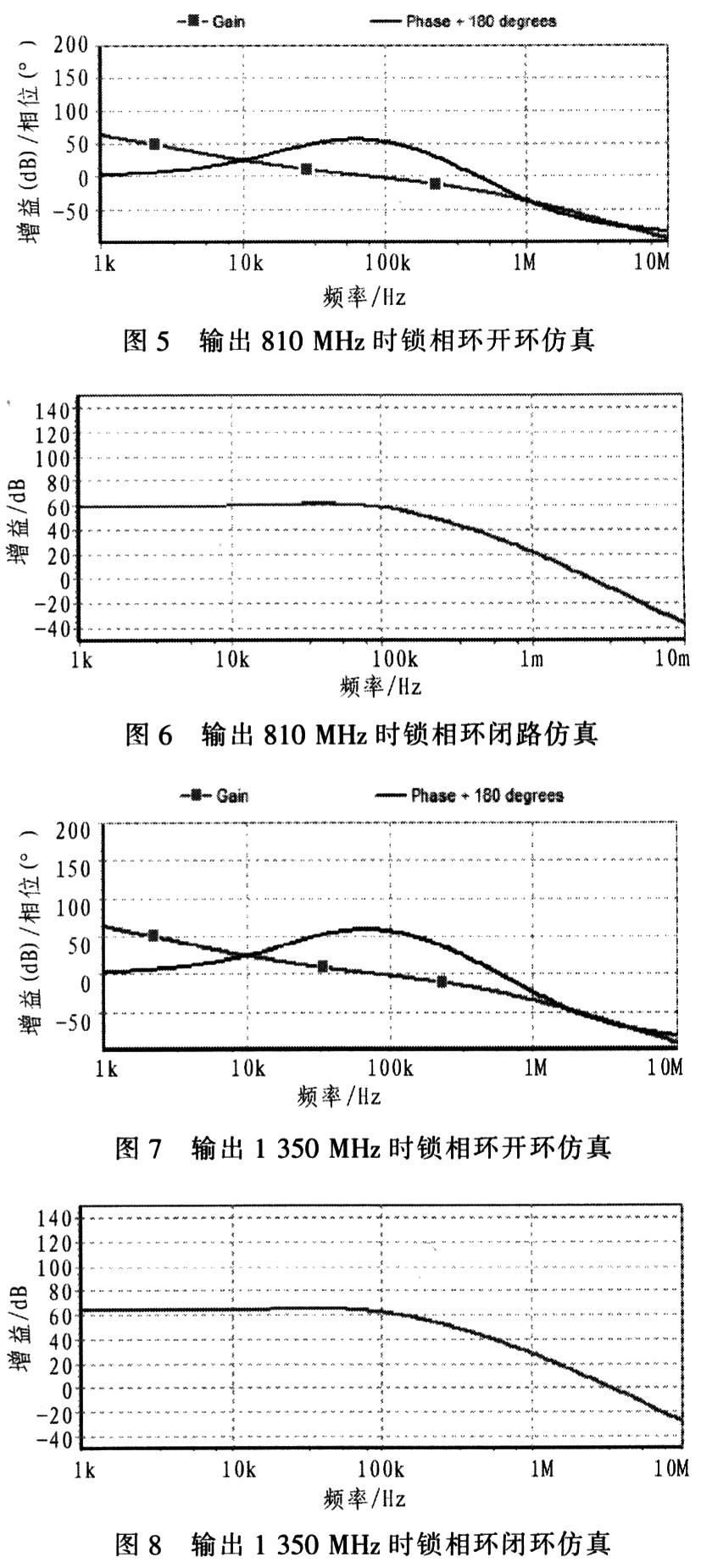

0 10GHz擴頻時鐘發生器的設計_胡帥帥

2017-01-07 21:28:58 1

1 ?XAUI以太網連接單元接口(10Gbps單元接口) ?RXAUI(減少了擴展管腳的單元接口) ?CAUI(100Gbps單元接口) ?XLAUI(40Gbps單元接口) ?CPRI(通用公共無線電接口

2017-02-09 02:15:10 296

296 fluke-p-dx-7可變時鐘結構的任意波形發生器

2017-03-22 09:35:58 0

0 IDT公司的5L35023是VersaClock? 3S可編時鐘發生器,1.8V工作,采用3 PLL架構,每個PLL可單獨可編程,允許有多達6個頻率輸出,內置主動省功耗特性(PPS),性能-功耗平衡(PPB),降過沖技術(ORT)和極低功耗DCO以及動態頻率控制(DFC),

2017-09-20 13:40:42 5

5 Microchip基于MEMS的時鐘發生器

2018-06-07 13:46:00 4534

4534

Xilinx公司業界首款28 nm FPGA Kintex-7 10Gbps 收發器性能演示。

2018-06-01 15:50:00 3960

3960 領先的數據中心,有線電視寬帶和光纖到戶以及電信用光網絡產品開發商AOI公司發布針對下一代400G光模塊應用的100Gbps EML激光器產品。

2018-05-24 17:00:00 7526

7526 Microchip基于MEMS的時鐘發生器

2018-07-08 01:23:00 3933

3933 Silicon Labs(亦稱“芯科科技”)最新發布的Si5332任意頻率的時鐘發生器可以為10/25/100G 數據中心的時鐘設計提供最高級別的集成度,包含通信和工業應用程序中的完整時鐘樹整合,進而降低系統的物料成本并加快開發時程。

2018-08-24 17:51:28 6117

6117 Oclaro日前推出針對100Gbps及其以上速率的相干光傳輸系統的拉曼放大器及混合拉曼/EDFA產品。

2018-10-25 16:21:13 862

862 據麥姆斯咨詢報道,Microchip推出了業界尺寸最小的MEMS時鐘發生器DSC613。這款新器件可在電路板上最多替換掉三個晶振和振蕩器,從而減少高達80%的時鐘元件布板空間。

2018-11-15 16:38:26 3910

3910 Xilinx推出全球首款28nm FPGA,展示10Gbps SERDES功能

Xilinx在Kintex-7 K325T FPGA上展示了10Gbps收發器,這是有史以來第一款28nm FPGA。

2018-11-28 06:30:00 3785

3785 本視頻演示了一個SDNet環境生成的每秒100Gbps的可編程包處理系統中所實現的“無中斷”升級

2018-11-23 06:07:00 2255

2255 云計算是一種新的運算模式,它需要建設大規模的數據中心來服務程序應用和存儲需求。以太網提供了最經濟有效的網絡互連,將提供云計算的大型系統整合在一起。這個龐大的系統在服務器連接方面要求10Gbps的傳輸速率,甚至40Gbps和100Gbps的傳輸速率來滿足大型網絡的協作需要。

2019-01-21 15:38:09 5208

5208 云計算是一種新的運算模式,它需要建設大規模的數據中心來服務程序應用和存儲需求。以太網提供了最經濟有效的網絡互連,將提供云計算的大型系統整合在一起。這個龐大的系統在服務器連接方面要求10Gbps的傳輸速率,甚至40Gbps和100Gbps的傳輸速率來滿足大型網絡的協作需要。

2019-03-04 14:44:06 1000

1000 AD9523:14路LVPECL/LVDS/HSTL輸出 或29路LVCMOS輸出 低抖動時鐘發生器

2019-07-04 06:18:00 3604

3604 如果評選PC中最方便的功能,USB接口顯然是最佳候選人之一,隨著USB-C接口的普及,USB難插對方向的問題也解決了,而且速度越來越快,USB 3.1已經達到10Gbps了。

2019-06-14 09:02:40 5091

5091 新的模數轉換器(ADC)技術使首次實現單芯片100 Gbps相干接收器的設計成為可能。它使用65 nm CMOS技術,可以滿足長距離光學系統的性能和功率要求。它為短途和更高速率的應用提供了未來,并提供

2021-04-14 16:19:04 1452

1452 如果設計不合適,一個通道中的這些多重轉換將會影響信號完整性性能。在10Gbps及以上,通過最大限度地減少阻抗不連續性,得到適合的互連設計已成為提高系統性能的一個重要的考慮因素。由于封裝內有許多不連續區,該收發器封裝在提高回波損耗性能方面存在一個重要瓶頸。

2020-11-12 15:31:05 2606

2606

系統設計師通常側重于為應用選擇最合適的數據轉換器,在向數據轉換器提供輸入的時鐘發生器件的選擇上往往少有考慮。然而,如果不慎重考慮時鐘發生器的相位噪聲和抖動性能,數據轉換器動態范圍和線性度性能可能受到嚴重的影響。

2020-11-22 11:34:38 2666

2666

諾基亞和沃達豐宣布,他們已經成為第一家在光纖無源光網絡(PON)上試驗100Gbps寬帶互聯網的公司。在一個PON波長上就可以達到這樣的速度,而且比現在 “最先進的網絡”快10倍左右。該試驗

2021-02-03 15:03:59 1299

1299 AD9525: 8路LVPECL輸出低抖動時鐘發生器

2021-03-21 15:00:20 0

0 AD9571:以太網時鐘發生器,10個時鐘輸出

2021-04-16 10:21:56 3

3 AD9551:多業務時鐘發生器數據表

2021-04-28 10:30:52 0

0 AD9577:帶雙鎖相環、擴頻和余量的時鐘發生器數據表

2021-04-29 20:06:50 8

8 AD9575:網絡時鐘發生器,雙輸出數據表

2021-05-09 11:06:44 1

1 時鐘發生器AD9516-0技術手冊

2022-01-25 15:59:42 7

7 。Cypress時鐘發生器兼容大量增值性能,如VCXO,擴頻和輸出相位校準,及其兼容流行接口標準的參考時鐘/3.0,如PCIe1.0/2.0/3.0、10GbE、SATA1.0/2.0和USB1.0

2022-04-22 09:02:09 806

806 Corundum是一個基于FPGA的開源原型平臺,用于高達100Gbps及更高的網絡接口開發。Corundum平臺包括一些用于實現實時,高線速操作的核心功能,包括:高性能數據路徑,10G/ 25G

2022-08-02 08:03:22 1538

1538

Integrated Device Technology Inc. (IDT) 發布了兩款時鐘發生器,它們采用單軌 1.8V 電源供電,同時無需多個分立時序組件。據 IDT 稱,與市場上可用的解決方案相比,這可減少電路板占用空間并節省高達 60% 的功耗。

2022-08-10 15:33:06 869

869 USB接口將統一以傳輸帶寬命名,USB4 v2.0對應USB 80Gbps,USB4對應USB 40Gbps,USB 3.2 Gen2x2對應20Gbps,USB 3.2 Gen2對應USB 10Gbps,USB 3.2 Gen1對應USB 5Gbps……

2022-10-20 11:54:15 1173

1173 本文討論電源噪聲干擾對基于PLL的時鐘發生器的影響,并介紹幾種用于評估由此產生的確定性抖動(DJ)的測量技術。派生關系顯示了如何使用頻域雜散測量來評估時序抖動行為。實驗室臺架測試結果用于比較測量技術,并演示如何可靠地評估參考時鐘發生器的電源噪聲抑制(PSNR)性能。

2023-04-11 11:06:39 811

811

極景微發布超小封裝PCIe5.0時鐘發生器日前,極景微(UltraSilicon)宣布,推出兩款支持PCIe5.0接口標準的1輸出及2輸出時鐘發生器,分別為US6D101和US6D102。該芯片具有

2023-02-02 15:25:54 999

999

時鐘合成器和時鐘發生器是兩種用于產生時鐘信號的電子器件,它們在功能和應用上有一些區別。

2023-11-09 10:26:56 298

298 的時鐘發生器件的選擇上往往少有考慮。目前市場上有性能屬性大相徑庭的眾多時鐘發生器。然而,如果不慎重考慮時鐘發生器、相位噪聲和抖動性能,數據轉換器、動態范圍和線性度性能可能受到嚴重的影響。...

2023-11-28 14:33:57 0

0

電子發燒友App

電子發燒友App

評論