作者:李奎利,文光俊,蔡競業(yè),王永平,曾隆月

1 引言

雖然近年來通信技術得到了前所未有的發(fā)展,但是人們在通信技術不斷發(fā)展的同時,對各個通信系統(tǒng)的性能要求也日益提高,以至于現(xiàn)存的通信系統(tǒng)仍然需要發(fā)展,需要科技工作者不斷解決更加苛刻的技術難題。在眾多技術難題中,如何實現(xiàn)高性能的單片全集成射頻壓 控振蕩器仍然是最具挑戰(zhàn)性的技術難題。

隨著無線通信的不斷發(fā)展,頻率資源越來越成為稀缺而珍貴的資源。為了使得無線通信 系統(tǒng)能夠充分地利用頻率資源,并且能夠在信號微弱以及臨近信道信號干擾強的惡劣條件實 現(xiàn)高性能的通信,各種無線通信系統(tǒng)在射頻前端普遍地采用頻率合成器技術。 高性能的頻率合成器通常采用鎖相環(huán)技術實現(xiàn)。鎖相環(huán)通用方框圖如圖1所示:

圖1 基于鎖相環(huán)的頻綜系統(tǒng)方框圖

在上述頻率合成系統(tǒng)中,反饋環(huán)路將使輸出頻頻為參考頻率的N/N+1 倍,如果這個參考頻 率采用穩(wěn)定的低頻石英晶體振蕩器實現(xiàn),那么該頻率合成器系統(tǒng)輸出頻率的穩(wěn)定性將取決于 環(huán)路中壓控振蕩器的相位噪聲特性。為了確保壓控振蕩器具有低的相位噪聲,通常采用 LC-tank 結構構成高性能的壓控振蕩器。雖然在新的世紀里,對低相位噪聲VCO 的研究 取得令人矚目的成就,但是高性能單片集成的射頻VCO 芯片的設計仍然是一項十分艱巨的 任務。本文將基于一種新的VCO結構,采用有效的方法該降低該VCO 的相位噪聲,從而得到 高性能的VCO。

2 VCO 電路的設計

根據(jù)眾所周知的Lee 相位噪聲模型,為了得到盡可能低的相位噪聲,諧振電路的品 質因數(shù)必須盡可能的大。由于基于當前的工藝技術實現(xiàn)高品質因數(shù)的電感很困難,從而導致 基于當前的工藝技術實現(xiàn)高品質因數(shù)的諧振電路也很困難。所以,為了得到盡可能的低的相 位噪聲,在給定工藝條件下,必須采用工藝允許的品質因數(shù)最高的電感來實現(xiàn)高品質因數(shù)的 諧振電路,同時,還必須考慮其它相位噪聲降低技術。

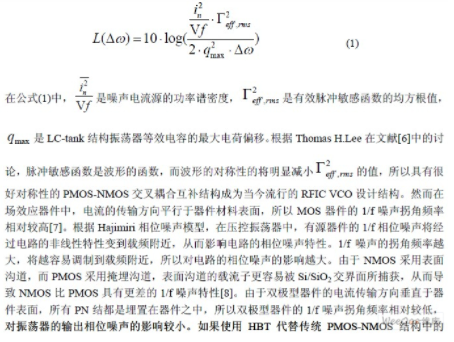

根據(jù)Hajimiri 提出的線性時變相位噪聲理論模型,由周期性準穩(wěn)態(tài)噪聲電流所引起 的相位噪聲可以表示為:

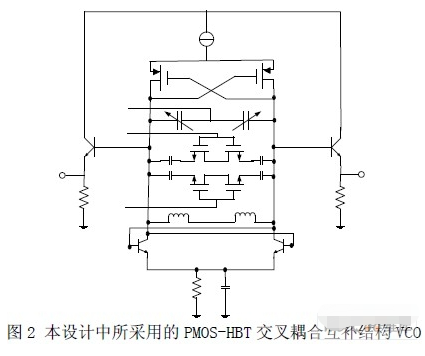

NMOS 器件,將使得VCO 的性能得到顯著的改善。采用該結構的VCO 便是PMOS-HBT 交叉耦合互補結構的VCO。由于降低1/f 噪聲對相位噪聲的影響,所以該結構能得到較好的 相位噪聲特性。因此,本文將采用如圖2 所示的PMOS-HBT 交叉耦合互補振蕩器結構。

在上述結構中,變容二極管(G0,G1),開關對(NM0 和NM1,NM3 和NM4),電感(L0,L1) 以及有源器件的寄生電容,共同構成壓控振蕩器的諧振電路,而PMOS(PM0,PM1) HBT(Q0,Q1)交叉耦合互補結構產(chǎn)生負阻,為電路補充因諧振電路的損耗而消耗掉的能量, 從而維持電路持續(xù)振蕩。為了實現(xiàn)電路的全集成,并能夠得到盡可能高的品質因數(shù),電感 (L0,L1)采用片上螺旋電感。因為電路要實現(xiàn)寬調諧范圍,所以采用調諧范圍比較寬,品質 因數(shù)很高的MOS 變容二極管作為調諧電容。開關對(NM0 和NM1,NM3 和NM4)通過控制位 (B0,B1)來控制開關的關和開,從而實現(xiàn)數(shù)字調諧,這樣不僅能夠展寬調諧范圍,同時還能 夠保證調諧增益具有相對較好的線性度。調諧增益的線性度越好,控制電壓鏈路的噪聲 對輸出相位噪聲的干擾也就越小。

3 驗證結果

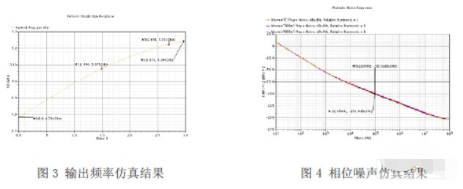

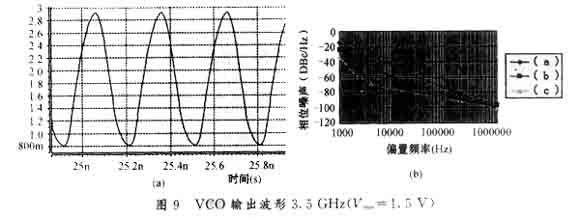

基于TSMC 0.35μm SiGe BiCMOS 工藝,并采用高性能電路仿真軟件Cadence SpectreRF 實現(xiàn)設計。對電路進行設計時,首先設計諧振電路,考慮到有源器件的寄生電容效應,以及 工藝的偏差和溫度補償,所設計的諧振電路的諧振頻率應該高于調諧帶寬的最高頻率。在設 計電路時,直流偏置電流應使該VCO 工作在流控區(qū)域,這樣可以降低電路的輸出相位噪聲 。為了進一步降低相位噪聲,PMOS 和HBT 的器件參數(shù)進行優(yōu)化調整,使VCO 電路輸 出信號保持良好的對稱性。通過Cadence SpectreRF 仿真器仿真的輸出頻率結果如圖3 所示。

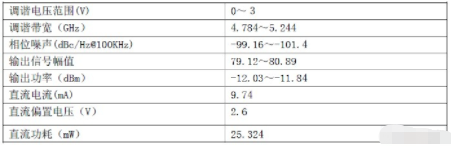

在0 到3V 的調諧電壓范圍內,該VCO 電路的輸出頻率范圍為4.78GHz 到5.244GHz, 調諧帶寬為444MHz。在4.78GHz 到5.244GHz 的頻率范圍內對相位噪聲的仿真結果如圖 4 所示。在4.78GHz 到5.244GHz 的調諧范圍內,在頻偏100KHz 時,輸出相位噪聲的范 圍為-99.16dBc/Hz 到-101.4dBc/Hz。該VCO 電路的性能總結如表1 所示。

4 總結

現(xiàn)代SiGe BiCMOS 工藝不僅提供了用于實現(xiàn)高集成度的CMOS 工藝,而且也提供了 噪聲特性優(yōu)異的HBT 工藝,使制作高興能射頻集成電路成為可能。本論文基于TSMC 0.35μm SiGe BiCMOS 工藝,采用PMOS-HBT 交叉耦合互補結構實現(xiàn)了調諧帶寬為444MHz, 頻偏100KHz 時,最好相位噪聲-100dBc/Hz 的VCO。

本文創(chuàng)新點:當前流行的RFIC VCO 設計結構是PMOS-NMOS 交叉耦合互補結構,雖然該 結構具有較好相位噪聲特性,但是NMOS 器件的閃爍噪聲特性非常差,限制了相位噪聲 進一步降低。本文充分利用BiCMOS 工藝的優(yōu)勢,采用PMOS-HBT 交叉耦合互補結構,同 時采用電容陣列調諧技術,在保證VCO 具有較低相位噪聲的同時,盡可能的展寬調諧頻 率的范圍,實現(xiàn)地相位噪聲和寬調諧范圍的VCO 設計。

責任編輯:gt

-

二極管

+關注

關注

148文章

9816瀏覽量

168034 -

振蕩器

+關注

關注

28文章

3858瀏覽量

139512 -

頻率合成器

+關注

關注

5文章

222瀏覽量

32444

發(fā)布評論請先 登錄

相關推薦

ADI推出全新四頻段VCO 提供更低相位噪聲及低水平電流消耗

Z-COMM VCO的相位噪聲測量

關于ADF4351開環(huán)VCO相位噪聲測試問題

電源技巧#8:設計12GHz,超低相位噪聲(0.09 ps rms抖動)鎖相環(huán)

一款1.9~5.7 GHz寬帶低噪聲BiCMOS LC VCO設計

如何用交叉耦合電流饑餓型VCO設計實現(xiàn)降低時鐘頻率的相位噪聲?

有誰能解答關于仿真VCO相位噪聲的問題嗎?

相位噪聲分析儀-從1 MHz到50/65 GHz

APPH系列相位噪聲分析儀和VCO測試儀—輸入高達40GHz

免調中頻VCO的實現(xiàn)

高速低相位噪聲VCO設計

基于新VCO結構實現(xiàn)地相位噪聲和寬調諧范圍的設計

基于新VCO結構實現(xiàn)地相位噪聲和寬調諧范圍的設計

評論