鎖相環頻率合成器ADF4106為速度和RF相位噪聲性能樹立了新的基準,完全適合在高達6.0 GHz的頻率下工作。這樣可以大大簡化 5.4 GHz 至 5.8 GHz 上層 ISM 頻段的設計。它采用先進的 0.35μm BiCMOS 工藝制造,取代了引腳和軟件兼容的 4 GHz ADF4113,成為市面上最快的整數 N 分頻頻率合成器,并且開機時相位噪聲可降低 3 dB!它只需要一個 3.3V 電源,但其 VP 引腳的額定電壓高達 5.5 V,以便與基站中使用的模塊化 VCO 通常需要的調諧電壓電平兼容。

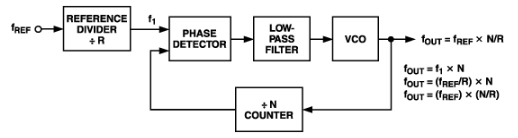

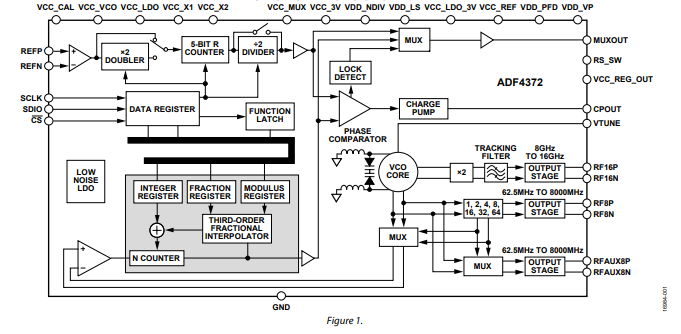

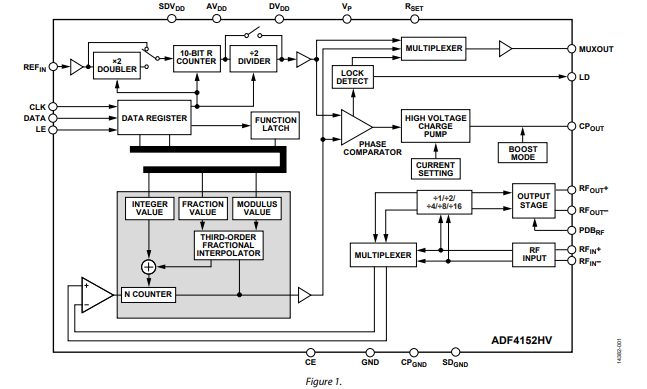

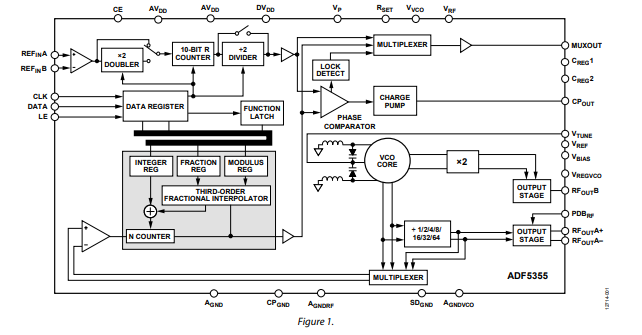

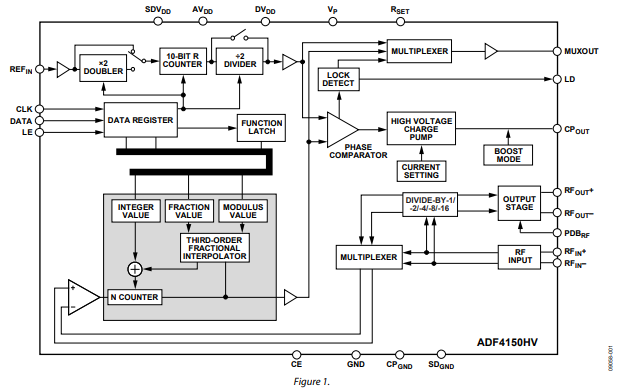

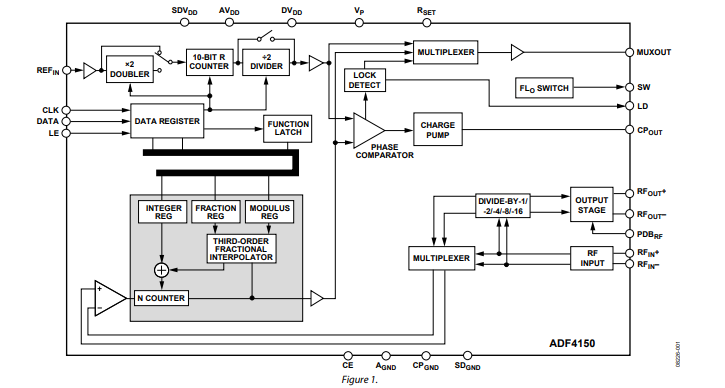

圖1.ADF4106的功能框圖

頻率合成器ADF4106(圖1)可用于在無線接收器和發射器的上變頻和下變頻部分實現本振(LO)。它由一個低噪聲數字鑒頻鑒頻器(PFD)、一個精密電荷泵、一個可編程基準分頻器、可編程A和B計數器以及一個雙模預分頻器(P/P+1)組成。A(6 位)和 B(13 位)計數器與雙模預分頻器 (P/P+1) 配合使用,實現 N 分頻器 (N = BP+A)。此外,14位基準(R)計數器允許在PFD輸入端選擇REFIN頻率。如果頻率合成器與外部環路濾波器和壓控振蕩器 (VCO) 配合使用,則可以實現完整的鎖相環 (PLL)。其非常高的帶寬意味著在許多高頻系統中可以省去倍頻器,從而簡化系統架構并降低成本。

寬帶寬使其能夠用作 6GHz 本地振蕩器

圖2.標準鎖相環架構

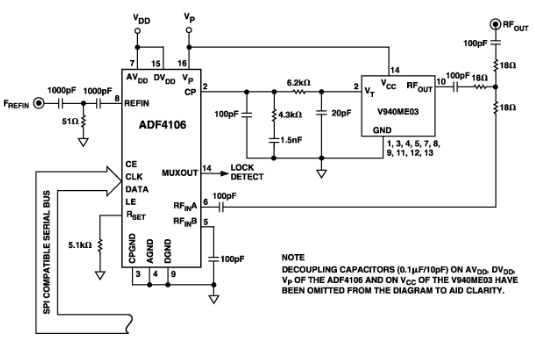

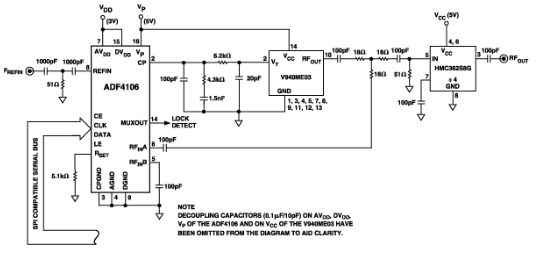

ADF4106及其前身ADF4113使用的標準PLL系統架構如圖2所示。由于ADF4113的最大工作頻率約為4 GHz,因此更高的頻率需要使用倍頻器,這通常需要額外的RF放大器才能為倍頻器產生足夠的電平。使用ADF4106省去了倍頻器及其相關電路,實現了更簡單、更節能的LO。例如,圖3所示設計產生的RF輸出頻率為1 MHz通道間隔,頻率范圍為5.4 GHz至6.0 GHz。在上限測量的相位噪聲為-83 dBc/Hz。

圖3.ADF4106用于實現6.0 GHz本振。

由于ADF4106在這種高工作頻率下的輸入阻抗非常接近50 Ω,因此RF輸入端不需要50歐姆端接電阻即可實現最大功率傳輸效率。在較低頻率下工作時,數據手冊中的s參數給出了匹配所需的阻抗值。

低相位噪聲使其可用作低噪聲、快速建立的 1.5GHz 本振

ADF4106與寬帶寬分壓器配合使用,可以改善標準本振電路在低于2.0 GHz頻率時的相位噪聲和鎖定時間。

典型的無線系統可能以 200 kHz 的增量生成從 1450 MHz 到 1500 MHz 的頻率。為此,使用整數 N 分頻架構,需要 200 kHz 的相位/頻率檢波器參考頻率,N 值將在 7250 (1450 MHz) 到 7500 (1500 MHz) 之間變化。

使用ADF4106獲得最佳性能,相位噪聲系數為–88 dBc/Hz。 此類系統中的典型基準雜散在88 kHz時為–200 dBc,在90 kHz時為–400 dBc。實現20 kHz環路帶寬時,10度相位誤差的典型鎖定時間為250 μs。

圖 4a.用于改善鎖定時間、相位噪聲和參考雜散的架構。

但是,ADF4106的寬帶工作允許考慮另一種架構,如圖4a所示。在這種配置中,內核PLL的工作頻率是最終所需輸出頻率的倍數。在上面給出的示例中,最終所需的頻率范圍為1450 MHz至1500 MHz。器件頻率范圍內的倍數為 5800 MHz 至 6000 MHz(所需輸出頻段的 4 倍)。在圖4a所示的方案中,FPFD的工作頻率為800 kHz,FVCO頻段為5800 MHz至6000 MHz,最終系統LO輸出由FVCO除以4獲得。

FOUT = (FPFD × N)/X (1)

下面概述了使用此體系結構的一些后果。

降相降噪

頻率合成器的相位噪聲為10對數F聚苯乙烯關系。這意味著PFD頻率每增加一倍,頻率合成器相位噪聲就會下降3 dB。但是,VCO的輸出將被分頻,其相位噪聲遵循20 logX規則。因此,X每增加一倍,相位噪聲性能將增加6 dB。如果 PFD 頻率翻了兩番,如上所述,FVCO除以四,得到正確的F外.因此,由于F聚苯乙烯與使用標準架構相比,采用圖12a時,相位噪聲性能總增益為6 dB,因此采用圖4a時,相位噪聲性能總增益為94 dB。在上例中,產生的相位噪聲為–<> dBc/Hz。

基準雜散減少

在整數N分頻PLL中,雜散頻率出現在VCO輸出端PFD頻率的整數倍處。在圖 4a 中,如果您考慮FVCO,這些馬刺將在F聚苯乙烯,2F聚苯乙烯,3F聚苯乙烯等。然而,在f外,基頻除以X(X = 4),但雜散頻率仍存在于PFD頻率的整數倍處。但請注意,它們的振幅降低了 20 logX (20 log4 = 12 dB)。參見圖 4b。

圖 4b.比較 F 處的輸出頻譜VCO和 F外圖4a。

因此,使用圖 4a 中的架構(X = 4),并生成 1450 MHz 至 1500 MHz 的 FOUT,間距為 200 kHz,頻率雜散將以 800 kHz(PFD 頻率)的整數倍存在于低于 –90 dBc 的水平。請注意,雖然步進頻率為200 kHz,但最低頻率雜散為800 kHz。

鎖定時間更短

由于圖4a中的PFD以更高的頻率工作,因此相位比較以更高的速率進行;這將導致循環鎖定得更快。此外,由于PFD頻率較高,因此可以獲得更寬的環路帶寬,這也有助于改善鎖定時間。在本例中,對于70 kHz的PLL環路帶寬,鎖定時間約為10 μs,相位誤差的80°以內。

圖 4a 的實際實現如圖 5 所示。

圖5.使用帶有輸出分頻器的ADF4106產生1.5 GHz本振。

總而言之,圖5所示電路具有以下性能:

| 相位噪聲 | –94 dBc/Hz @ 1kHz 偏移 | |

| 參考馬刺 | <–100 dBc(系統本底噪聲)@ 200kHz、400kHz、600kHz 偏移 | |

| –90 dBc @ 800-kHz 偏移 | ||

| 鎖定時間 |

70 μs 至 10° 以內的相位誤差 |

這種性能改進的代價是輸出分壓器的額外成本和整個系統的額外功耗(HMC通常會使ADF68的4106 mA電流要求增加13 mA)。因此,提高性能必須是使用此體系結構的關鍵要求。實現所需的額外電路板空間極少,因為 HMC 采用 8 引腳 SOIC 封裝。

帶寬

0.35 μm BiCMOS制造工藝和RF設計技術的謹慎應用使ADF4106的預分頻器部分能夠在高達6.0 GHz的頻率下工作,輸入電平為–10 dBm(參考50 Ω),在–40至+85°C工業溫度范圍內得到保證。下圖6顯示了采用TSSOP封裝的ADF4106在–40°C、+25°C和+85°C下的典型靈敏度曲線。 可以清楚地看到,6 GHz 的性能完全在信號低于 –15 dBm 的器件的范圍內。

圖6.ADF4106靈敏度與頻率的關系

相位噪聲

相位噪聲是衡量本振信號純度的指標,是無線電本振部分最關鍵的規格,直接影響接收器靈敏度。它是在給定載波偏移時,1 Hz帶寬內噪聲功率與輸出載波功率的比率。以對數比表示,相位噪聲的單位為dBc/Hz。 相位噪聲通常使用頻譜分析儀測量。

圖7.基本鎖相環模型。

圖7所示電路將用作討論相位噪聲的電路模型。

鎖相環中的總相位噪聲(dB)可以表示如下:

PNTOTAL = PNSYNTH + 20 logN + 10 logFPFD (2)

哪里

PN總是PLL的總相位噪聲

PN合成器相位噪聲是由PLL頻率合成器電路本身

引起的相位噪聲20 log N是由于與反饋比相關的頻率放大倍率引起的相位噪聲增加,1/N。

10 日志F聚苯乙烯是與輸入PFD頻率相關的噪聲增加。圖8中的圖表顯示了ADF4106的相位噪聲特性與PFD頻率FPFD的函數關系。

圖8.ADF4106相位噪聲與PFD頻率的關系

在給定測量的總噪聲下,合成器噪聲可以推斷為:

PNSYNTH = PNTOTAL – 20 logN – 10 logFPFD (3)

這為PLL頻率合成器電路本身提供了一個品質因數,而不管PLL N值和PFD頻率貢獻的噪聲如何,因為對于要比較的任何類似電路,這些噪聲都是相同的。對于ADF4106,該數字為–219 dBc/Hz,比ADF3提高了4113 dB,ADF<>是相位噪聲方面最好的整數N分頻頻率合成器。

利用這種相位噪聲品質因數,工程師可以計算出任何給定PFD頻率和RF輸出頻率的總PLL相位噪聲。例如,考慮生成頻率為 1700 MHz 至 1800 MHz、通道間隔為 200 kHz 的本振信號。使用公式(2),使用ADF4106作為PLL頻率合成器的近載波相位噪聲為:

PNTOTAL = –219 + 20 log(9000) + 10 log(200 x 103)= (–219 + 79 + 53) dBc/Hz= –87 dBc/Hz

圖8顯示ADF4106遵守10個對數F聚苯乙烯“規則”(PFD相位噪聲與對數頻率基本成線性關系)一直相當一致,一直到30 MHz。一旦PFD頻率超過1 MHz,一些整數N分頻器件就會開始迅速退化。

請注意,–219 dBc/Hz品質因數是通過將圖8外推回1 Hz而獲得的。該圖可用于在已知N值后快速識別給定PLL設置中可能的性能。例如,圖表上的200 kHz對應于-166 dBc/Hz的相位噪聲。 增加20 logN (79 dBc)得到-87 dBc/Hz的PLL相位噪聲。

審核編輯:郭婷

-

頻率合成器

+關注

關注

5文章

297瀏覽量

32881 -

pll

+關注

關注

6文章

891瀏覽量

136542 -

計數器

+關注

關注

32文章

2292瀏覽量

96535

發布評論請先 登錄

設計帶有新型寬帶整數N分頻PLL頻率合成器的直接6GHz本振

設計帶有新型寬帶整數N分頻PLL頻率合成器的直接6GHz本振

評論