為什么單片機內置時鐘源不經過pll也可以分頻?

單片機內置時鐘源不經過PLL也可以實現分頻,原因在于單片機內置時鐘源自帶分頻器,可以通過軟件設置分頻系數來控制內部時鐘頻率。

在單片機內部,通常會集成一個晶振或者振蕩器作為時鐘源,該時鐘源會被一個精密的計數器控制,并使用內部或者外部的分頻器將計數器的輸出頻率降低到所需的頻率水平。這種內置分頻器通常可以不依賴于PLL,就可以實現分頻工作。

在單片機內部的時鐘源中,一般會采用分頻器來控制時鐘頻率。分頻器就是將時鐘頻率按一個固定的比例進行除法運算,得到所需的時鐘頻率。分頻因子可以通過設定某個寄存器的值來實現。

比如,對于一個24 MHz的時鐘源,我們希望得到1 MHz的時鐘,就可以使用一個24分頻器來進行分頻,使得輸出頻率降低到1 MHz的水平。對于一些高速設備,可以通過連接多個分頻器來得到更低頻率的輸出。

總的來說,單片機內置時鐘源可以通過內部分頻器實現分頻,不需要自帶PLL。這種技術可以幫助開發人員在一定程度上簡化硬件設計,降低成本,提高可靠性。同時,還可以通過軟件簡單地控制分頻比例,適應不同的應用場景和需求。

-

單片機

+關注

關注

6064文章

44931瀏覽量

647439 -

pll

+關注

關注

6文章

884瀏覽量

136092 -

計數器

+關注

關注

32文章

2286瀏覽量

96071 -

時鐘源

+關注

關注

0文章

97瀏覽量

16247

發布評論請先 登錄

Analog Devices Inc. ADF4382x小數N分頻鎖相環 (PLL)數據手冊

集成整數 N 分頻 PLL 和 VCO 的 350-5000 MHz 寬帶接收混頻器 skyworksinc

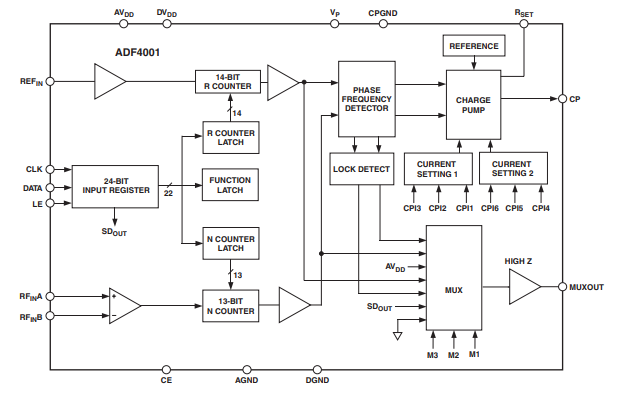

ADF4001 200MHz時鐘發生器PLL技術手冊

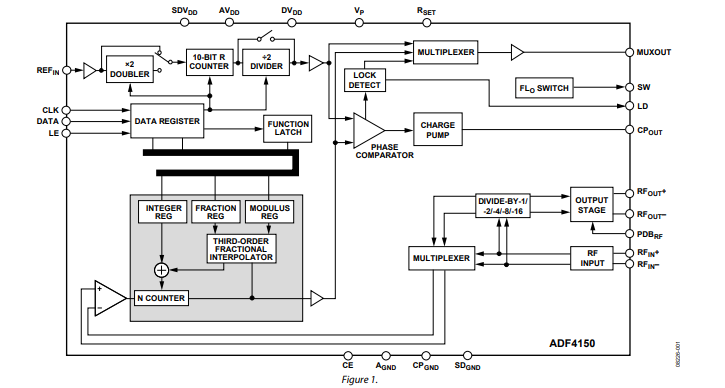

ADF4150小數N/整數N分頻PLL頻率合成器技術手冊

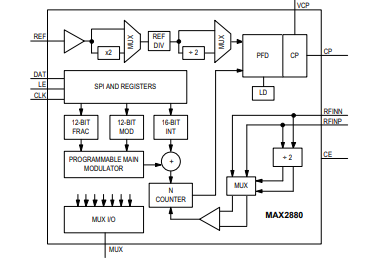

MAX2880 250MHz-12.4GHz、高性能、分數/整數型N分頻PLL技術手冊

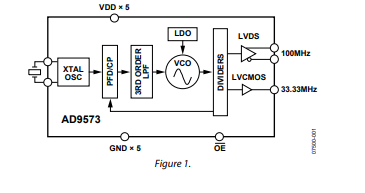

AD9573 PCI-Express時鐘發生器IC,PLL內核,分頻器,兩路輸出技術手冊

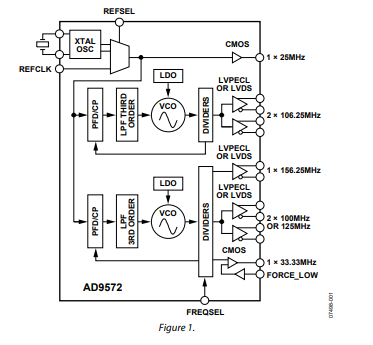

AD9572光纖通道/以太網時鐘發生器IC,PLL內核,分頻器,7路時鐘輸出技術手冊

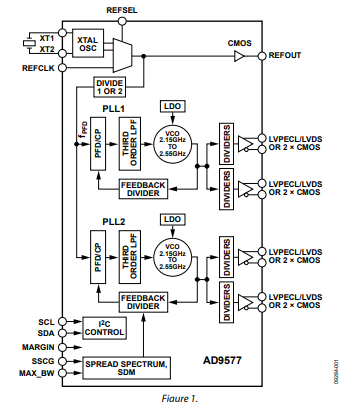

AD9577帶雙路PLL、擴頻和余量微調功能的時鐘發生器技術手冊

PGA870可否不經過電容,直接連接至輸入端口?

CDC906可編程3-PLL時鐘合成器/乘法器/分頻器數據表

PLL1705/PLL1706雙通道PLL多時鐘發生器數據表

CDCE706可編程3-PLL時鐘合成器/乘法器/分頻器數據表

紫光同創——PLL IP 的使用(Logos2)

LVDS用法:LVDS RX 時鐘選擇 LVDS的PLL的復位信號的處理

為什么單片機內置時鐘源不經過pll也可以分頻?

為什么單片機內置時鐘源不經過pll也可以分頻?

評論