大模型時(shí)代已經(jīng)到來(lái),AI大模型技術(shù)快速成熟,進(jìn)入萬(wàn)億參數(shù)時(shí)代,對(duì)于AI算力性能要求越來(lái)越高,表現(xiàn)為計(jì)算系統(tǒng)的節(jié)點(diǎn)內(nèi)卡間互聯(lián)與節(jié)點(diǎn)間的網(wǎng)絡(luò)互聯(lián),高速互聯(lián)的底層是PCIe,對(duì)于PCIe的技術(shù)迭代和落地迫切。

一、PCIe 5.0 /6.0技術(shù)升級(jí)

1)信號(hào)速率方面

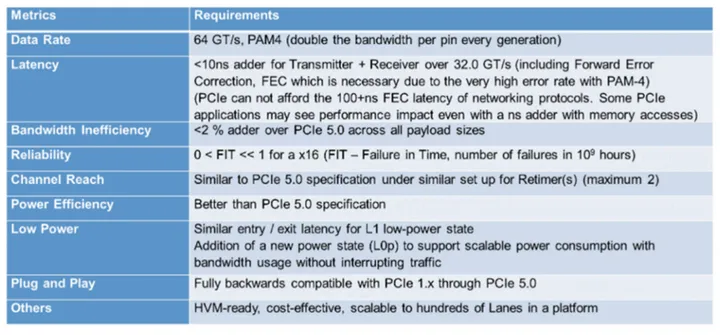

從PCIe 3.0、4.0、5.0 到 6.0,數(shù)據(jù)速率翻倍遞增,6.0支持64GT/s,16路雙向傳輸帶寬可達(dá)256GB/s。

圖1:PCIe技術(shù)變化2)調(diào)制格式方面

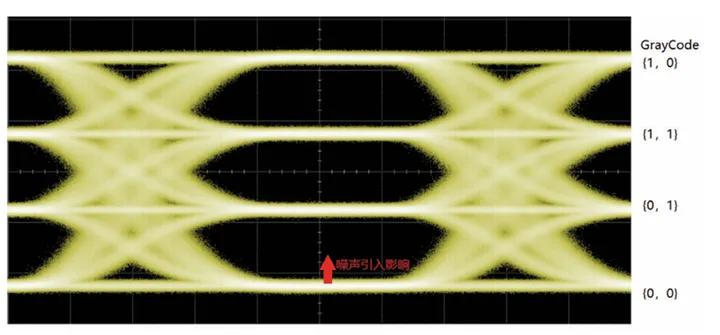

PCIe 3.0-5.0 都采用NRZ調(diào)制格式,在PCIe 6.0時(shí)首次采用高階調(diào)制格式PAM4,在信號(hào)幅度相同的情況下信噪比天然會(huì)下降約9.5dB,因此對(duì)噪聲更加敏感(比如電源噪聲、串?dāng)_、反射等),為降低該影響,采用了格雷碼映射(MSB,LSB),如下展示了格雷碼映射的PAM4眼圖,在噪聲影響下,低比特LSB更易引起反轉(zhuǎn)導(dǎo)致出錯(cuò),若噪聲幅度較高,也會(huì)引起2bit反轉(zhuǎn),但概率較低。

圖2:PAM4 眼圖

3)收發(fā)架構(gòu)方面

為支持PAM4調(diào)制格式,通常采用DAC產(chǎn)生信號(hào),ADC接收信號(hào),發(fā)送側(cè)為克服傳輸鏈路影響,通常會(huì)用多抽頭的FIR實(shí)現(xiàn),PCIe 6.0采用4抽頭的FIR,接收側(cè)為補(bǔ)償高頻損耗和多比特碼間干擾會(huì)用到CTLE+DFE,當(dāng)前架構(gòu)會(huì)利用DSP技術(shù)根據(jù)ADC模數(shù)轉(zhuǎn)換的數(shù)據(jù)點(diǎn)實(shí)現(xiàn)數(shù)字域處理,該技術(shù)也可以有效克服PVT的變化對(duì)信號(hào)帶來(lái)的影響。

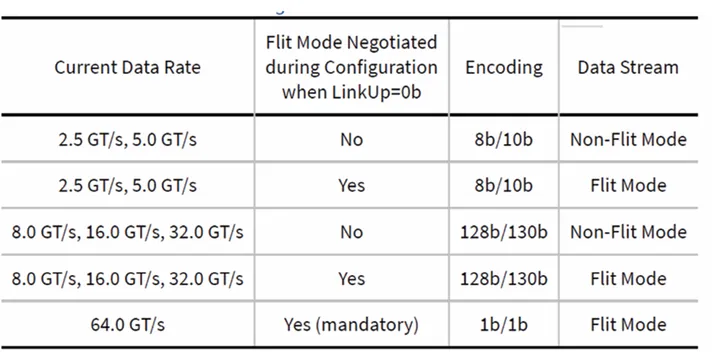

4)編碼與數(shù)據(jù)流方面PCIe 3.0-5.0 均采用128b/130b編碼方式,相比PCIe 1.0-2.0 降低了開銷提高了編碼效率,默認(rèn)支持Non-Flit流模式,PCIe 6.0采用1b/1b編碼并且必須支持Flip流模式。Non-Flit模式支持可變大小TLP、4字節(jié)CRC用于TLP、2字節(jié)CRC用于DLLP。而Flit模式則支持256字節(jié)固定長(zhǎng)度包括235字節(jié)TLP、6字節(jié)DLP、8字節(jié)CRC 和6字節(jié)FEC,沒有Sync Header/Framing Token,TLP 和DLLP 沒有獨(dú)立的CRC,通過(guò)這些開銷的優(yōu)化相對(duì)提高了帶寬利用率。

圖3:PCIe速率、Flit、編碼等特點(diǎn)

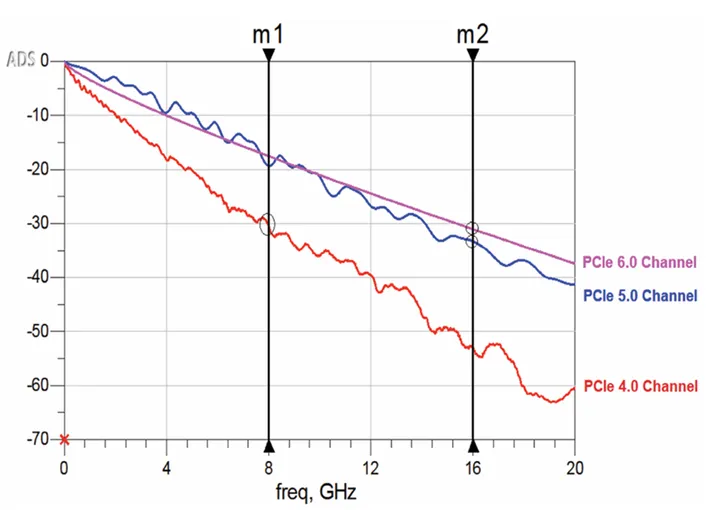

5)互連通道及連接器方面

PCIe 5.0~6.0 相比PCIe 1.0~4.0 速率高,SI、PI 要求也有提高。電源方面,插卡最大功耗可提升至600W,將 在 6.0 CEM中更新;信號(hào)方面為保證信號(hào)完整性要求使用表貼連接器;互連通道方面,與PCIe 5.0類似,要求主板支持約12 inch,插卡支持約3-4 inch,可以想象下,如果PCIe 6.0仍舊采用NRZ調(diào)制格式,64GT/s速率奈奎斯特頻點(diǎn)在32GHz,那 么 通 道 IL將小于-60dB(參考下圖通道仿真結(jié)果),很難通過(guò)現(xiàn)有技術(shù)實(shí)現(xiàn)該信號(hào)的高頻補(bǔ)償,考慮實(shí)現(xiàn)成本和技術(shù)復(fù)雜度,采用高階調(diào)制PAM4是種不錯(cuò)選擇,相比PCIe 5.0奈奎斯特頻率不變,當(dāng)前可用板材下可傳輸相似距離。

圖4:不同信道插損仿真圖

6)誤碼率方面PCIe 3.0~5.0 均要滿足1E-12,PCIe 6.0 由于采用PAM4,對(duì)噪聲和反射更敏感,結(jié)合格雷碼映射特點(diǎn)(易發(fā)生單bit 錯(cuò) 誤 ), 接 收 側(cè) 會(huì) 關(guān) 注 first bit error,規(guī)范會(huì)用FBER衡量。由于鏈路接收機(jī)會(huì)用到DFE均衡,若有單bit出錯(cuò),它這會(huì)引起后續(xù)接連出錯(cuò)。如果造成誤碼的源是共有的,比如電源噪聲,那么也會(huì)引起其他lane出錯(cuò),系統(tǒng)BER依賴于FBER和lane間的錯(cuò)誤相關(guān)性。規(guī)范定義了FBER是1E-6,那么為什么是1E-6呢?能否放寬至1E-4, 滿足PCIe 5.0通常的傳輸距離或IL目標(biāo)呢?答案是否定的。參考以太網(wǎng)標(biāo)準(zhǔn)放寬至1E-4,需要使用復(fù)雜RS-FEC 糾錯(cuò),延時(shí)將增加到約100ns量級(jí),這對(duì)負(fù)載和存儲(chǔ)等對(duì)時(shí)延敏感的應(yīng)用是一個(gè)很大的挑戰(zhàn)。一旦確定FEC技術(shù)將應(yīng)用至整個(gè)PCIe 6.0的生命周期,傳輸通道優(yōu)化還有其他更多手段,比如更新板材,更復(fù)雜信號(hào)調(diào)理等。為滿足FBER=1E-6目標(biāo),PCIe 6.0引入輕量級(jí)FEC和魯棒性強(qiáng)的CRC算法實(shí)現(xiàn)修正和錯(cuò)誤檢測(cè)。相比100G/400G以太網(wǎng)標(biāo)準(zhǔn)中經(jīng)常用到的RS(544,514), 該 FEC實(shí)現(xiàn)相對(duì)簡(jiǎn)單,在固定包長(zhǎng)度Flit模式下,6字節(jié)的FEC“保護(hù)”242字節(jié)Payload和8字節(jié)CRC,2字節(jié)1組實(shí)現(xiàn)FEC Group通過(guò)交織方式抵抗突發(fā)錯(cuò)誤。如果FEC解碼完成,但CRC仍檢測(cè)到錯(cuò)誤,那么接收側(cè)會(huì)發(fā)送NAK啟動(dòng)重傳,為提高效率,該模式下不會(huì)重傳NOP-only TLP 包。通過(guò)上述FEC、CRC適配FBER=1E-6 要求,同時(shí)保證出錯(cuò)情況下重傳概率在5E-6、帶寬額外消耗約0.05%、FIT接近0。

圖5:展示PCIe 6.0的重要變化

二、PCIe 6.0 測(cè)試測(cè)量挑戰(zhàn)

1)PCIe 6.0 規(guī)范狀態(tài)

當(dāng)前PCIe 6.0 Base spec v1.0 已經(jīng)發(fā)布,CEM Spec 和Phy Test Spec 還在討論中。

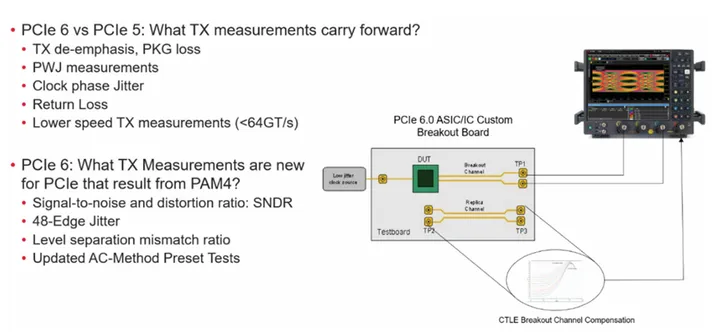

2)Tx 信號(hào)完整性方面

相比PCIe 5.0,PCIe 6.0新增了SNDR、RLM、JnU、Jrms 和Preset 測(cè)試。

圖6 PCIe 6.0 Tx 測(cè)試參數(shù)變化

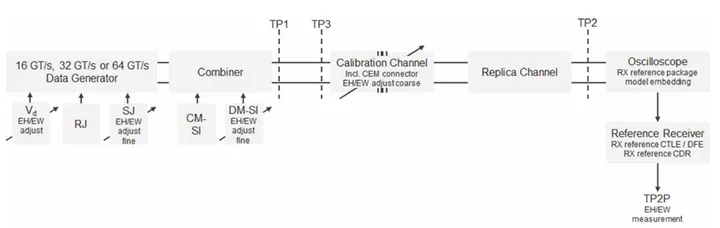

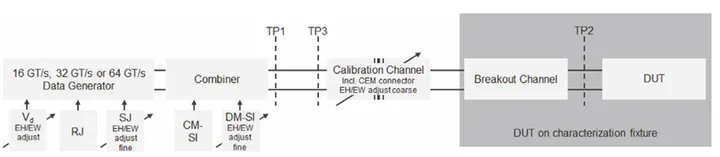

3)Rx接收誤碼率方面在16G、32G和64GT/s接收校準(zhǔn)時(shí)RJ不再是主要調(diào)節(jié)目標(biāo)EH/EW的參數(shù),通過(guò)信道自身插損調(diào)節(jié)實(shí)現(xiàn)粗調(diào),SJ/DMSI 實(shí)現(xiàn)細(xì)調(diào),綜合實(shí)現(xiàn)目標(biāo)EH/EW。Rx Reference Package的S參數(shù)模型是嵌在示波器中實(shí)現(xiàn)的,通過(guò)TP2端面信號(hào)測(cè)量和嵌入S參數(shù)的計(jì)算并結(jié)合參考的CTLE+DFE/CDR得到TP2P EH和EW。這里的EH和EW是目標(biāo)PAM4眼圖的Top Eye 參 數(shù)( 6mV EH / 0.1 UI EW @1e-6 BER)。目 前Sigtest 還未發(fā)布,校準(zhǔn)時(shí)采用seasim 作為數(shù)據(jù)處理工具。

圖7:PCIe 6.0芯片Rx校準(zhǔn)

64GT/s 接收測(cè)試時(shí),無(wú)論是芯片還是 CEM,通常需要進(jìn)行鏈路訓(xùn)練進(jìn)入loopback,才能完成誤碼率測(cè)試。能 否支持更高速率切換、能否支持對(duì)噪聲敏感的NRZ/PAM4格式切換都是挑戰(zhàn),另外是否支持SSC和FEC解碼 挑戰(zhàn)更大。為消除環(huán)回channel對(duì)誤碼率影響,可以利用外置Redriver及內(nèi)部自適應(yīng)均衡配合實(shí)現(xiàn)。

圖8:PCIe 6.0芯片Rx測(cè)試

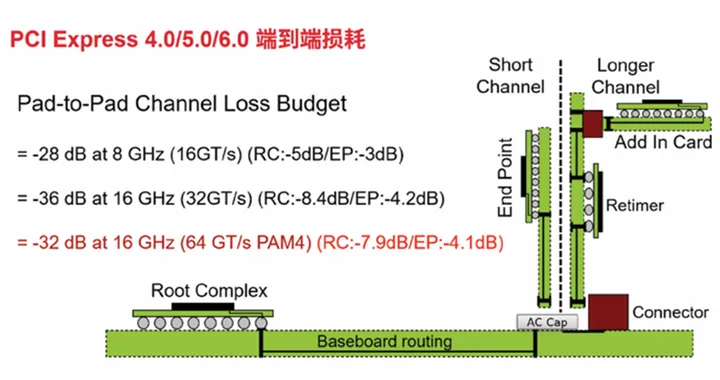

4)互連通道方面端到端鏈路包括封裝、PCB布線、連接器、過(guò)孔、耦合電容等,和PCIe 5.0相比有所變化,參考下圖,其一體現(xiàn)在端到端IL限制到了-32dB,其二體現(xiàn)在RC 的IL限制到了-7.9dB,EP的IL限制到-4.1dB,鏈路相關(guān)插損仍舊需要使用20GHz網(wǎng)分實(shí)現(xiàn)標(biāo)定。

圖9:PCIe 5.0/6.0 端到端損耗比較

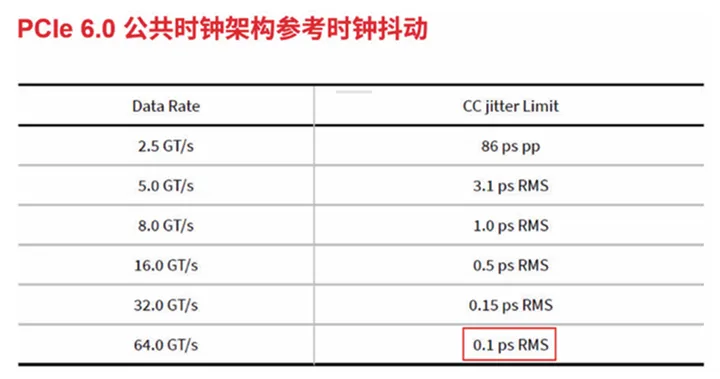

5)參考時(shí)鐘方面共時(shí)鐘架構(gòu)下PCIe 6.0參考時(shí)鐘抖動(dòng)在100fs(rms),相比PCIe 5.0參考時(shí)鐘抖動(dòng)limit下降了67%,這對(duì)測(cè)試測(cè)量帶來(lái)挑戰(zhàn),要求儀器固有抖動(dòng)不能太高。在信道仿真時(shí)考慮實(shí)際系統(tǒng)噪聲影響,抖動(dòng)limit可放寬至0.15ps(rms)。

圖10:參考時(shí)鐘抖動(dòng)要求

三、PCIe 6.0 測(cè)試方案

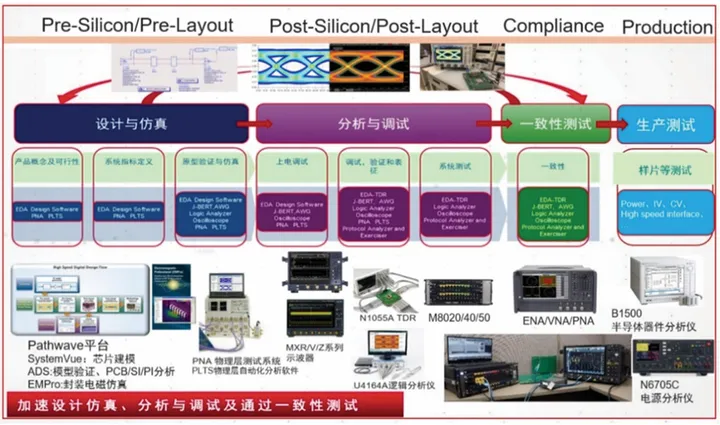

是德科技可以提芯片、板卡和產(chǎn)品的整體測(cè)試方案。包括仿真、調(diào)試和一致性測(cè)試等。

圖11:整體測(cè)試方案

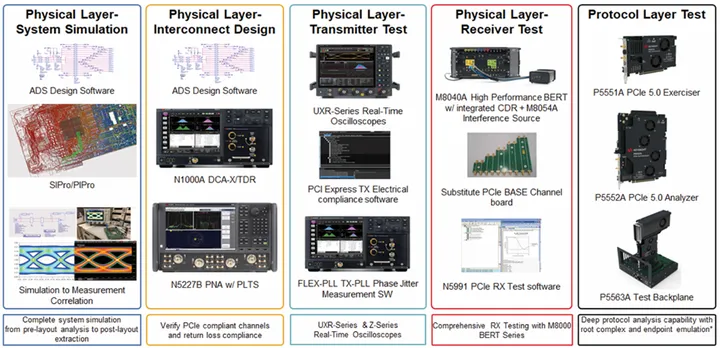

1) 物理層方面

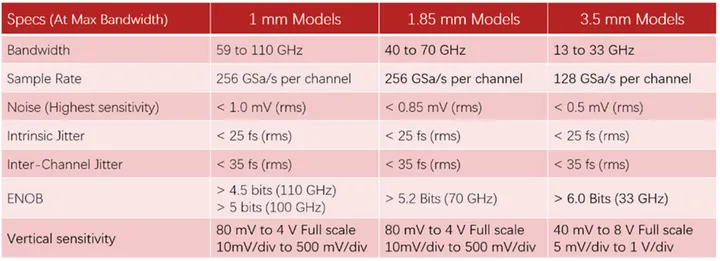

參考PCIe 6.0 Base spec v1.0,要求使用 33GHz 帶 寬( Bessel濾波器)進(jìn)行發(fā)送一致性測(cè)試, 等效最大平坦度 響應(yīng)帶寬是50GHz,這里推薦UXR0504A示波器。UXR系列示波器集成了InP材料HB2C工藝實(shí)現(xiàn)的前置放 大 器( 可達(dá) 110GHz)、 10 bit 高性能ADC和硬件加速功能的ASIC芯片,實(shí)現(xiàn)了4通帶全帶寬。通過(guò)工藝、芯 片和封裝技術(shù)使得UXR具備低本底噪聲、低固有抖動(dòng)/通道間抖動(dòng)和高耐壓。它無(wú)需外接衰減器就可以實(shí)現(xiàn) PCIe 6.0 serdes 信號(hào)高保真度測(cè)試。

圖12:UXR示波器主要型號(hào)和參數(shù)

2)協(xié)議層方面

芯片回片或板卡回板后完成bring up,除物理電氣子層測(cè)試還外,還需驗(yàn)證邏輯子層LTSSM鏈路狀態(tài)機(jī)以及數(shù)據(jù) 鏈 路 層 、事 務(wù) 層 等 業(yè) 務(wù) 是 否 正 常 及 合 規(guī) 性 ,那 么 還 需 要 借 助 協(xié) 議 分 析 儀 或 訓(xùn) 練 器 。當(dāng) 前 已 經(jīng) 發(fā) 布 了 支 持 PCIe 5.0的P5551A和P5552A的訓(xùn)練器和分析儀產(chǎn)品,支持不同link寬度,該產(chǎn)品集成interposer采集和數(shù)據(jù)處理功能于一體,無(wú)需一堆外部長(zhǎng)線纜將信號(hào)傳給主機(jī)處理,保證了信號(hào)完整性。分析儀注重協(xié)議解析、鏈路監(jiān)控及數(shù)據(jù)過(guò)濾等,訓(xùn)練器重點(diǎn)在于模擬對(duì)端EP或RC完成數(shù)據(jù)通信、支持注錯(cuò)和重播等,未來(lái)有計(jì)劃通過(guò)升級(jí)支持PCIe 6.0、CXL、NVMe等協(xié)議。

總之,是德科技可以提供基于ADS仿真、PLTS信號(hào)測(cè)量、物理層收發(fā)、插卡環(huán)路帶寬分析及協(xié)議分析等綜合解決方案。

圖13:PCIe 6.0 仿真、互連、物理層一致性和協(xié)議分析方案

文章來(lái)源:是德科技

審核編輯 黃宇

-

AI

+關(guān)注

關(guān)注

88文章

34405瀏覽量

275670 -

是德科技

+關(guān)注

關(guān)注

21文章

986瀏覽量

83283 -

PCIe5.0

+關(guān)注

關(guān)注

0文章

29瀏覽量

1619 -

大模型

+關(guān)注

關(guān)注

2文章

3045瀏覽量

3856

發(fā)布評(píng)論請(qǐng)先 登錄

PCIe 5.0市場(chǎng)加速滲透,PCIe 6.0研發(fā)到來(lái)

【極速存儲(chǔ)新選擇】PCIe5.0 M.2硬盤盒 免工具安裝全金屬抽取盒

Kioxia、AIO Core和Kyocera宣布開發(fā)適用于下一代綠色數(shù)據(jù)中心的支持PCIe 5.0的寬帶光固態(tài)硬盤

核芯互聯(lián)推出面向PCIe 5.0/6.0的32/64Gbps高速重驅(qū)動(dòng)器芯片CLH3264R

有獎(jiǎng)直播 | 3/13 群聯(lián)高速 IC redriver / retimer 發(fā)展計(jì)劃 (GEN6)

是德科技PCIe 6.0發(fā)射機(jī)合規(guī)性測(cè)試解決方案

PCIe 6.0時(shí)代的測(cè)試挑戰(zhàn)和解決方案

納米壓印技術(shù):開創(chuàng)下一代光刻的新篇章

下一代主流SiC IGBT模塊封裝技術(shù)研發(fā)趨勢(shì)——環(huán)氧灌封技術(shù)

下一代機(jī)器人技術(shù):工業(yè)自動(dòng)化的五大趨勢(shì)

PCIe 5.0 SerDes 測(cè)試

IaaS+on+DPU(IoD)+下一代高性能算力底座技術(shù)白皮書

DS320PR410支持PCIe5.0、CXL 2.0的四通道線性轉(zhuǎn)接驅(qū)動(dòng)器數(shù)據(jù)表

24芯M16插頭在下一代技術(shù)中的潛力

下一代PCIe5.0 /6.0技術(shù)熱潮趨勢(shì)與測(cè)試挑戰(zhàn)

下一代PCIe5.0 /6.0技術(shù)熱潮趨勢(shì)與測(cè)試挑戰(zhàn)

評(píng)論