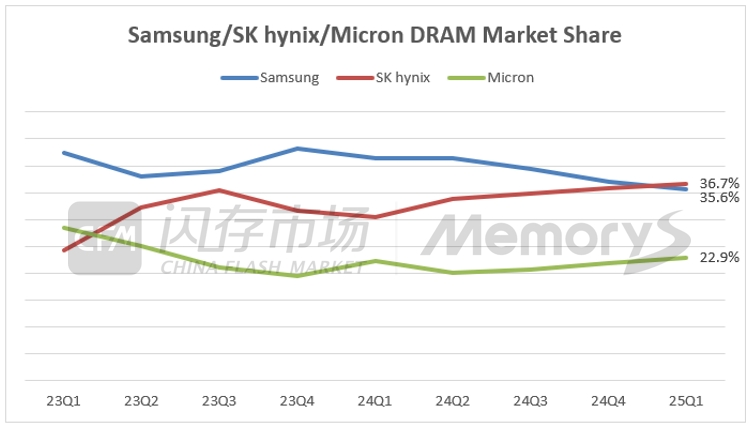

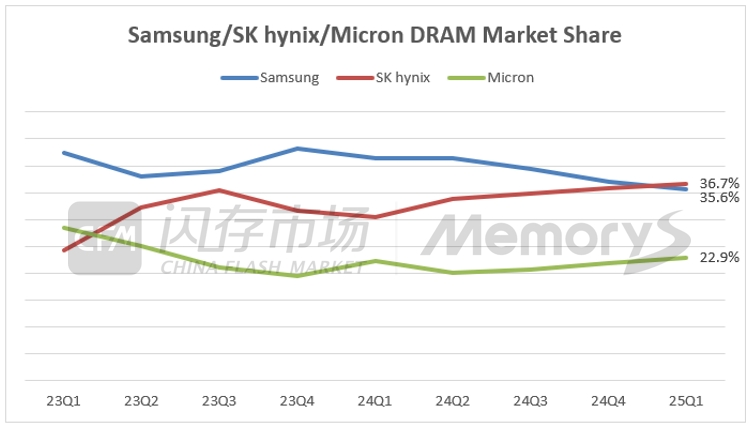

增長42.5%至267.29億美元,環(huán)比減少8.5%。 ? 然而不可忽視的是,在2025年一季度,SK海力士憑借在HBM領(lǐng)域的絕對優(yōu)勢,終結(jié)三星長達四十多年的市場統(tǒng)治地位,以36.7%的市場份額首度登頂全球

![的頭像]() 發(fā)表于

發(fā)表于 05-06 15:50

?486次閱讀

三星電子在 HBM3 時期遭遇了重大挫折,將 70% 的 HBM 內(nèi)存市場份額拱手送給主要競爭對手 SK 海力士,更是近年來首度讓出了第一大 DRAM 原廠的寶座。這迫使

發(fā)表于 04-18 10:52

3月20日,以“AI科技、AI生活”為主題的2025年中國家電及消費電子博覽會(AWE 2025)在上海新國際博覽中心開幕。作為消費

![的頭像]() 發(fā)表于

發(fā)表于 03-21 15:25

?614次閱讀

南極熊導(dǎo)讀:中國金屬3D打印廠商已經(jīng)在全球占據(jù)重要的組成部分。國外行業(yè)大咖如何看待2025年金屬3D打印行業(yè)的趨勢與挑戰(zhàn)?

![的頭像]() 發(fā)表于

發(fā)表于 03-14 09:59

?690次閱讀

DRAM內(nèi)存產(chǎn)品面臨的良率和性能雙重挑戰(zhàn),已決定在2024年底對現(xiàn)有的1b nm工藝進行改進,并從頭開始設(shè)計新版1b nm DRAM。然而,三星電子

![的頭像]() 發(fā)表于

發(fā)表于 01-23 15:05

?592次閱讀

近日,三星電子宣布了一項重大決策,將大幅削減其晶圓代工部門在2025年的設(shè)施投資。據(jù)透露,與上一年相比,此次削減幅度將超過一半。 具體來說,

![的頭像]() 發(fā)表于

發(fā)表于 01-23 14:36

?511次閱讀

近日,據(jù)最新報道,三星計劃在2025年大幅削減其晶圓代工部門的投資規(guī)模,設(shè)備投資預(yù)算將從2024年的10萬億韓元銳減至5萬億韓元,削減幅度高達50%。 此次投資削減主要集中在韓國的兩大

![的頭像]() 發(fā)表于

發(fā)表于 01-23 11:32

?628次閱讀

問題,在2024年底決定在改進現(xiàn)有1b nm工藝的同時,從頭設(shè)計新版1b nm DRAM。 不過,三星通過相關(guān)媒體表示相關(guān)報道不準確。盡管三星否認了重新設(shè)計,但有業(yè)內(nèi)人士透露,

![的頭像]() 發(fā)表于

發(fā)表于 01-23 10:04

?980次閱讀

據(jù)韓媒MoneyToday報道,三星電子已將其1c nm(1-cyano nanometer)DRAM內(nèi)存開發(fā)的良率里程碑時間從原定的2024年底推遲至

![的頭像]() 發(fā)表于

發(fā)表于 01-22 14:27

?644次閱讀

近日,據(jù)韓媒最新報道,三星電子在面對其12nm級DRAM內(nèi)存產(chǎn)品的良率和性能雙重困境時,已于2024年底作出了重要決策。為了改善現(xiàn)狀,三星決

![的頭像]() 發(fā)表于

發(fā)表于 01-22 14:04

?870次閱讀

近日,韓媒The Elec發(fā)布了一篇博文,披露了三星在智能手機領(lǐng)域的一項新動向。據(jù)該報道,三星計劃在2025年第2季度正式量產(chǎn)其首款三折疊手

![的頭像]() 發(fā)表于

發(fā)表于 01-15 15:42

?836次閱讀

三星電子近日宣布了2025年度的重大組織與高管調(diào)整計劃。其中,存儲器業(yè)務(wù)將被調(diào)整為CEO直轄部門,這一調(diào)整意味著存儲器業(yè)務(wù)在三星

![的頭像]() 發(fā)表于

發(fā)表于 12-03 12:50

?738次閱讀

三星電子近日宣布了2025年度的重大組織與高管結(jié)構(gòu)調(diào)整計劃,以進一步推動公司的戰(zhàn)略轉(zhuǎn)型和業(yè)務(wù)發(fā)展。 其中,存儲器業(yè)務(wù)將調(diào)整為CEO直轄部門,

![的頭像]() 發(fā)表于

發(fā)表于 11-29 14:36

?1608次閱讀

近日,業(yè)界傳出三星電子HBM3E商業(yè)化進程遲緩的消息,據(jù)稱這一狀況或與HBM核心芯片DRAM有關(guān)。具體而言,1a DRAM的性能問題成為了

![的頭像]() 發(fā)表于

發(fā)表于 10-23 17:15

?936次閱讀

三星推出了業(yè)內(nèi)首款24Gb(即3GB)GDDR7 DRAM內(nèi)存芯片,其超高速度可達42.5Gbps,專為下一代圖形處理單元(GPU)打造。據(jù)三星介紹,得益于多項改進與更新,該芯片相比前

![的頭像]() 發(fā)表于

發(fā)表于 10-22 15:13

?2094次閱讀

三星電子:2025年步入3D DRAM時代

三星電子:2025年步入3D DRAM時代

評論