本文介紹了集成電路制造工藝中的偽柵去除技術(shù),分別討論了高介電常數(shù)柵極工藝、先柵極工藝和后柵極工藝對比,并詳解了偽柵去除工藝。

高介電常數(shù)金屬柵極工藝

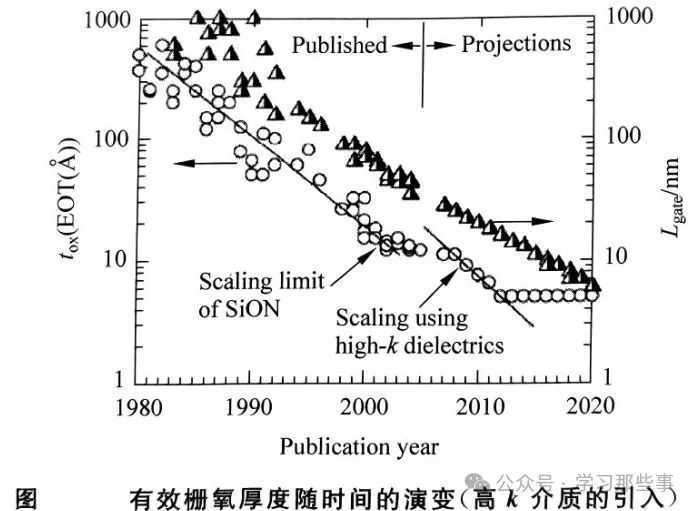

隨著CMOS集成電路特征尺寸的持續(xù)縮小,等效柵氧厚度成為影響晶體管性能的關(guān)鍵因素。然而,柵氧厚度的減小極限受到隧穿漏電效應(yīng)的限制,當氧化硅層薄至2nm以下時,隧穿漏電現(xiàn)象變得顯著,且隨厚度減小呈指數(shù)級增長,使得1nm以下的柵氧厚度變得不切實際。

為了克服這一挑戰(zhàn),英特爾公司在45nm節(jié)點引入了高k技術(shù),其他公司則在32nm或28nm節(jié)點跟進。

高介電常數(shù)柵介電層技術(shù)(HK)與金屬柵極技術(shù)(MG)的結(jié)合成為當前邏輯電路的主流趨勢。盡管兩者本無必然聯(lián)系,但高k柵介電層帶來的高電場強度要求柵極材料具有更好的導(dǎo)電性和穩(wěn)定性,因此金屬柵極成為理想選擇。金屬柵極可以顯著減小柵極耗盡效應(yīng),提升晶體管性能。

先柵極工藝和后柵極工藝對比

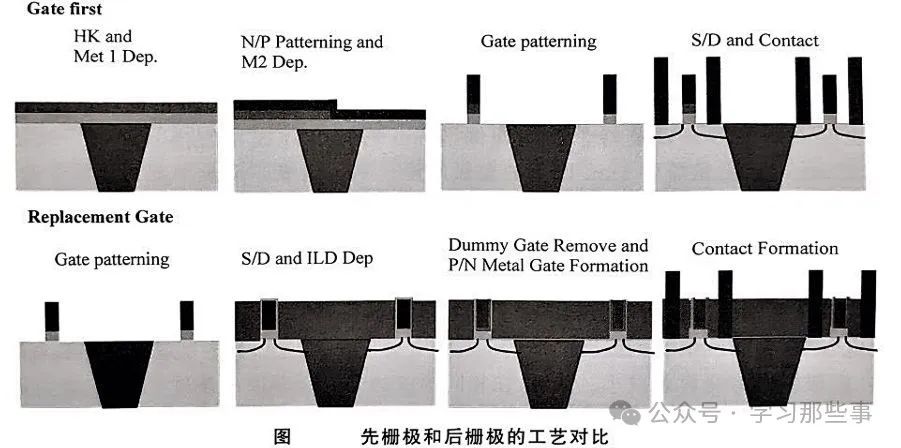

在CMOS集成電路制造中,“硅柵自對準”工藝占據(jù)主導(dǎo)地位。該工藝首先形成柵介電層和柵極(通常為多晶硅),然后進行源極和漏極的離子摻雜。由于柵極結(jié)構(gòu)的阻擋作用,離子摻雜自動與硅柵對準。后續(xù)的高溫退火工藝用于激活摻雜離子。

然而,金屬柵極在“硅柵自對準”工藝中面臨諸多挑戰(zhàn),如閾值電壓變化等。為解決這些問題,業(yè)界采用了多晶硅偽柵技術(shù)。

在離子摻雜和退火等關(guān)鍵步驟完成后,通過化學氣相生長填充氧化硅膜,并采用化學機械研磨工藝進行平坦化,使偽柵暴露出來。隨后,去除多晶硅偽柵,并使用功函數(shù)金屬和柵極金屬填充形成金屬柵。這一過程被稱為后柵極工藝流程。

后柵極工藝流程增加了偽柵去除和金屬填充等核心步驟。偽柵去除工藝要求在不損傷溝道的情況下完全去除偽柵材料。而金屬填充則面臨高深寬比的挑戰(zhàn),需要采用先進的填充技術(shù)和材料以確保金屬柵的完整性和可靠性。

盡管后柵極工藝成本較高且工藝復(fù)雜,但長期以來被認為是實現(xiàn)高介電常數(shù)柵介電層與金屬柵極(HKMG)結(jié)合的必要方案。然而,隨著技術(shù)的不斷進步,一些公司(如IBM)正在研發(fā)無需后柵極工藝的替代方案。例如,通過采用特定的介電材料(如硅酸鉿)和柵極材料匹配,可以在高溫下保持熱動力學穩(wěn)定,從而簡化工藝流程并降低成本。

此外,先柵極工藝也在不斷發(fā)展中。盡管先柵極工藝中的“金屬柵”實際上只是在柵介電層上增加了一層高熔點金屬,但仍需要多晶硅柵極來實現(xiàn)“硅柵自對準”的其他工序。隨著材料科學和工藝技術(shù)的不斷進步,未來可能會有更多創(chuàng)新的解決方案出現(xiàn),以進一步簡化CMOS集成電路的制造工藝并提升性能。

偽柵去除工藝詳解

在CMOS集成電路的后柵極工藝中,偽柵去除是一個至關(guān)重要的步驟。目前,業(yè)界主要采用三種偽柵去除工藝:濕法蝕刻、干法結(jié)合濕法蝕刻以及純干法蝕刻。

1、濕法蝕刻工藝

濕法蝕刻通常使用四甲基氫氧化銨等化學溶液來去除多晶硅偽柵。這種方法能夠避免干法蝕刻可能帶來的等離子體損傷。然而,由于離子注入過程中部分摻雜離子不可避免地會進入偽柵上半部分,導(dǎo)致濕法蝕刻率對摻雜多晶硅非常敏感。特別是當偽柵中摻雜了硼元素時,四甲基氫氧化銨在其上的蝕刻率會大幅降低,從而限制了濕法蝕刻的單獨使用。

2、干法結(jié)合濕法蝕刻工藝

為了克服濕法蝕刻和干法蝕刻各自的局限性,業(yè)界開發(fā)了干法結(jié)合濕法蝕刻的工藝。該工藝首先使用干法蝕刻去除偽柵上部的摻雜多晶硅層,以減少濕法蝕刻時的敏感性和不均勻性。隨后,采用濕法蝕刻去除剩余的未摻雜多晶硅。這種方法結(jié)合了干法和濕法的優(yōu)點,既避免了等離子體損傷,又提高了蝕刻的均勻性和可控性。然而,由于濕法蝕刻的各向同性特性,這種方法通常只適用于同時去除N型和P型偽柵。在后續(xù)的功函數(shù)金屬填充工藝中,仍需要重新定義圖形并去除不需要的功函數(shù)金屬,因此整體工藝流程并未得到顯著簡化。

3、純干法蝕刻工藝

純干法蝕刻工藝是一種更為先進和靈活的偽柵去除方法。該工藝首先去除偽柵表面覆蓋的原生氧化硅層,通常采用碳氟氣體進行蝕刻。在去除原生氧化硅的同時,盡量減少蝕刻表面副產(chǎn)物的殘留。接下來的偽柵主蝕刻步驟則采用HBr與O2的混合氣體,在電感耦合蝕刻反應(yīng)腔體中進行。硅與溴反應(yīng)形成弱揮發(fā)性的溴化硅副產(chǎn)物,從而實現(xiàn)較高的多晶硅對氧化硅的選擇比。在去除偽柵多晶硅的同時,蝕刻會停止在高介電常數(shù)柵氧化層的保護層上,且對層間介質(zhì)層的損傷較小。

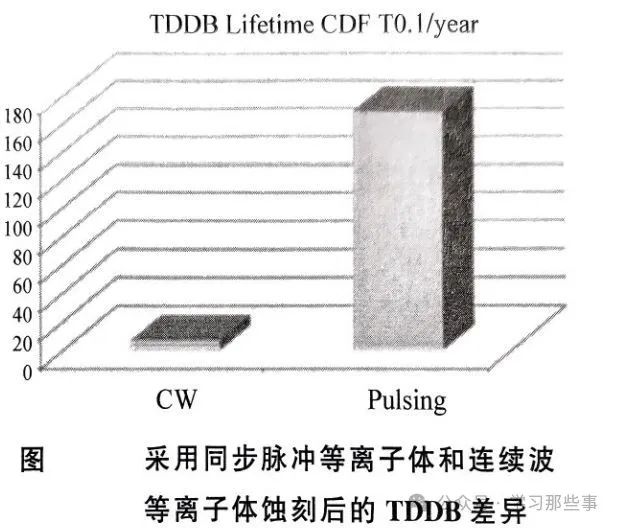

為了進一步提高純干法蝕刻的效率和可控性,業(yè)界引入了同步脈沖等離子體工藝。

該工藝通過控制等離子體的開關(guān)時間和占空比,降低等離子體中的電子溫度,從而減輕高能粒子注入溝道區(qū)所帶來的風險。同步脈沖等離子體蝕刻能夠減少HBr的過度解離,降低等離子體中的氫離子濃度,進而減少被電場加速注入溝道的氫離子數(shù)量。這不僅提高了偽柵去除的均勻性和可控性,還有效改善了NBTI(負偏置溫度不穩(wěn)定性)等可靠性問題。

在偽柵去除工藝中,物理性能的考慮對于確保工藝的高效性和器件的可靠性至關(guān)重要。其中,鍵能差異和電子溫度對蝕刻過程有著顯著影響。

1、鍵能差異與蝕刻選擇比

由于Si-O鍵的鍵能(460kJ/mol-1)遠高于Si-Si鍵的鍵能(176kJ/mol-1),這導(dǎo)致在蝕刻過程中,氧化硅層相對于多晶硅層具有更高的穩(wěn)定性。極低的電子溫度,如同步脈沖偽柵去除蝕刻工藝所提供的,能夠顯著降低對氧化硅層間介電層的蝕刻率。這種降低的蝕刻率使得偽柵和層間介電層之間的蝕刻選擇比上升,有助于在去除偽柵的同時保護層間介電層不受損傷。

2、層間介電層消耗與金屬柵高度

同步脈沖蝕刻工藝的優(yōu)勢在于,它能夠在蝕刻過程中顯著減少層間介電層的消耗。通過優(yōu)化蝕刻條件,層間介電層的消耗從50?減少到20?。這種減少的消耗將明顯提高金屬柵的高度,進而降低金屬柵的電阻。這對于提高器件的性能和可靠性至關(guān)重要。

3、蝕刻氣體的選擇

在偽柵去除工藝中,蝕刻氣體的選擇同樣是一個關(guān)鍵因素。傳統(tǒng)的HBr氣體在與多晶硅柵反應(yīng)時,會形成難以揮發(fā)的副產(chǎn)物,這增加了去除的難度。為了達到去除的目的,通常需要增加偏置功率,但這可能導(dǎo)致離子轟擊增強,對器件造成損傷。為了克服這一問題,業(yè)界開始探索使用氫氣作為蝕刻氣體。

氫氣分子在源功率的作用下解離為氫原子,這些氫原子與硅反應(yīng)形成硅烷(SiH?)。硅烷具有較低的沸點,因此其氣化性遠大于溴化硅(SiBr?)。這意味著在蝕刻過程中,硅烷副產(chǎn)物更容易被去除,無需使用偏置功率即可達到清潔的蝕刻表面。實驗證明,采用無偏置功率氫氣等離子體的偽柵去除工藝對偽柵底部的高k材料保護層具有更高的選擇比和更少的損傷。從器件性能角度看,這種工藝能夠大幅降低金屬柵極漏電,相比其他工藝可降低50%。

-

集成電路

+關(guān)注

關(guān)注

5420文章

11983瀏覽量

367502 -

CMOS

+關(guān)注

關(guān)注

58文章

5999瀏覽量

238280 -

制造工藝

+關(guān)注

關(guān)注

2文章

202瀏覽量

20294

原文標題:偽柵去除技術(shù)

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

中國集成電路大全 接口集成電路

最全最詳盡的半導(dǎo)體制造技術(shù)資料,涵蓋晶圓工藝到后端封測

集成電路外延片詳解:構(gòu)成、工藝與應(yīng)用的全方位剖析

集成電路工藝學習之路:從零基礎(chǔ)到專業(yè)水平的蛻變

探秘集成電路制造的“高精尖”:三束技術(shù)全景解析

集成電路制造工藝中的偽柵去除技術(shù)介紹

集成電路制造工藝中的偽柵去除技術(shù)介紹

評論