OTGHS介紹

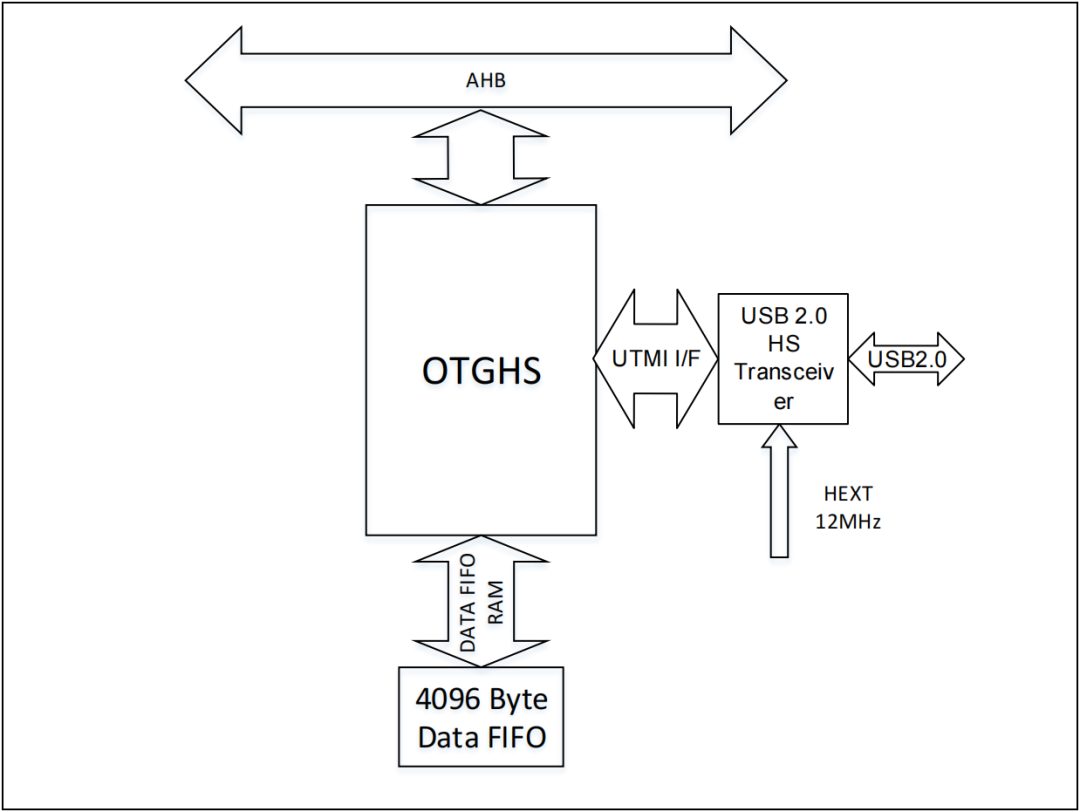

本章將描述OTGHS支持的一些基本功能。圖1.OTGHS框圖

OTGHS特性

OTGHS通用特性:

- 支持USB2.0協(xié)議

- 內(nèi)置獨(dú)立4096字節(jié)SRAM

- 內(nèi)置USB2.0高速PHY

- 內(nèi)置上下拉電阻

- SOF信號(hào)輸出

- 低功耗模式

- 支持忽略VBUS狀態(tài)

- 支持ID檢測(cè)以切換主機(jī)設(shè)備模式

- 不支持HNP/SRP協(xié)議(PHY不支持,不能動(dòng)態(tài)切換模式,只能根據(jù)ID狀態(tài)切換模式)

- AHB時(shí)鐘大于30MHz

OTGHS設(shè)備模式特性:

- 支持高速和全速設(shè)備

- 支持內(nèi)部1.5KΩ上拉

- 支持軟件斷開連接

- 支持1個(gè)雙向控制端點(diǎn)0

- 支持7個(gè)IN端點(diǎn),端點(diǎn)號(hào)1-7

- 支持7個(gè)OUT端點(diǎn),端點(diǎn)號(hào)1-7

- 支持控制傳輸,大容量傳輸,中斷傳輸,同步傳輸

- 端點(diǎn)接收FIFO共享

- 端點(diǎn)發(fā)送FIFO專用

- 支持內(nèi)部DMA模式

OTGHS主機(jī)模式特性:

- 支持高速、全速和低速

- 支持內(nèi)部15KΩ下拉

- 支持16個(gè)主機(jī)通道

- 支持控制傳輸,大容量傳輸,中斷傳輸,同步傳輸

- 通道接收FIFO共享

- 通道發(fā)送FIFO專用

- 支持內(nèi)部DMA模式

OTGHS高速PHY

OTGHS內(nèi)置PHY支持高速/全速/低速,為主機(jī)和設(shè)備模式提供通信支持。

- DP和DM內(nèi)置上下拉電阻,由OTGHS根據(jù)模式自動(dòng)使能上下拉電阻當(dāng)OTGHS處于設(shè)備模式時(shí),DP1.5KΩ上拉自動(dòng)使能當(dāng)OTGHS處于主機(jī)模式時(shí),DP和DM 15KΩ下拉自動(dòng)使能

- ID線內(nèi)置上拉ID線為高電平,默認(rèn)為設(shè)備模式ID線為低電平,為主機(jī)模式

- 設(shè)備模式下的VBUS檢測(cè)(可忽略VBUS檢測(cè))設(shè)備模式下,僅支持VBUS高低電平檢測(cè),當(dāng)VBUS為高電平,OTGHS認(rèn)為是有效電平,將使能DP的上拉電阻,讓主機(jī)識(shí)別到設(shè)備插入。當(dāng)VBUS為低電平,OTGHS認(rèn)為是無效電平,此時(shí)不使能DP上拉,處于斷開模式。在設(shè)備模式下,如果想不檢測(cè)VBUS,可通過設(shè)置寄存器OTGHS_GCCFG.VBUSIG=1來實(shí)現(xiàn),此時(shí)可將檢測(cè)VBUS的引腳釋放出來給其它外設(shè)使用。

- PHY的低功耗模式OTGHS全速PHY支持低功耗模式。

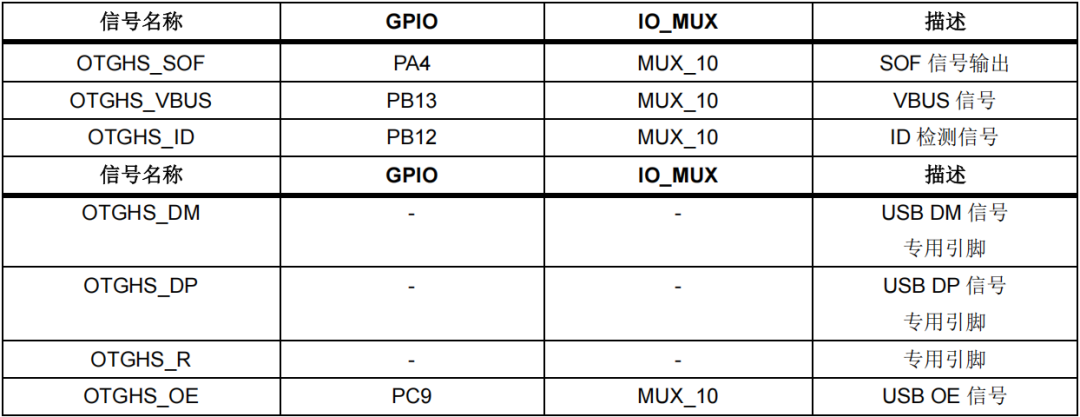

OTGHS GPIO引腳

OTGHS使用GPIO引腳如下表所示:表1 OTGHS GPIO引腳 注:USB_OE信號(hào)當(dāng)USB在傳輸數(shù)據(jù)時(shí),會(huì)翻轉(zhuǎn)此信號(hào)

注:USB_OE信號(hào)當(dāng)USB在傳輸數(shù)據(jù)時(shí),會(huì)翻轉(zhuǎn)此信號(hào)

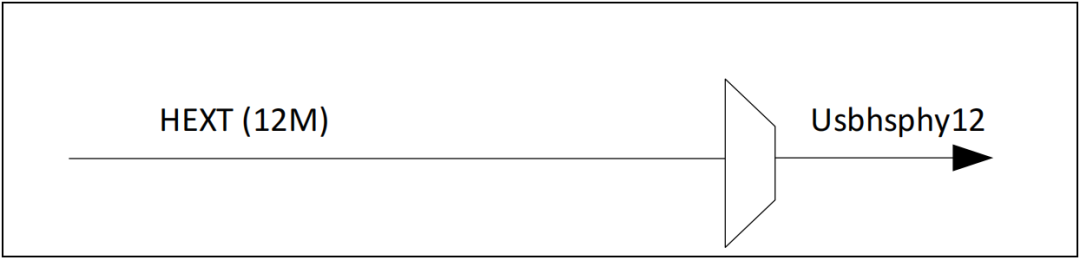

OTGHS 12MHz時(shí)鐘

需要給OTGHS PHY提供12MHz的時(shí)鐘,建議直接掛12MHz晶振,由晶振直接提供12MHz時(shí)鐘給PHY。圖2.OTGHS 12MHz時(shí)鐘來源

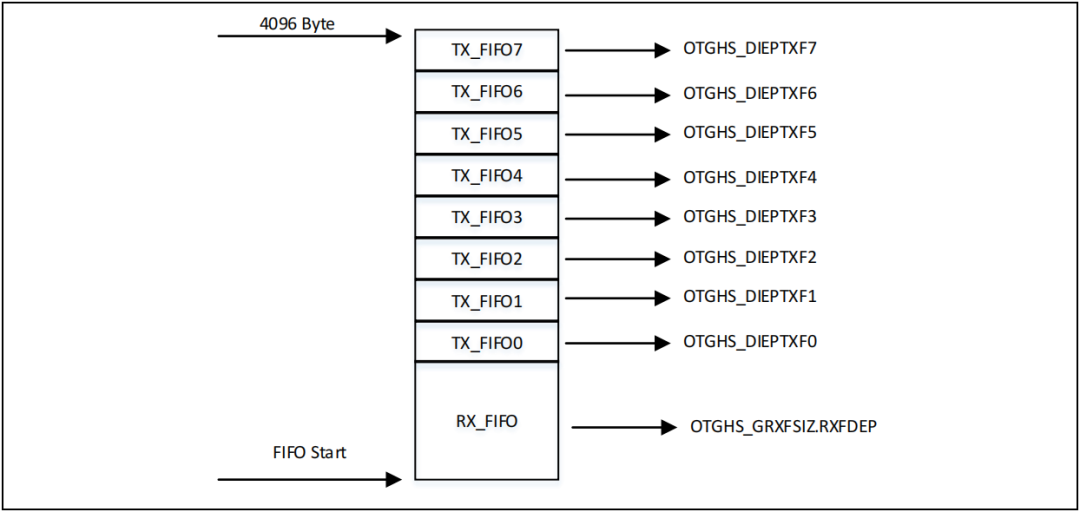

OTGHS數(shù)據(jù)FIFO管理

OTGHS分配專用的4096 Byte SRAM作為數(shù)據(jù)FIFO,在主機(jī)或設(shè)備模式下,可通過軟件配置寄存器給端點(diǎn)/通道分配FIFO,同時(shí)可以使用OTG內(nèi)部DMA實(shí)現(xiàn)用戶SRAM與FIFO的數(shù)據(jù)交換。注意:分配的FIFO總大小不要超過4096 Byte

一、設(shè)備模式下的FIFO分配設(shè)備模式下所有端點(diǎn)的接收共享一個(gè)接收FIFO,每個(gè)端點(diǎn)的發(fā)送對(duì)應(yīng)一個(gè)專有的發(fā)送FIFO。圖3 設(shè)備模式FIFO分配

- RX_FIFO所有端點(diǎn)的接收共享這一塊FIFO,配置寄存器OTGHS_GRXFSIZ.RXFDEP,此寄存器值表示接收FIFO大小,注意單位為word(4Byte)。

- TX_FIFO0端點(diǎn)0的發(fā)送FIFO,配置寄存器OTGHS_DIEPTXF0,需要配置起始地址和FIFO大小。OTGHS_DIEPTXF0. INEPT0TXSTADDR=OTGFS_GRXFSIZ.RXFDEPOTGHS_DIEPTXF0. INEPT0TXDEP=端點(diǎn)0發(fā)送FIFO大小

- TX_FIFO1端點(diǎn)1的發(fā)送FIFO,配置寄存器OTGFS_DIEPTXF1,需要配置起始地址和FIFO大小。OTGHS_DIEPTXF1.INEPTXFSTADDR=OTGHS_GRXFSIZ.RXFDEP+端點(diǎn)0發(fā)送FIFO大小OTGHS_DIEPTXF1.INEPTXFDEP=端點(diǎn)1發(fā)送FIFO大小….

注意:對(duì)應(yīng)端點(diǎn)FIFO配置寄存器中FIFO大小值的單位都是word(4Byte)。注意:發(fā)送端點(diǎn)的起始地址一般配置為前面所有端點(diǎn)已占用的FIFO大小,例程如端點(diǎn)2的發(fā)送FIFO起始地址為RX_FIFO大小+TX_FIFO0大小+TX_FIFO1大小。

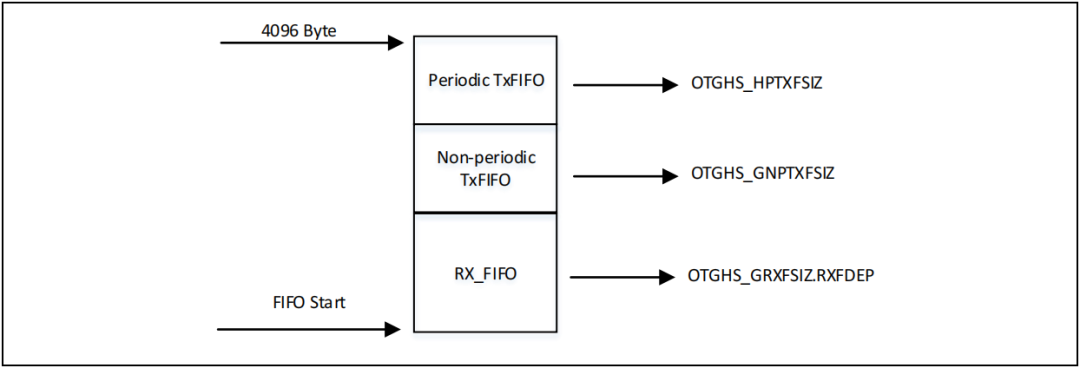

二、主機(jī)模式下的FIFO分配主機(jī)模式下,所有通道共享一個(gè)接收FIFO,通道發(fā)送FIFO分為非周期性發(fā)送FIFO和周期性發(fā)送FIFO。非周期性和周期性通過傳輸類型來區(qū)分,每個(gè)主機(jī)通道寄存器都有配置傳輸類型,包含4種傳輸類型:控制傳輸(Control),同步傳輸(ISO),批量傳輸(Bulk),中斷傳輸(Interrupt)

- 非周期性:控制傳輸(Control),批量傳輸(Bulk)

- 周期性傳輸:同步傳輸(ISO),中斷傳輸(Interrupt)

圖4 主機(jī)模式下FIFO分配

- RX_FIFO所有主機(jī)通道的接收共享這一塊FIFO,配置寄存器OTGHS_GRXFSIZ.RXFDEP,此寄存器值表示接收FIFO大小,注意單位為word(4Byte)。

- Non-periodic TxFIFO非周期性的主機(jī)通道發(fā)送FIFO,配置寄存器OTGHS_GNPTXFSIZ,需要配置起始地址和FIFO大小。OTGHS_GNPTXFSIZ. NPTXFSTADDR=OTGHS_GRXFSIZ.RXFDEPOTGHS_GNPTXFSIZ. NPTXFDEP=非周期性發(fā)送FIFO大小

- Periodic_TxFIFO周期性的主機(jī)通道發(fā)送FIFO,配置寄存器OTGHS_HPTXFSIZ,需要配置起始地址和FIFO大小。OTGHS_HPTXFSIZ.PTXFSTADDR=OTGHS_GRXFSIZ.RXFDEP+OTGFS_GNPTXFSIZ.NPTXFDEPOTGHS_HPTXFSIZ. PTXFSIZE=周期性發(fā)送FIFO大小

注意:對(duì)應(yīng)FIFO配置寄存器中FIFO大小值的單位都是word(4Byte)。

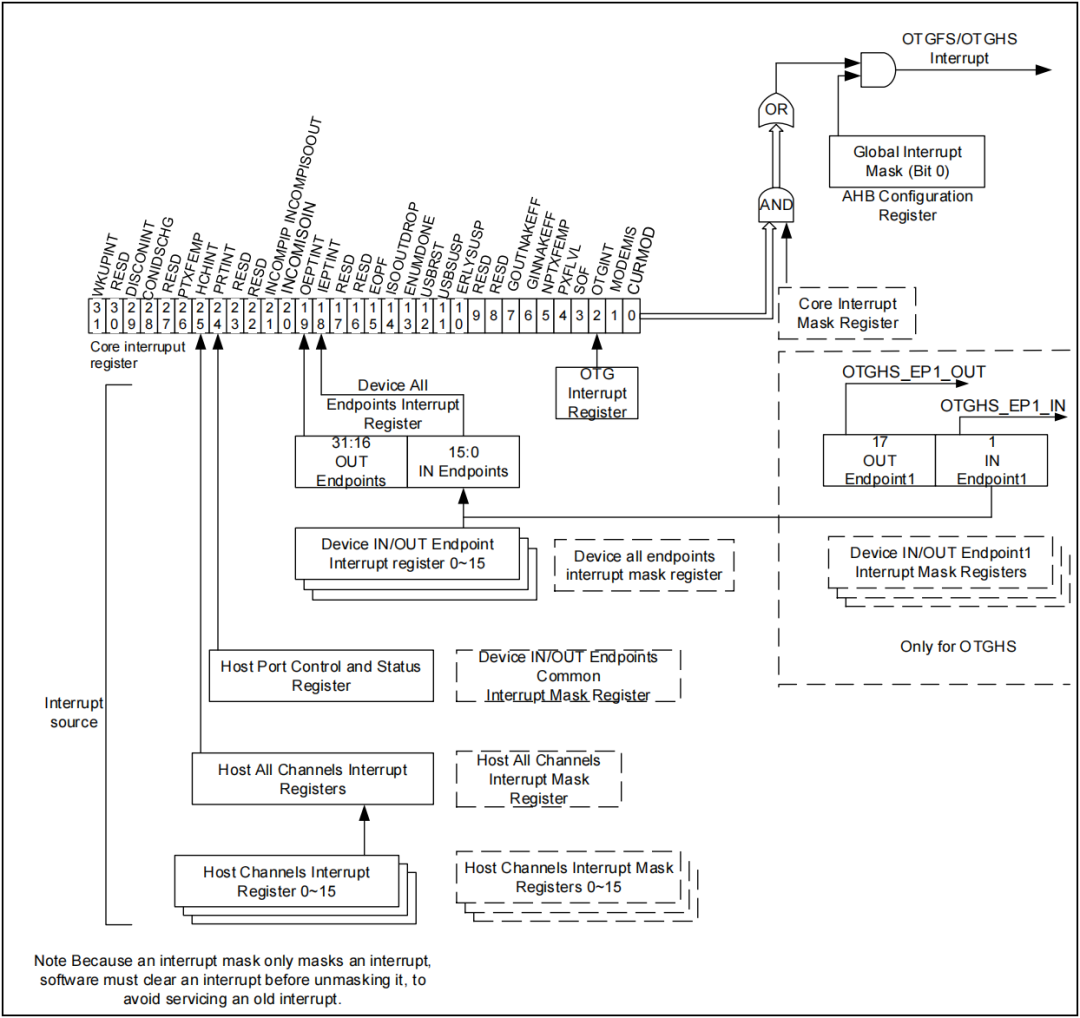

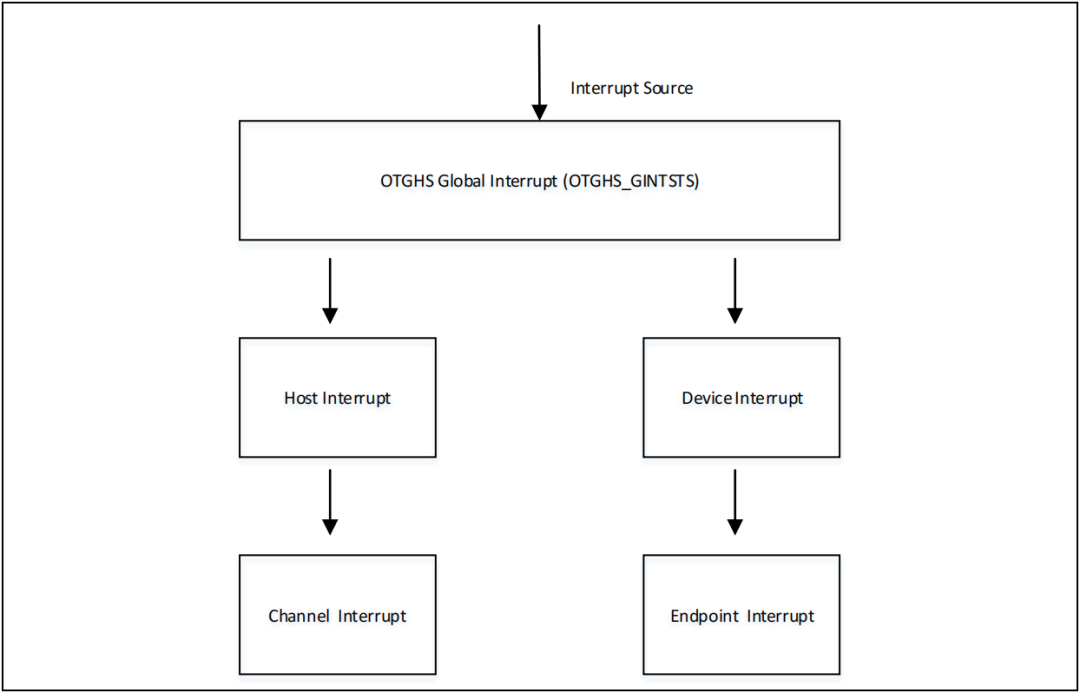

OTGHS中斷結(jié)構(gòu)

圖5.OTGHS中斷結(jié)構(gòu) 全局常用中斷OTGHS_GINTSTS,此寄存器中包含了主機(jī)和設(shè)備的中斷標(biāo)志,部分中斷標(biāo)志只在設(shè)備模式或者主機(jī)模式下有效。

全局常用中斷OTGHS_GINTSTS,此寄存器中包含了主機(jī)和設(shè)備的中斷標(biāo)志,部分中斷標(biāo)志只在設(shè)備模式或者主機(jī)模式下有效。

- 設(shè)備和主機(jī)模式都有效中斷標(biāo)志OTGHS_GINTSTS. MODEMIS:模式不匹配(主機(jī)和設(shè)備都適用)OTGHS_GINTSTS. SOF:SOF中斷(主機(jī)和設(shè)備都適用)OTGHS_GINTSTS.RXFLVL:接收FIFO非空(主機(jī)和設(shè)備都適用)OTGHS_GINTSTS. CONIDSCHG:ID線狀態(tài)變化(主機(jī)和設(shè)備都適用)OTGHS_GINTSTS.WKUPINT:?jiǎn)拘研盘?hào)中斷(主機(jī)和設(shè)備都適用)

- 僅主機(jī)模式下有效中斷標(biāo)志OTGHS_GINTSTS. NPTXFEMP:非周期發(fā)送FIFO為空(主機(jī)適用)OTGHS_GINTSTS. PRTINT:主機(jī)端口中斷(主機(jī)適用)OTGHS_GINTSTS. HCHINT:主機(jī)通道中斷(主機(jī)適用)OTGHS_GINTSTS. PTXFEMP:周期性發(fā)送FIFO為空(主機(jī)適用)OTGHS_GINTSTS. DISCONINT:設(shè)備斷開(主機(jī)適用)

- 僅設(shè)備模式下有效中斷標(biāo)志OTGHS_GINTSTS. USBSUSP:設(shè)備掛起(設(shè)備適用)OTGHS_GINTSTS. USBRST:USB復(fù)位(設(shè)備適用)OTGHS_GINTSTS. ENUMDONE:枚舉速度完成(設(shè)備適用)OTGHS_GINTSTS. ISOOUTDROP:同步OUT包丟失(設(shè)備適用)OTGHS_GINTSTS. IEPTINT:IN端點(diǎn)中斷(設(shè)備適用)OTGHS_GINTSTS. OEPTINT:OUT端點(diǎn)中斷(設(shè)備適用)OTGHS_GINTSTS. INCOMPISOIN:未完成的同步IN傳輸(設(shè)備適用)

圖6.中斷處理流程

OTG模式

通過配置如下寄存器讓OTGHS處于OTG模式:

- OTGHS_GUSBCFG.FDEVMODE=0(非強(qiáng)制設(shè)備模式)

- OTGHS_GUSBCFG.FHSTMODE=0(非強(qiáng)制主機(jī)模式)

OTGHS可以通過檢測(cè)ID線上的狀態(tài)來確定當(dāng)前處于設(shè)備模式還是主機(jī)模式。當(dāng)ID狀態(tài)為高電平時(shí)為設(shè)備模式,當(dāng)ID狀態(tài)為低電平時(shí)為主機(jī)模式。

寄存器GINTSTS.CURMOD=0,表示當(dāng)前為設(shè)備模式寄存器GINTSTS.CURMOD=1,表示當(dāng)前為主機(jī)模式另外可以根據(jù)GINTSTS. CONIDSCHG中斷來檢測(cè)當(dāng)前ID線的狀態(tài)是否有變化,當(dāng)檢測(cè)到ID線有變化時(shí),根據(jù)當(dāng)前的模式位(GINTSTS.CURMOD),應(yīng)用程序選擇初始化主機(jī)程序還是設(shè)備程序。圖7.OTG模式連接示意圖

設(shè)備模式

OTGHS作為設(shè)備時(shí)支持高速和全速設(shè)備,不支持低速設(shè)備。支持8個(gè)IN端點(diǎn)(包括端點(diǎn)0),8個(gè)OUT端點(diǎn)(包括端點(diǎn)0)。

OTGHS強(qiáng)制作為設(shè)備

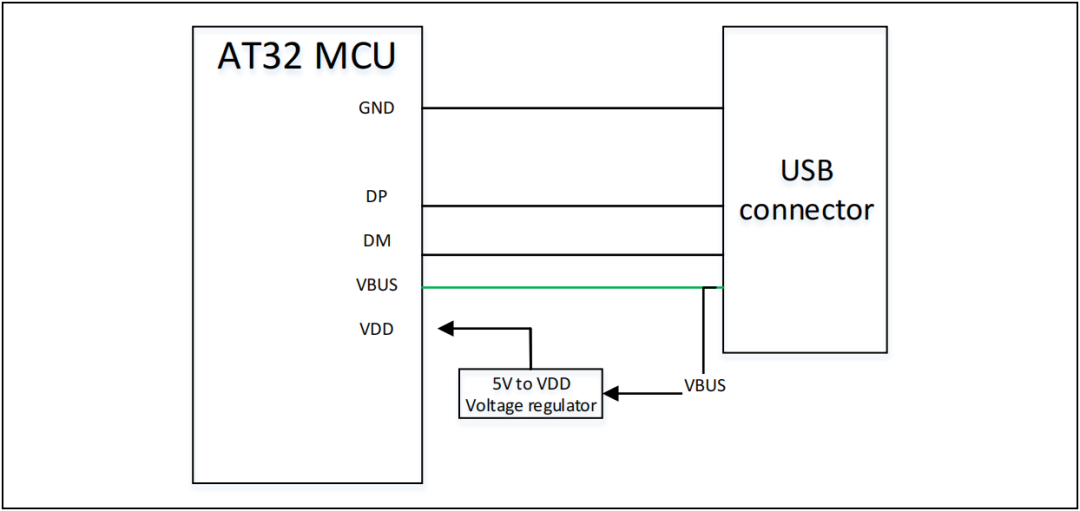

通過設(shè)定如下寄存器將OTGHS強(qiáng)制作為設(shè)備:OTGHS_GUSBCFG.FDEVMODE=1(強(qiáng)制設(shè)備模式)OTGHS_GUSBCFG.FHSTMODE=0(非強(qiáng)制主機(jī)模式)圖8.設(shè)備模式連接示意圖 注意:綠色線表示可選連接,當(dāng)使能VBUSIG信號(hào)時(shí),VBUS引腳可作為普通I/O。

注意:綠色線表示可選連接,當(dāng)使能VBUSIG信號(hào)時(shí),VBUS引腳可作為普通I/O。

OTGHS設(shè)備常用功能

本節(jié)介紹OTGHS作為設(shè)備模式時(shí)的一些功能。

- 軟件斷開可以通過配置設(shè)備模式下的寄存器,達(dá)到讓設(shè)備斷開與主機(jī)的連接。原理是通過控制DP的上拉使能來控制連接狀態(tài)。配置OTGHS_DCTL.SFTDISCON=1,DP上拉不使能,斷開連接。配置OTGHS_DCTL.SFTDISCON=0,DP上拉使能,開始連接。

- Remote wakeup喚醒當(dāng)設(shè)備進(jìn)入掛起狀態(tài)之后,可以通過Remote wakeup功能喚醒主機(jī)。喚醒流程:1. 設(shè)置OTGHS_DCTL.RWKUPSIG=1;2. 延遲1-15ms3. 設(shè)置OTGHS_DCTL.RWKUPSIG=0;

- 忽略VBUS信號(hào)在設(shè)備模式下,可以忽略VBUS信號(hào),此模式可以釋放VBUS引腳給其它外設(shè)使用。通過配置OTGHS_GCCFG.VBUSIG=1來忽略VBUS信號(hào)。

- 支持內(nèi)部DMAIN/OUT端點(diǎn)都支持DMA操作,可通過DMA交換USB FIFO和用戶SRAM的數(shù)據(jù)。

OTGHS設(shè)備端點(diǎn)配置

本節(jié)簡(jiǎn)單介紹OTGHS端點(diǎn)寄存器的配置。

一、IN端點(diǎn)配置IN端點(diǎn)寄存器OTGHS_DIEPCTLx(x為0~7),端點(diǎn)寄存器存放端點(diǎn)的基本信息。如下是一個(gè)IN端點(diǎn)的基本配置選項(xiàng):

- OTGHS_DIEPCTLx.MPS(最大包長(zhǎng)度)

- OTGHS_DIEPCTLx.EPTYPE(端點(diǎn)類型:控制傳輸,同步傳輸,塊傳輸,中斷傳輸)

- OTGHS_DIEPCTLxTXFNUM(發(fā)送FIFO編號(hào),正常跟端點(diǎn)號(hào)相同)

- OTGHS_DIEPCTLx.USBACEPT(激活端點(diǎn))

- OTGHS_DIEPCTLx.SNAK(設(shè)置端點(diǎn)為NAK狀態(tài))

- OTGHS_DIEPCTLx.CNAK(清除端點(diǎn)NAK狀態(tài))

- OTGHS_DIEPCTLx.STALL(設(shè)置端點(diǎn)為STALL狀態(tài))

- OTGHS_DIEPCTLx.EPTENA(開始傳輸數(shù)據(jù))

二、OUT端點(diǎn)配置OUT端點(diǎn)寄存器OTGHS_DOEPCTLx(x為0~7),端點(diǎn)寄存器存放端點(diǎn)的基本信息。如下是一個(gè)OUT端點(diǎn)的基本配置選項(xiàng):

- OTGHS_DOEPCTLx.MPS(最大包長(zhǎng)度)

- OTGHS_DOEPCTLx.EPTYPE(端點(diǎn)類型:控制傳輸,同步傳輸,塊傳輸,中斷傳輸)

- OTGHS_DOEPCTLx.USBACEPT(激活端點(diǎn))

- OTGHS_DOEPCTLx.SNAK(設(shè)置端點(diǎn)為NAK狀態(tài))

- OTGHS_DOEPCTLx.CNAK(清除端點(diǎn)NAK狀態(tài))

- OTGHS_DOEPCTLx.STALL(設(shè)置端點(diǎn)為STALL狀態(tài))

- OTGHS_DOEPCTLx.EPTENA(開始傳輸數(shù)據(jù))

主機(jī)模式

OTGHS作為主機(jī)模式時(shí)支持高速/全速/低速設(shè)備,同時(shí)支持16個(gè)主機(jī)通道。

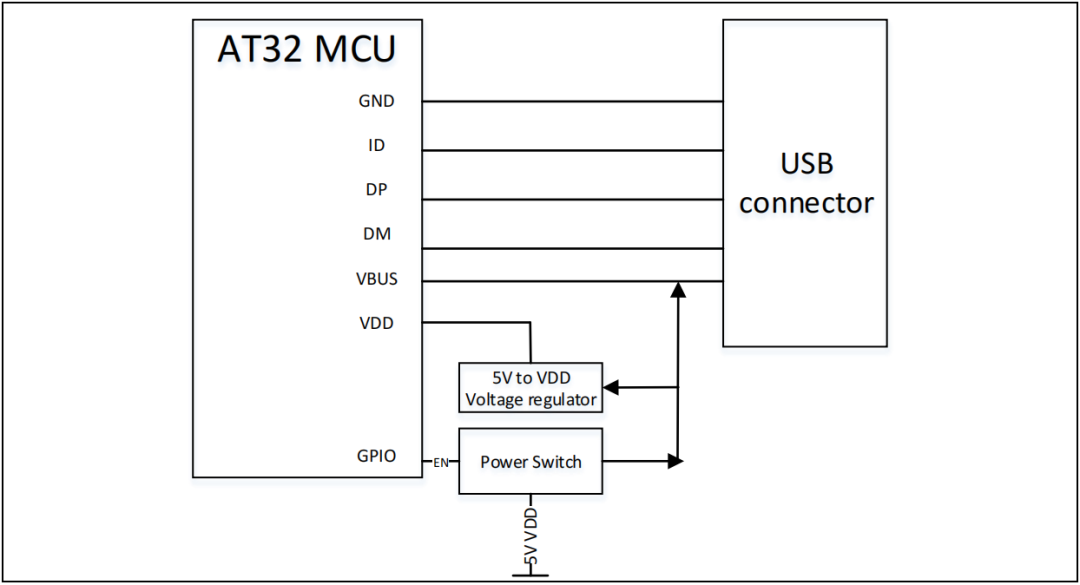

OTGHS強(qiáng)制作為主機(jī)

通過設(shè)定如下寄存器將OTGHS強(qiáng)制作為主機(jī),此時(shí)DP/DM下拉自動(dòng)使能:

- OTGHS_GUSBCFG.FDEVMODE=0(非強(qiáng)制設(shè)備模式)

- OTGHS_GUSBCFG.FHSTMODE=1(強(qiáng)制主機(jī)模式)

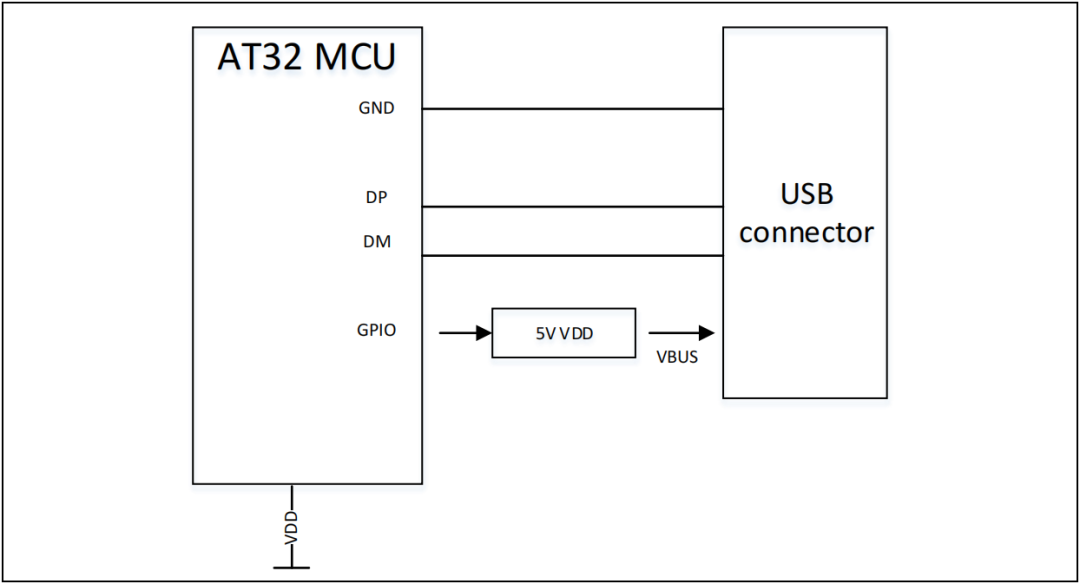

圖9.主機(jī)模式連接示意圖

OTGHS主機(jī)常用功能

- 支持高速、全速和低速設(shè)備通過OTGHS_HPRT.PRTSDP判斷當(dāng)前連接的設(shè)備是全速設(shè)備還是低速設(shè)備;OTGHS_HPRT.PRTSDP=0表示高速OTGHS_HPRT.PRTSDP=1表示全速OTGHS_HPRT.PRTSDP=2表示低速

- 復(fù)位通過設(shè)置OTGHS_HPRT.PRTRST來設(shè)置端口復(fù)位;OTGHS_HPRT.PRTRST=1;延時(shí)10msOTGHS_HPRT.PRTRST=0;

- 掛起通過設(shè)置OTGHS_HPRT.PRTSUP=1來設(shè)置端口掛起,此時(shí)主機(jī)停止發(fā)送SOF;

- 支持內(nèi)部DMA主機(jī)通道支持DMA操作,可通過DMA交換USB FIFO和用戶SRAM的數(shù)據(jù)

OTGHS主機(jī)通道配置

主機(jī)通道配置寄存器OTGHS_HCCHARx(x為0~15),通道寄存器存放通道的基本信息。如下是一個(gè)通道的基本配置選項(xiàng):

- OTGHS_HCCHARx.MPS(最大包長(zhǎng)度)

- OTGHS_HCCHARx.EPTNUM(指示設(shè)備端點(diǎn)號(hào))

- OTGHS_HCCHARx.EPTDIR(指示設(shè)備端點(diǎn)方向OUT/IN)

- OTGHS_HCCHARx.LSPDDEV(低速設(shè)備)

- OTGHS_HCCHARx.EPTYPE(端點(diǎn)類型:控制傳輸,同步傳輸,塊傳輸,中斷傳輸)

- OTGHS_HCCHARx.MC(周期性傳輸在每幀內(nèi)傳輸?shù)氖聞?wù)個(gè)數(shù))

- OTGHS_HCCHARx.DEVADDR(設(shè)備地址)

- OTGHS_HCCHARx.ODDFRM(周期性傳輸奇數(shù)幀/偶數(shù)幀)

- OTGHS_HCCHARx.CHDIS(通道禁止)

- OTGHS_HCCHARx.CHENA(通道使能)

-

雅特力

+關(guān)注

關(guān)注

0文章

179瀏覽量

8556 -

AT32

+關(guān)注

關(guān)注

1文章

121瀏覽量

2693

發(fā)布評(píng)論請(qǐng)先 登錄

識(shí)別AT32 MCU的應(yīng)用筆記

雅特力攜高效能AT32 MCU“芯”動(dòng)亮相ICCAD 2020

雅特力攜高性能AT32 MCU精彩亮相全球MCU生態(tài)發(fā)展大會(huì)

雅特力AT-Link Family為用戶帶來更完美開發(fā)體驗(yàn)

雅特力攜高性能 MCU亮相ELEXCON 2022,持續(xù)發(fā)力中高端

雅特力攜高性能AT32 MCU精彩亮相D Forum 2021 微控制器論壇

雅特力AT32 MCU完整生態(tài)系統(tǒng),加速創(chuàng)新開發(fā)進(jìn)程

慕尼黑上海電子展丨雅特力展臺(tái)首日速遞,AT32 MCU閃耀滬上

雅特力展臺(tái)首日速遞,AT32 MCU精彩亮相

雅特力AT32 MCU實(shí)現(xiàn)高效電機(jī)驅(qū)動(dòng)控制與應(yīng)用

雅特力AT32 OTGHS應(yīng)用筆記

雅特力AT32 OTGHS應(yīng)用筆記

評(píng)論