概述

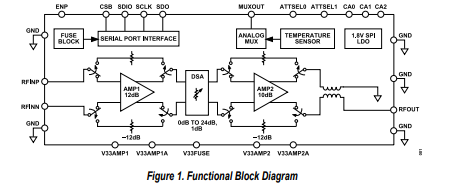

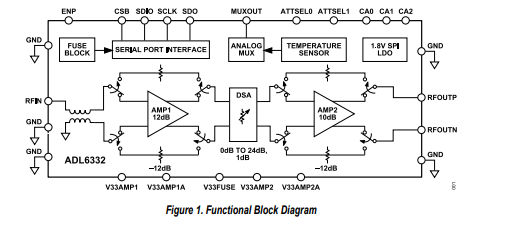

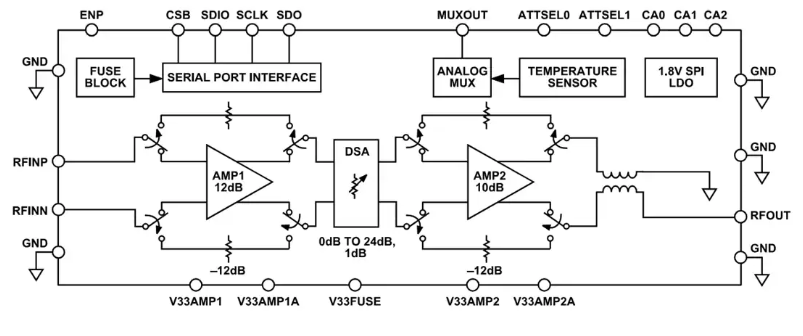

ADL6331 發(fā)射可變增益放大器(TxVGA)提供從 RF 數(shù)模轉(zhuǎn)換器(RF DAC)到單端功率放大器(PA)信號鏈的接口。每個 ADL6331 IC 均由一個平衡-不平衡轉(zhuǎn)換器、兩個帶旁路衰減器的差分 RF 放大器和一個數(shù)字步進(jìn)衰減器(DSA)組成,以在 24 端子、4.0 mm x 4.0 mm LGA 封裝中提供合適的發(fā)射器性能。

串行端口接口(SPI)控制可用于配置 RF 信號路徑或優(yōu)化電源電流與性能。

集成式 RF 巴倫用于提供 0.38 GHz 至 8.0 GHz(ADL6331-A)或 1.0 GHz 至 12.0 GHz(ADL6331-B)范圍內(nèi)的單端輸出,且具有良好的阻抗匹配。

數(shù)據(jù)表:*附件:ADL6331 0.38GHz至12GHz TxVGA技術(shù)手冊.pdf

應(yīng)用

特性

- 寬帶 TxVGA 將 RF-DAC 與波束合成和 PA 連接

- 工作頻率范圍:0.38 GHz 至 12 GHz,2 種產(chǎn)品型號

- ADL6331-A:0.38 GHz 至 8 GHz

- ADL6331-B:1.0 GHz 至 12 GHz

- 優(yōu)化 RF-DAC 的共模抑制、偶次諧波和互調(diào)

- 50 Ω 差分輸入和 50 Ω 單端輸出

- 集成寬帶射頻輸出平衡器

- 增益控制范圍為 70 dB,步長為 1 dB

- RF DSA 范圍:24.0 dB,步長為 1.0 dB

- 每個放大器旁路損耗為 12 dB

- 多個預(yù)定義衰減值和旁路放大器級之間的異步切換。

- 4 GHz 時的功率增益:15.1 dB (ADL6331-A), 15.4 dB (ADL6331-B)

- 4 GHz 時的噪聲指數(shù):7.5 dB (ADL6331-A), 7.5 dB (ADL6331-B)

- 4GHz 時的 OIP3:31.0 dBm (ADL6331-A),31.0 dBm(ADL6331-B)

- 4GHz 時的 OIP2:58 dBm (ADL6331-A), 56 dBm (ADL6331-B)

- 4GHz 時的 OP1dB:12.4 dBm (ADL6331-A), 12.0 dBm (ADL6331-B)

- 通過 3/4 線 SPI 完全可編程

- 3.3 V(單電源)

- 24 引腳、4.0 mm x 4.0 mm LGA

邏輯圖

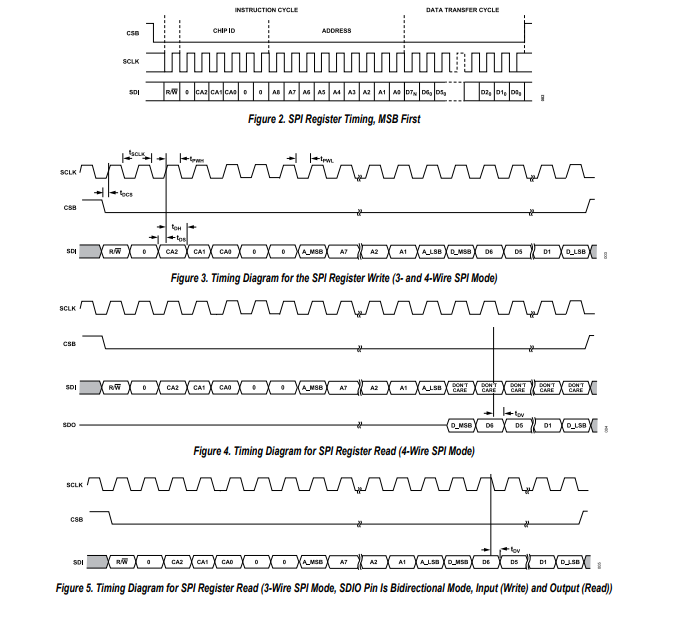

SPI時序圖

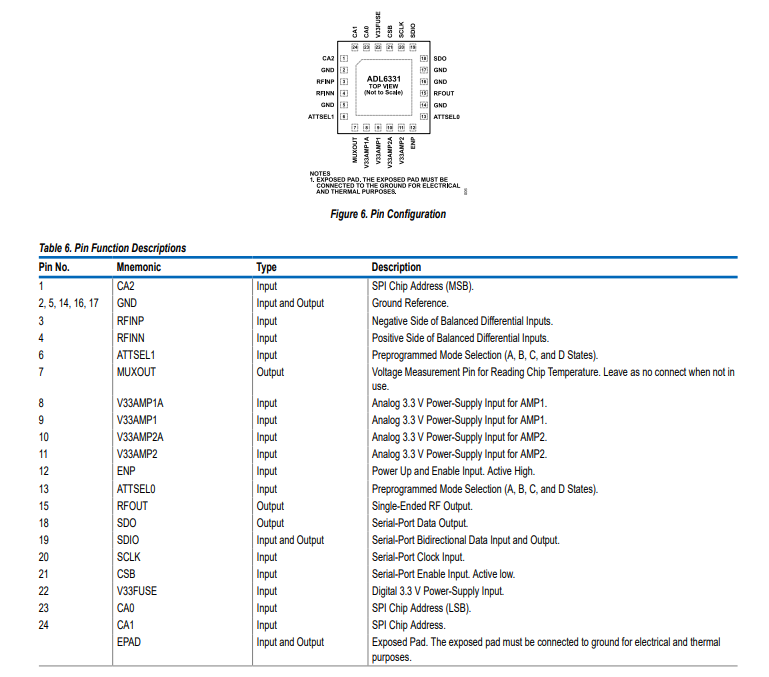

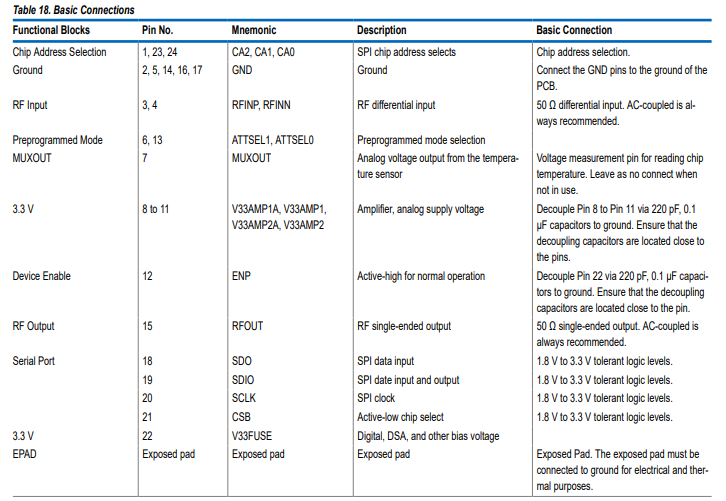

引腳配置描述

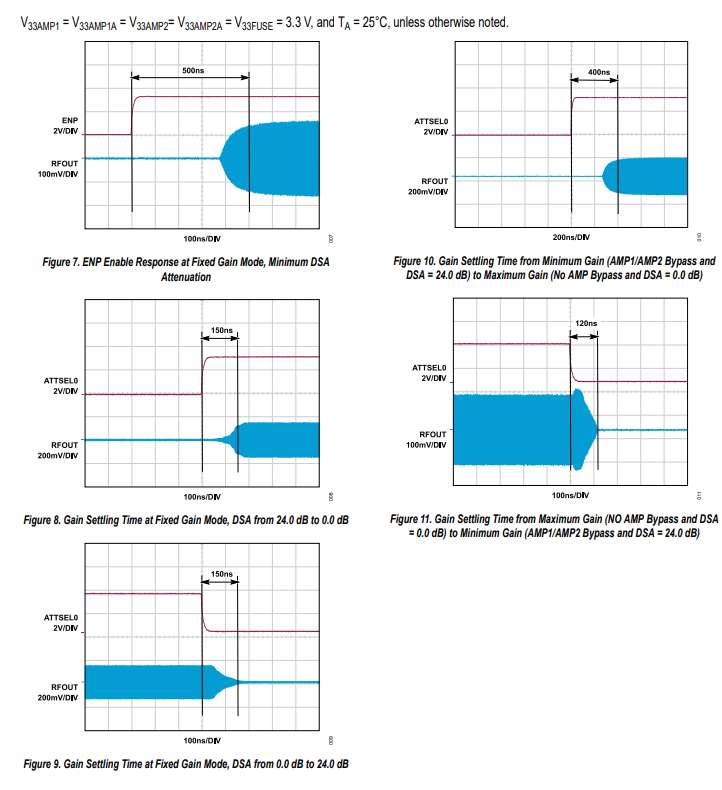

典型性能特征

串行端口接口(SPI)

ADL6331的SPI允許用戶通過三線或四線SPI模式為特定功能或操作配置設(shè)備。該串行端口接口由四條控制線路組成:SCLK、SDIO、SDO和CSB。對于四線SPI模式,SCLK、SDIO和SDO被使用;三線SPI模式則是SPI模式的默認(rèn)狀態(tài)。要啟用四線SPI模式,必須將SDOACTIVE[3]和SDOACTIVE[4]在寄存器0x000中設(shè)置為1。SPI中的定時要求列于表3中。

ADL6331協(xié)議由一個讀/寫操作、四個芯片地址位(最高有效位始終為0 )、九個寄存器地址位以及八個數(shù)據(jù)位組成。地址和數(shù)據(jù)字節(jié)均先傳輸最高有效位,最后傳輸最低有效位。為正確尋址設(shè)備,芯片地址前綴位必須與外部配置的芯片地址引腳CA2、CA1和CA0匹配。

ADL6331寫入SPI的輸入邏輯電平為1.8 V或3.3 V。在回讀周期中,通過設(shè)置SPI_3P3_CTRL位(寄存器0x121,位4 ),SDO可配置為1.8 V(默認(rèn) )或3.3 V回讀輸出電平。

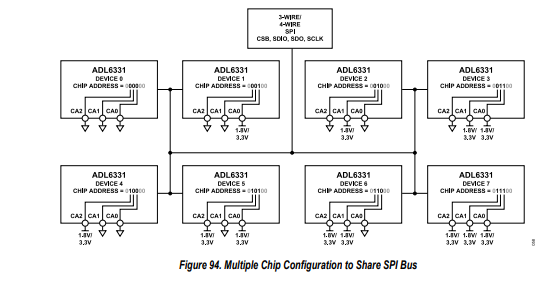

配置多個芯片共享SPI總線

最多可以使用同一條三線或四線SPI總線,通過單個CSB引腳尋址八個ADL6331設(shè)備。對于此功能,ADL6331的芯片選擇引腳(CA2、CA1和CA0 )用于標(biāo)識帶有SPI寫芯片地址前綴的芯片(SPI接口端口如圖2所示 )。

ADL6331協(xié)議會忽略芯片地址最高有效位與芯片地址引腳設(shè)置不相等的地址寫入,只有當(dāng)芯片地址前綴位的高四位與芯片地址引腳設(shè)置相等時,芯片才會接受地址。唯一的例外是軟件復(fù)位地址0x000。共享總線上的所有ADL6331芯片都會接受來自SPI主機(jī)控制器的0x000寄存器軟件復(fù)位。

圖94展示了如何配置芯片地址引腳CA2、CA1和CA0以及相關(guān)的芯片地址前綴位。

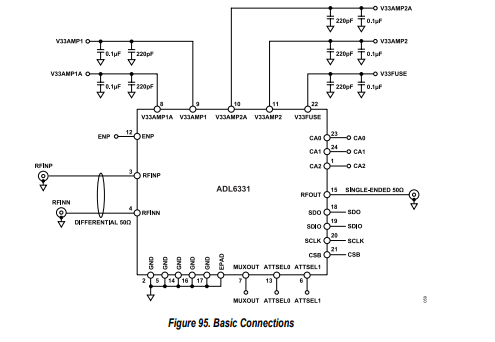

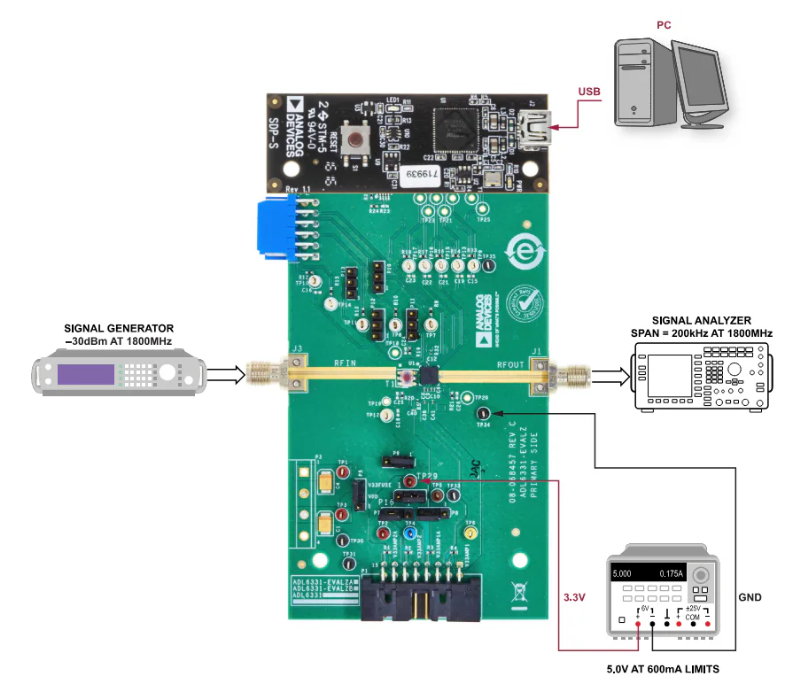

基本連接

應(yīng)用信息

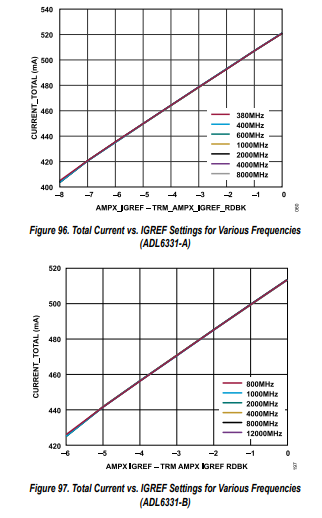

電流消耗優(yōu)化

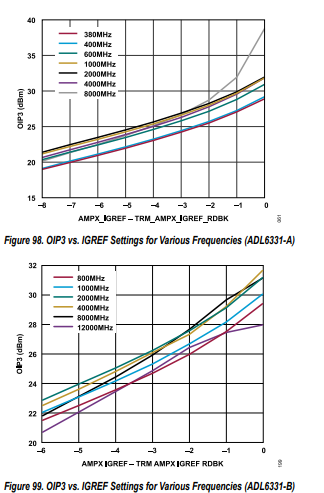

當(dāng)寄存器0x104、寄存器0x105和寄存器0x106(適用于AMP1 )以及寄存器0x111、寄存器0x112和寄存器0x113(適用于AMP2 )中的最高有效位(MSB)都設(shè)置為0時,這六個寄存器可供用戶使用。如果需要降低電流消耗,可根據(jù)需要設(shè)置AMP1的IGREF(在寄存器0x104中 )和AMP2的IGREF(在寄存器0x111中 )。工廠調(diào)校的IGREF(分別在寄存器0x140和寄存器0x143中,適用于AMP1和AMP2 )可實現(xiàn)最佳的OIP3性能,如圖98和圖99所示。

不建議將IGREF設(shè)置增加到高于AMP1和AMP2的回讀值,這樣做可能會影響器件的長期可靠性。

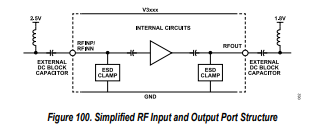

交流耦合

靜電放電(ESD)鉗位電路緊鄰輸入端口和輸出端口(見圖100 )。當(dāng)施加的直流電壓大于或等于1.0 V(這是常見情況 )時,存在硅控制整流器(SCR)觸發(fā)的風(fēng)險,即使是單個直流電壓尖峰也可能導(dǎo)致SCR觸發(fā)。帶有直流偏置的部件始終建議使用隔直電容進(jìn)行交流耦合。

-

RF

+關(guān)注

關(guān)注

65文章

3174瀏覽量

168594 -

數(shù)模轉(zhuǎn)換器

+關(guān)注

關(guān)注

14文章

1055瀏覽量

84023 -

可變增益放大器

+關(guān)注

關(guān)注

1文章

40瀏覽量

45896

發(fā)布評論請先 登錄

LMX2595在8GH,12GHz, 24GHz都會產(chǎn)生雜散,為什么?

電源技巧#8:設(shè)計12GHz,超低相位噪聲(0.09 ps rms抖動)鎖相環(huán)

ADL6010S:0.5 GHz至43.5 GHz包絡(luò)檢測器數(shù)據(jù)表

安捷倫1169A 12GHz探頭放大器套件特性參數(shù)

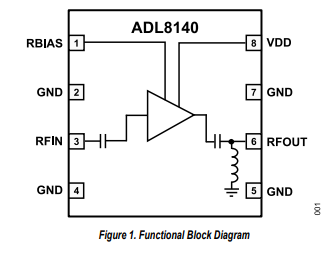

ADL6331:0.38千赫至12千赫TxVGA初步數(shù)據(jù)表 ADI

ADL6332:0.38千兆赫至12千兆赫RxVGA初步數(shù)據(jù)表 ADI

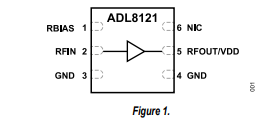

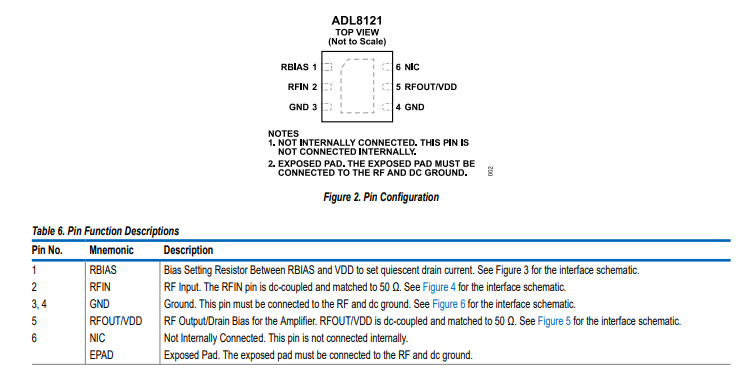

ADL8121 GaAs、pHEMT、MMIC、低噪聲放大器,0.025GHz至12GHz技術(shù)手冊

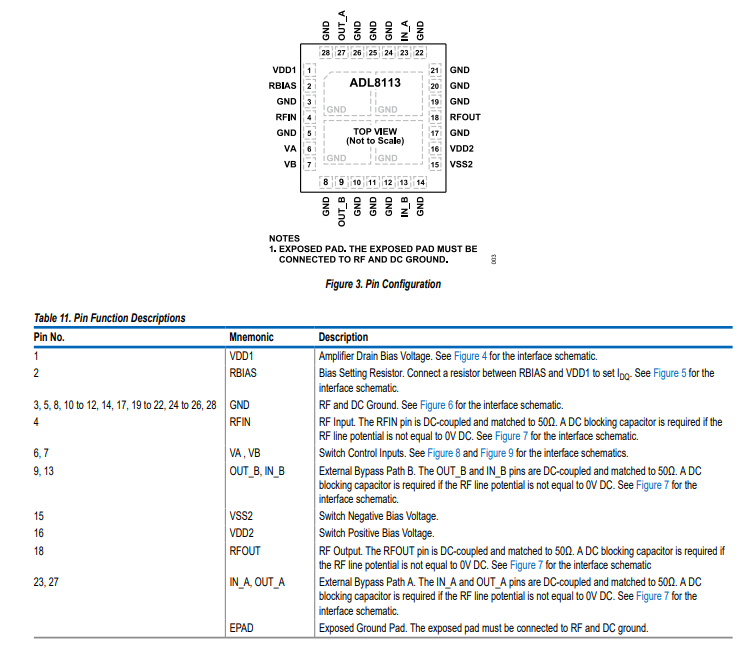

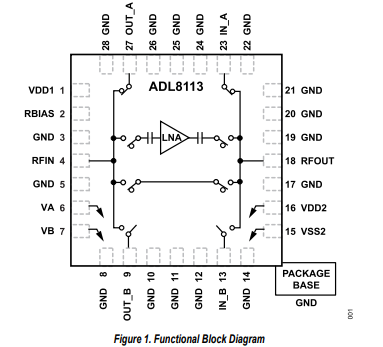

ADL8113 10MHz至12GHz低噪聲放大器,帶10MHz至14GHz旁路開關(guān)技術(shù)手冊

ADL6332 0.38GHz至15GHz RxVGA技術(shù)手冊

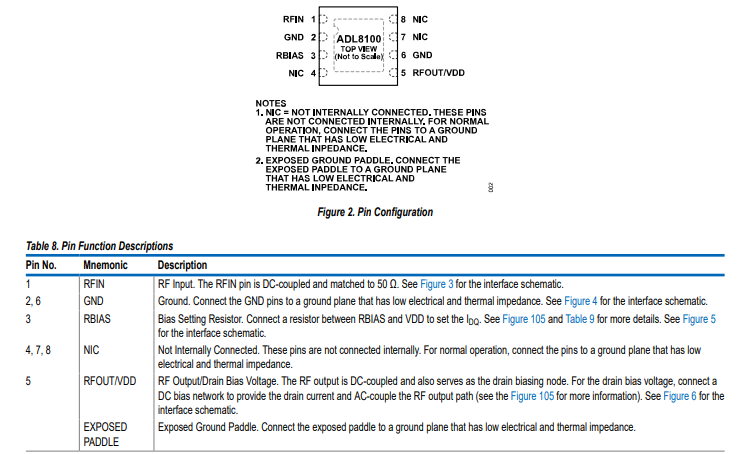

ADL8100 GaAs、pHEMT、MMIC、低噪聲放大器,0.01 GHz至20 GHz技術(shù)手冊

ADL8121 GaAs、pHEMT、MMIC、低噪聲放大器,0.025 GHz至12 GHz技術(shù)手冊

ADL8113 10MHz至12GHz低噪聲放大器,帶有10MHz至 14GHz旁路開關(guān)技術(shù)手冊

Analog Devices Inc. ADL6331發(fā)射可變增益放大器 (TxVGA)數(shù)據(jù)手冊

Analog Devices Inc. ADL6331-EVALZA 評估板數(shù)據(jù)手冊

ADL6331 0.38GHz至12GHz TxVGA技術(shù)手冊

ADL6331 0.38GHz至12GHz TxVGA技術(shù)手冊

評論