概述

ADRF5714 是一款 1 位硅工藝數字衰減器,具有 16 dB 衰減率,并且支持無干擾操作。

該套件的工作頻率范圍為 100 MHz 至 30 GHz,具有優于 1.3 dB 的插入損耗和出色的衰減精度。ADRF5714 的 ATTIN 端口具有 30 dBm 平均和 33 dBm 峰值的 RF 輸入功率處理能力。

ADRF5714 需要 +3.3 V 和 ?3.3 V 的雙電源電壓。此套件采用互補金屬氧化物半導體 (CMOS)-/低電壓晶體管至晶體管邏輯 (LVTTL) 兼容控制。

ADRF5714 還可使用單一正電源電壓 (V DD ) 工作。負電源電壓 (V SS ) 接地。有關更多詳細信息,請參見數據手冊的“工作原理”部分。

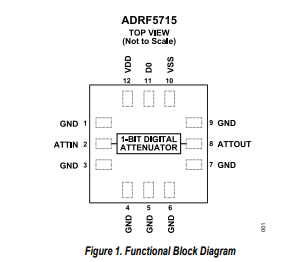

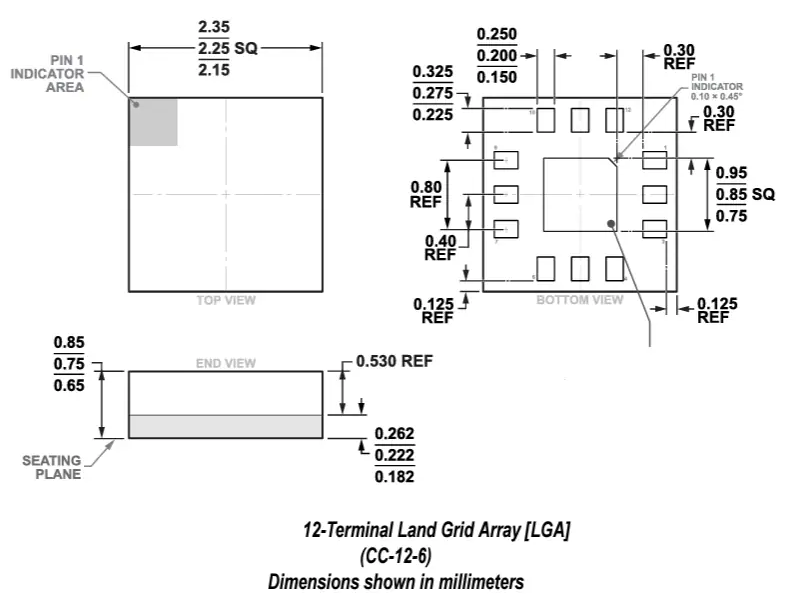

ADRF5714 射頻端口旨在匹配 50 Ω 的特性阻抗。ADRF5714 采用符合 RoHS 標準的 12 端子、2.25 mm × 2.25 mm、LGA 封裝, 并可在 ?40°C 至 +105°C 的溫度范圍內工作。

數據表:*附件:ADRF5714硅數字衰減器,1位,100MHz至30GHz技術手冊.pdf

應用

特性

- 超寬帶頻率范圍:0.1 GHz 至 30 GHz

- 16 dB 單一衰減步長

- 低插入損耗

- 0.7 dB (8 GHz)

- 0.9 dB (18 GHz)

- 1.3 dB (30 GHz)

- 衰減精度:±0.20 dB 典型值,最高 30 GHz

- 高輸入線性度

- P0.1dB 插入損耗狀態:33 dBm

- P0.1dB 16 dB 衰減狀態:29 dBm

- IP3 插入損耗路徑:57 dBm(典型值)

- IP3 16 dB 衰減狀態:49 dBm(典型值)

- 高 RF 功率處理能力

- 30 dBm(典型值)穩態平均值

- 33 dBm(典型值)穩態峰值

- RF 幅度建立時間(0.1 dB 最終 RF

OUT):110 ns - 支持單電源工作

- 在相對相位中實現緊密分布

- 無低頻雜散信號

- 與 CMOS/LVTTL 兼容

- 12 端子 2.25 mm x 2.25 mm 岸面柵格陣列 (LGA) 封裝

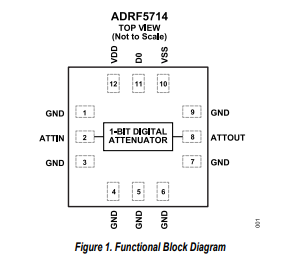

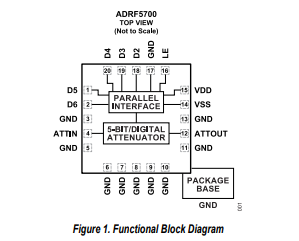

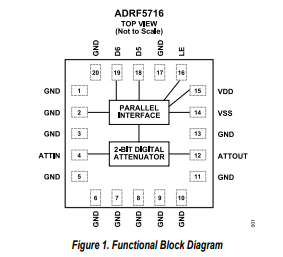

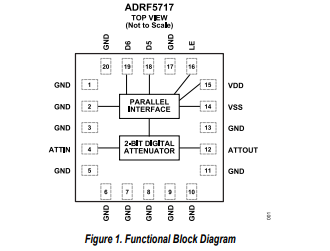

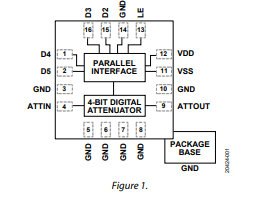

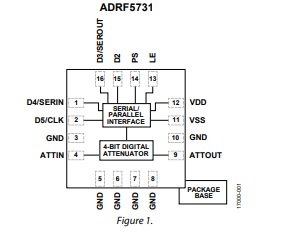

框圖

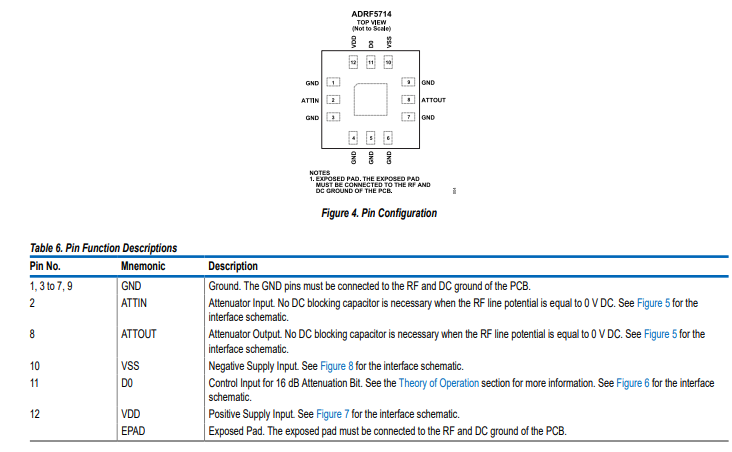

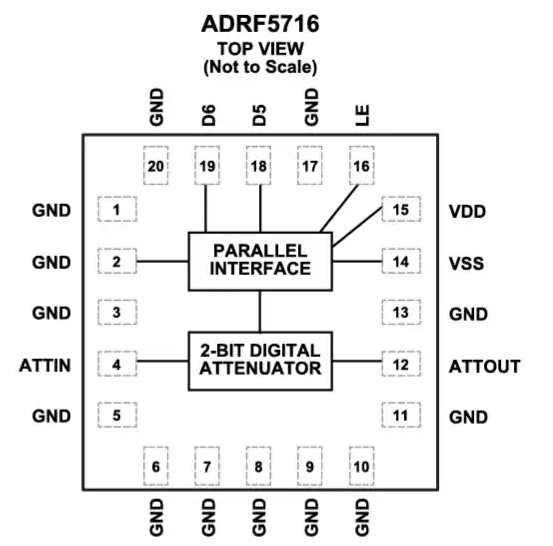

引腳配置描述

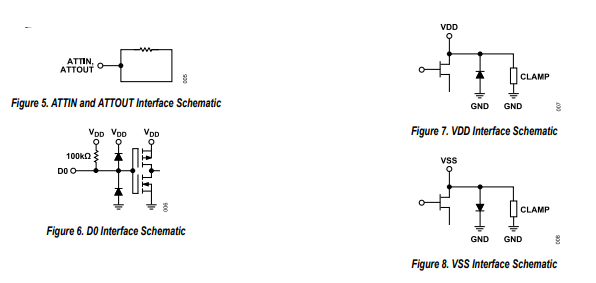

接口示意圖

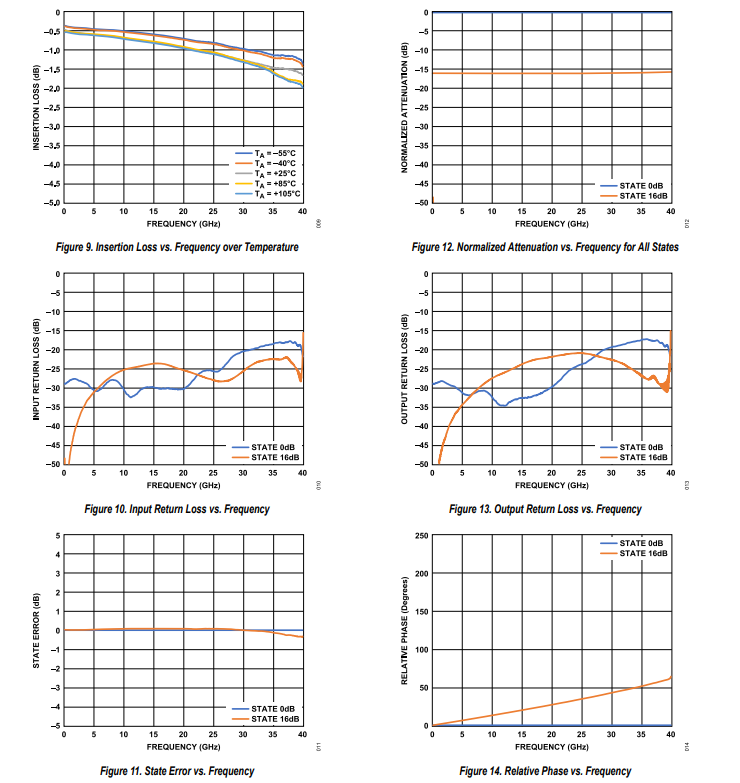

典型性能特征

應用信息

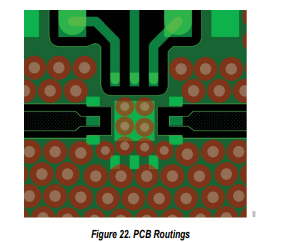

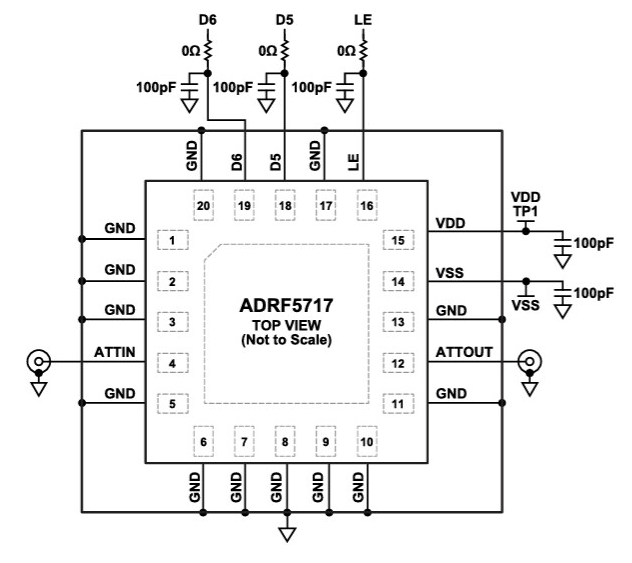

射頻傳輸線采用共面波導(CPWG)模型設計,走線寬度為16密耳,與接地層的間距為6密耳,特性阻抗為50Ω。為實現最佳射頻和熱接地效果,應通過盡可能多的過孔,圍繞器件的外露焊盤進行布線。

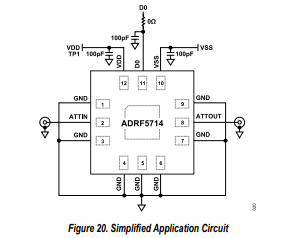

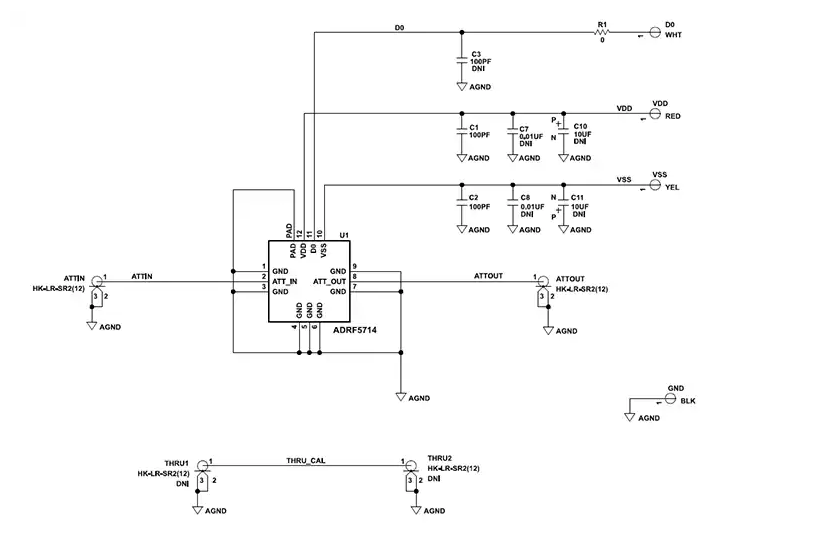

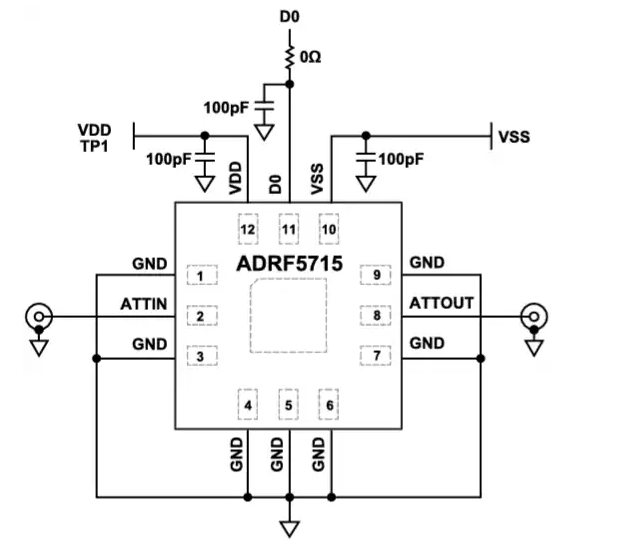

射頻輸入和輸出端口(ATTIN和ATTOUT)通過50Ω傳輸線連接。VDD和VSS電源引腳通過一個100 pF的旁路電容來濾除高頻噪聲。圖20展示了ADRF5714的簡化應用電路。

印刷電路板(PCB)設計建議

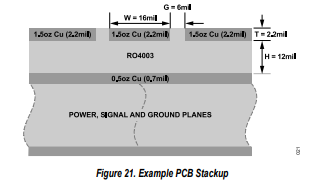

射頻端口需匹配50Ω阻抗,引腳設計為與PCB上的50Ω CPWG具有匹配的特性阻抗。圖21展示了ADRF5714射頻走線的推薦CPWG射頻電路設計,采用兩層12密耳厚的Rogers RO4003C介電材料。對于2.2密耳成品銅厚,建議采用寬度為16密耳、間距為6密耳的射頻走線。

圖22展示了射頻走線、電源和控制信號在ADRF5714上的布線情況。接地層通過盡可能多的過孔連接,以實現最佳射頻和熱接地效果。

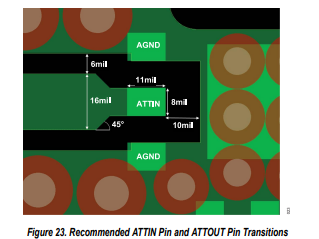

圖23展示了ADRF5714從ATTIN和ATTOUT引腳到參考堆疊上50Ω CPWG的推薦布局。PCB焊盤按1:1比例繪制為器件焊盤。接地焊盤按阻焊層定義繪制,信號焊盤按焊盤限定繪制。從PCB焊盤引出的射頻走線以45°角延伸。焊膏掩模也經過設計,以匹配焊盤的阻抗降低需求。焊膏掩模被劃分為多個開口。

-

衰減器

+關注

關注

4文章

726瀏覽量

34998 -

引腳

+關注

關注

16文章

1614瀏覽量

52439 -

硅工藝

+關注

關注

0文章

12瀏覽量

7128

發布評論請先 登錄

UG-1831:評估ADRF5740 2 dB LSB、4位、硅數字衰減器,10 MHz至60 GHz

ADRF5714: 硅數字加速器,1-比特,100兆赫至30千兆赫初步數據表 ADI

ADRF5700 46dB、2dB LSB、5位、硅數字衰減器,100MHz至22GHz技術手冊

ADRF5730 0.5dB LSB、6位硅數字衰減器,100MHz至40GHz技術手冊

GaAs 數字衰減器 5 位、1 dB LSB 400 MHz-4 GHz skyworksinc

Analog Devices Inc. EVAL-ADRF5714 評估板數據手冊

ADRF5714硅數字衰減器,1位,100MHz至30GHz技術手冊

ADRF5714硅數字衰減器,1位,100MHz至30GHz技術手冊

評論