概述

ADRF5740是一款硅、4位數字衰減器,以2 dB步長提供22 dB的衰減控制范圍。

ADRF5740的工作頻率范圍為10 MHz至60 GHz,在55 GHz下提供小于3.3 dB的插入損耗和衰減精度(±0.2 + 7.0%的衰減狀態)。在所有狀態下,ADRF5740的ATTIN端口具有24 dBm(平均值)和24 dBm(峰值)的RF輸入功率處理能力。

ADRF5740需要+3.3 V和?3.3 V雙電源電壓供電。ADRF5740具有并行模式控制、CMOS和低壓晶體管對晶體管邏輯(LVTTL)兼容控制特性。

ADRF5740 RF端口設計用于匹配50 Ω的特征阻抗。ADRF5740采用符合RoHS標準的16引腳、2.5 mm × 2.5 mm、基板柵格陣列(LGA)封裝,工作溫度范圍為?40°C至+105°C。

數據表:*附件:ADRF5740 2dB LSB、4 位硅數字衰減器(100MHz至60GHz)技術手冊.pdf

應用

- 工業掃描儀

- 測試和儀器儀表

- 蜂窩基礎設施:5G 毫米波

- 軍用無線電、雷達、電子對抗(ECM)

- 微波無線電和甚小孔徑終端(VSAT)

特性 - 超寬帶頻率范圍:10 MHz至60 GHz

- 衰減范圍:2 dB步進至22 dB

- 低插入損耗

- 1.4 dB,最高為20 GHz

- 2.2 dB,最高為44 GHz

- 3.3 dB,最高為55 GHz

- 衰減精度

- ±(0.1 + 1.0%)的狀態,最高20 GHz

- ±(0.2 + 3.0%)的狀態,最高44 GHz

- ±(0.2 + 7.0%)的狀態,最高55 GHz

- 典型步進誤差

- ± 0.30 dB,最高為20 GHz

- ± 0.50 dB,最高為44 GHz

- ± 0.60 dB,最高為55 GHz

- 高輸入線性度

- P0.1dB:25.5 dBm(典型值)

- IP3:45 dBm(典型值)

- 高RF輸入功率處理:24 dBm平均值,24 dBm峰值

- 相對相位中的緊湊分布

- 無低頻雜散信號

- 并行模式控制,CMOS和LVTTL兼容

- RF幅度建立時間(0.1 dB最終RF輸出):175 ns

- 符合RoHS標準的16引腳、2.5 mm × 2.5 mm、LGA封裝

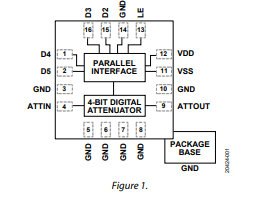

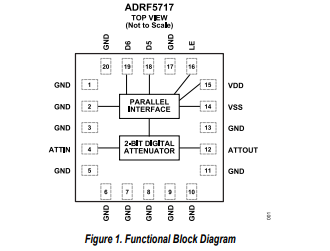

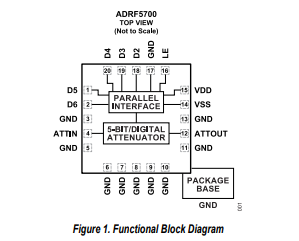

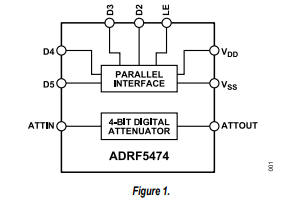

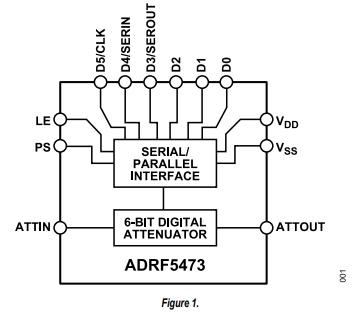

框圖

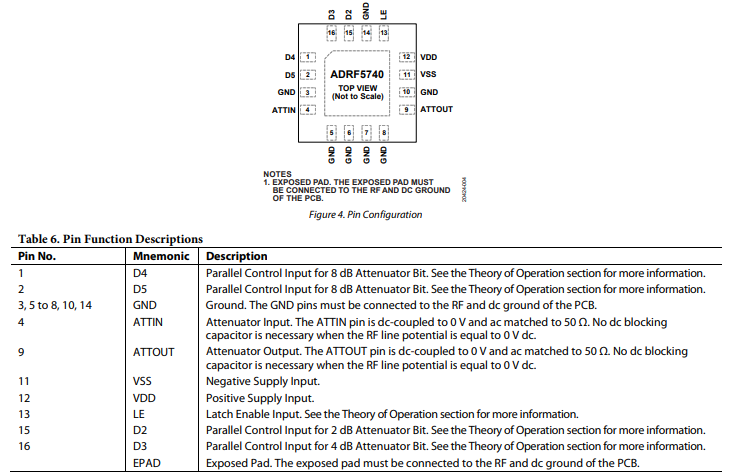

引腳配置描述

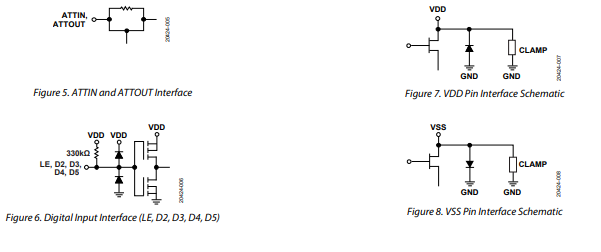

接口示意圖

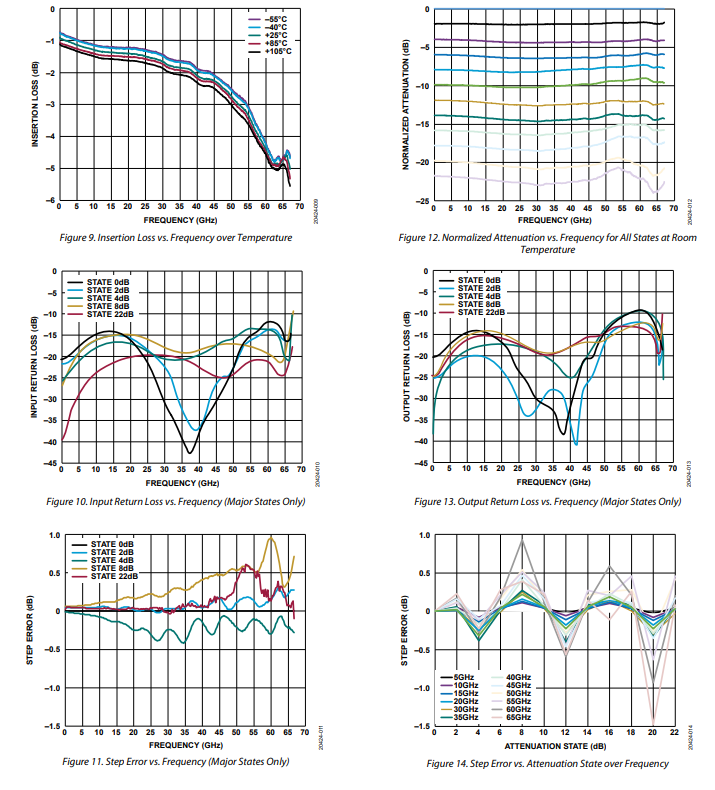

典型性能特征

應用信息

布局注意事項

本數據手冊中的所有測量均在ADRF5740 - EVALZ - 185評估板上進行。ADRF5740 - EVALZ - 185和ADRF5740 - EVALZ - 292的設計為ADRF5740應用的布局提供了建議。

電路板布局

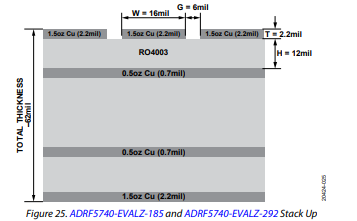

ADRF5740 - EVALZ - 185和ADRF5740 - EVALZ - 292是四層評估板。外層銅(Cu)層為0.5盎司(0.7密耳),鍍覆至1.5盎司(2.2密耳),中間由電介質材料隔開。圖25展示了ADRF5740 - EVALZ - 185和ADRF5740 - EVALZ - 292的堆疊結構。

所有射頻和直流走線都布置在頂層銅層,而內層和底層為接地層,為射頻傳輸線提供穩固的接地。頂層電介質材料為12密耳的Rogers RO4003,可提供最佳的高頻性能。中間和底層電介質材料提供機械強度。電路板總厚度為62密耳,可安裝1.85 mm的射頻連接器。

射頻與數字控制

射頻傳輸線采用共面波導(CPWG)模型設計,線寬為16密耳,與接地層間距為6密耳,特性阻抗為50Ω。為實現最佳射頻和熱接地效果,應圍繞傳輸線及器件外露焊盤布置盡可能多的過孔。

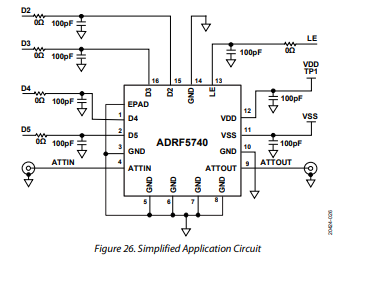

射頻輸入和輸出端口(ATTIN和ATTOUT)通過50Ω傳輸線連接到1.85 mm射頻連接器。在VDD和VSS電源引線上,接有一個100 pF的旁路電容來濾除高頻噪聲。圖26展示了ADRF5740的簡化應用電路。

-

衰減器

+關注

關注

4文章

726瀏覽量

35122 -

引腳

+關注

關注

16文章

1681瀏覽量

52682 -

LVTTL

+關注

關注

0文章

88瀏覽量

13311

發布評論請先 登錄

UG-1831:評估ADRF5740 2 dB LSB、4位、硅數字衰減器,10 MHz至60 GHz

ADRF5700: 46 dB, 2 dB LSB, 5-Bit, 硅數字加速器, 100 MHz 至 22 GHz 初步數據表 ADI

GaAs 數字衰減器 5 位、1 dB LSB 400 MHz-4 GHz skyworksinc

3 位數字衰減器 500 MHz–6 GHz,1 dB LSB skyworksinc

ADRF5740 2dB LSB、4 位硅數字衰減器(100MHz至60GHz)技術手冊

ADRF5740 2dB LSB、4 位硅數字衰減器(100MHz至60GHz)技術手冊

評論