概述

MAX5882為14位、4.6Gsps數(shù)/模轉(zhuǎn)換器(DAC),將電纜調(diào)制解調(diào)器終端(CMTS)和EQAM設(shè)備的多載波正交調(diào)幅(QAM)信號(hào)直接合成為RF輸出。DAC具有優(yōu)異的雜散特性和噪聲、鄰道功率(ACP)性能,并可根據(jù)電纜數(shù)據(jù)傳輸業(yè)務(wù)接口規(guī)范(DOCSIS?)的要求直接合成為47MHz至1003MHz電纜下行鏈路的多個(gè)載波。4.6Gsps刷新速率允許以數(shù)字方式產(chǎn)生高于2GHz帶寬的信號(hào)。

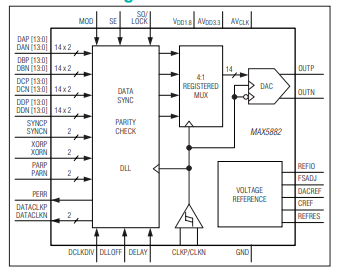

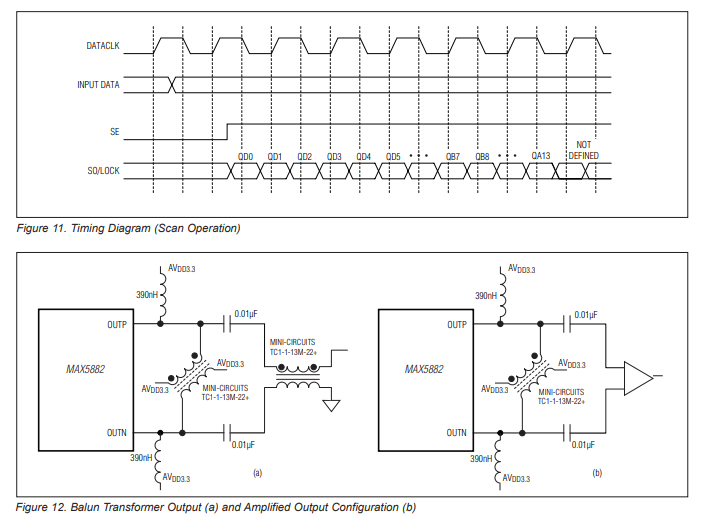

器件具有四個(gè)14位、多路復(fù)用的低壓差分信號(hào)(LVDS)輸入端口,每個(gè)端口可工作在高達(dá)1150Mwps的雙數(shù)據(jù)率(DDR)或單數(shù)據(jù)率(SDR)模式。輸入支持差分高速收發(fā)器邏輯(DHSTL)輸入電平。由于在時(shí)鐘的上升沿和下降沿均觸發(fā)轉(zhuǎn)換,器件能夠支持的速率為1/2 DAC刷新時(shí)鐘頻率。每個(gè)端口的輸入數(shù)據(jù)速率為DAC刷新率的1/4或時(shí)鐘速率的1/2。器件集成延時(shí)鎖相環(huán)(DLL),簡化與FPGA或ASIC器件的接口。利用DLL調(diào)節(jié)輸出時(shí)鐘(DATACLK)的相位,以確保輸入LVDS數(shù)據(jù)總線與數(shù)據(jù)鎖存片上時(shí)鐘保持恰當(dāng)?shù)亩〞r(shí)關(guān)系。

器件為電流控制型DAC,集成50Ω差分輸出匹配電阻,以確保最佳動(dòng)態(tài)性能。器件采用3.3V和1.8V電源供電,工作在4.6Gsps時(shí),功耗僅為2.3W。器件工作在擴(kuò)展商業(yè)級(jí)溫度范圍(0°C至+85°C),采用256 CSBGA無鉛(Pb)/符合RoHS標(biāo)準(zhǔn)的封裝。

數(shù)據(jù)表:*附件:MAX5882 14位、4.6Gsps電纜下行RF直接合成DAC技術(shù)手冊.pdf

應(yīng)用

- 廣播級(jí)視頻調(diào)制器

- 電纜調(diào)制解調(diào)器終端系統(tǒng)(CMTS)

- DOCSIS兼容Edge QAM設(shè)備

- 視頻點(diǎn)播(VOD)

特性

- 4.6Gsps輸出刷新率

- 直接合成RF輸出,47MHz至1003MHz

- 不會(huì)將HD3混疊到電纜頻帶

- 業(yè)內(nèi)領(lǐng)先的DOCSIS 3.0噪底指標(biāo)

- -70dBc @ f

OUT= 900MHz,8通道(256 QAM) - -66dBc @ f

OUT= 900MHz,16通道(256 QAM) - -62dBc @ f

OUT= 900MHz,32通道(256 QAM) - -57dBc @ f

OUT= 500MHz,128通道(256 QAM)

- -70dBc @ f

- 9dBm (CW)高輸出功率

- 支持低功耗設(shè)計(jì)

- 4:1多路復(fù)用LVDS輸入

- 每個(gè)端口高達(dá)1150Mwps

- 雙數(shù)據(jù)率(DDR)模式

- 片上DLL用于同步輸入數(shù)據(jù)

- 奇偶校驗(yàn)錯(cuò)誤標(biāo)識(shí)

- 內(nèi)部50Ω差分輸出匹配電阻

- 輸入寄存器掃描模式

- 緊湊的17mm × 17mm、256引腳CSBGA封裝

- 備有評估板(定購MAX5882EVKIT+)

框圖

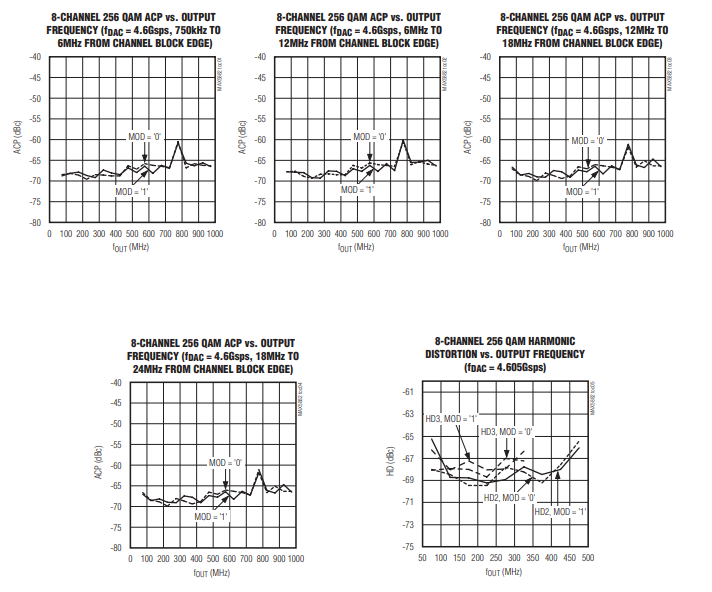

典型操作特性

應(yīng)用信息

啟動(dòng)條件

該設(shè)備采用了保護(hù)電路,以防止數(shù)模轉(zhuǎn)換器(DAC)輸出端受損。當(dāng)參考電壓(VREFIO)低于0.4V時(shí),內(nèi)部時(shí)鐘電路將被禁用。當(dāng)DAC輸出不工作時(shí),保護(hù)電路處于激活狀態(tài)。如果數(shù)據(jù)來源需要DATA時(shí)鐘來正常運(yùn)行,那么參考電壓必須保持在0.4V以上。

設(shè)備的數(shù)字鎖相環(huán)(DLL)電路需要一個(gè)有源、穩(wěn)定的時(shí)鐘輸入和穩(wěn)定的電源,才能準(zhǔn)確運(yùn)行。在施加初始電源并使時(shí)鐘穩(wěn)定后,DLL電路應(yīng)通過將DLLOFF引腳設(shè)置為邏輯0來復(fù)位。然后可以根據(jù)需要更改DLL頻率和延遲。

輸出耦合

OUTP和OUTN之間的差分電壓可使用變壓器或差分放大器轉(zhuǎn)換為單端電壓。數(shù)模轉(zhuǎn)換器(DAC)輸出應(yīng)上拉至AVDD3.3。建議使用偏置電阻將輸出從兩個(gè)獨(dú)立電感分壓器上拉。圖12中展示了推薦的輸出電路配置。為實(shí)現(xiàn)最大帶寬并最小化變壓器次級(jí)側(cè)接地引線上的電感,請使用極短的走線,并在接地層上使用多個(gè)過孔進(jìn)行連接。

頻譜考量

DAC更新速率選擇

該設(shè)備4.6Gsps的最大更新速率為系統(tǒng)設(shè)計(jì)提供了靈活性。在更新速率與性能或電路復(fù)雜度方面存在幾種權(quán)衡,選擇DAC更新速率時(shí)應(yīng)考慮這些因素。

由于DAC輸出在時(shí)鐘的兩個(gè)邊緣上都有輸出,所以在fDAC/2 - fOUT處會(huì)出現(xiàn)所需DAC輸出的衰減鏡像。DAC更新速率必須至少是電纜帶寬內(nèi)產(chǎn)生的最高頻率的四倍,以將此鏡像排除在頻帶之外。由于DOCSIS(數(shù)據(jù)業(yè)務(wù)接口規(guī)范)射頻附件A定義了3.03MHz的上限頻率,在某些情況下,為了將此鏡像的帶外抑制保持在40dB以上,需要1GHz的輸出濾波器。隨著DAC更新速率降低至較低要求,濾波器的設(shè)計(jì)變得越來越困難。不過,使用較低的更新速率有幾個(gè)潛在優(yōu)點(diǎn)。首先,隨著更新速率從4.6Gsps的最大值降低到4Gsps,設(shè)備的整體雜散性能會(huì)提高。其次,系統(tǒng)輸入的功率要求會(huì)降低。在4Gsps時(shí),設(shè)備本身的功耗比4.6Gsps時(shí)大約低15%,而ASIC或FPGA等其他組件在較低更新速率下的功耗也會(huì)降低。另一個(gè)需要考慮的因素是,較高更新速率下的時(shí)序裕度會(huì)減小,且更難滿足要求。

諧波失真

該設(shè)備具有較低的諧波失真。二次諧波失真(HD2)和三次諧波失真(HD3)通常是主要的諧波。在500MHz以下的頻率,HD2在1GHz以下的頻率通常低于-60dBc。當(dāng)DAC更新速率高于4Gsps時(shí),HD2和HD3在低于333MHz的輸出頻率下不會(huì)混疊到45MHz至1000MHz頻段內(nèi)。

時(shí)鐘頻率附近的諧波

該設(shè)備在fDAC/2 - 2×fOUT處存在雜散信號(hào)。此雜散信號(hào)低于DOCSIS限制,但可能會(huì)違反DOCSIS射頻共存要求,即較低頻道與較高輸出頻率共存時(shí)的要求。當(dāng)fOUT = fDAC/6時(shí),此雜散信號(hào)與輸出頻率重合。如有必要,可使用數(shù)字預(yù)失真來降低此雜散信號(hào)。

接地、旁路、電源和電路板布局注意事項(xiàng)

接地和電源去耦會(huì)顯著影響設(shè)備的性能。不需要的數(shù)字串?dāng)_可能會(huì)通過輸入、參考電壓、電源和接地連接耦合進(jìn)來,從而影響動(dòng)態(tài)性能。應(yīng)嚴(yán)格遵循高速、高頻應(yīng)用的正確接地和電源去耦準(zhǔn)則。這可減少電磁干擾(EMI)和內(nèi)部串?dāng)_,從而顯著提升設(shè)備的動(dòng)態(tài)性能。

需要使用具有獨(dú)立接地和電源平面的多層印刷電路板(PCB)。建議將模擬輸出和時(shí)鐘輸入作為受控阻抗微帶線在電路板頂層直接布線,且不使用過孔連接時(shí)鐘輸入(CLKP、CLKN)和模擬輸出(OUTP、OUTN)信號(hào)。根據(jù)走線長度和工作條件,可能需要使用低介電常數(shù)材料(如ROGERS RO4003)作為頂層材料,以便對數(shù)據(jù)時(shí)鐘(DATACLKP、DATACLKIN)和DAC輸出進(jìn)行路由,從而將耦合到時(shí)鐘輸入和DAC輸出的干擾降至最低。

數(shù)字信號(hào)應(yīng)作為受控阻抗走線在接地平面之間布線。數(shù)字信號(hào)應(yīng)遠(yuǎn)離敏感的模擬輸入、參考輸入感應(yīng)線、公共模式輸入,并且盡量遠(yuǎn)離時(shí)鐘輸入。尤其重要的是,要盡量減少數(shù)字信號(hào)與時(shí)鐘之間的耦合,以優(yōu)化高速輸出頻率下的動(dòng)態(tài)性能。對稱的時(shí)鐘輸入和模擬輸出走線設(shè)計(jì)對于減少失真和優(yōu)化DAC的動(dòng)態(tài)性能至關(guān)重要。

數(shù)字信號(hào)路徑應(yīng)盡量短,走線長度應(yīng)匹配,以避免數(shù)據(jù)延遲失配。

-

dac

+關(guān)注

關(guān)注

43文章

2361瀏覽量

192803 -

數(shù)模轉(zhuǎn)換器

+關(guān)注

關(guān)注

14文章

1049瀏覽量

83864 -

MAX5882

+關(guān)注

關(guān)注

0文章

2瀏覽量

5342

發(fā)布評論請先 登錄

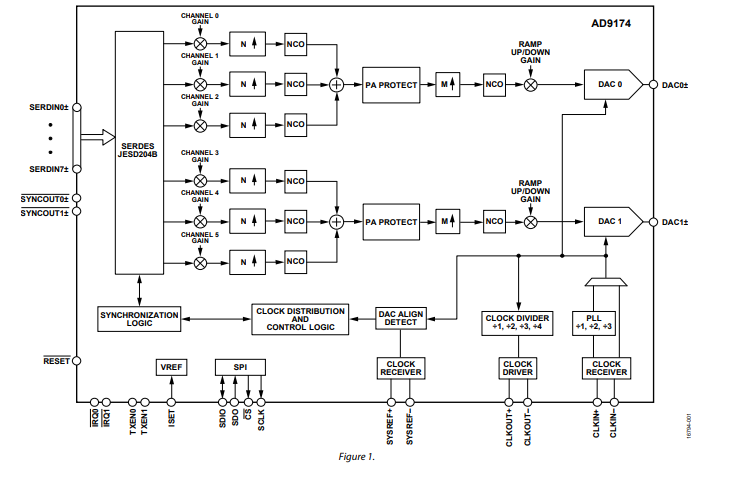

基于RF DAC的RF直接變頻發(fā)送器實(shí)現(xiàn)設(shè)計(jì)

MAX5882 14位,4.6Gsps下行電纜直接RF-DAC

AD9910: 1 GSPS、14位、3.3 V CMOS直接數(shù)字頻率合成器

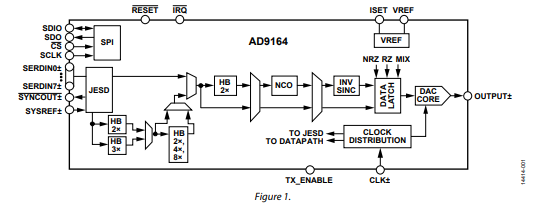

AD9164:16位、12 GSPS、RF DAC和直接數(shù)字合成器數(shù)據(jù)表

AD9175:雙11位/16位12.6 GSPS RF DAC,帶寬帶通道器產(chǎn)品手冊

AD9172:帶通道器的雙16位12.6 GSPS RF DAC產(chǎn)品手冊

AD9174:雙16位12.6 GSPS RF DAC和直接數(shù)字合成器數(shù)據(jù)表

AD9176:帶寬帶通道器的雙16位12.6 GSPS RF DAC產(chǎn)品手冊

UG-475:評估采用14位DAC的AD9912 1 GSPS直接數(shù)字頻率合成器

AD9174雙路、16位、12.6 GSPS RF DAC和直接數(shù)字頻率合成器技術(shù)手冊

AD9164 16位、12 GSPS、RF DAC和直接數(shù)字頻率合成器技術(shù)手冊

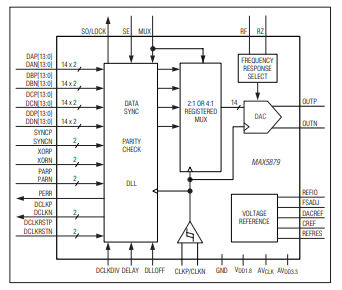

MAX5879 14位、2.3Gsps直接RF合成DAC,提供可選擇頻響技術(shù)手冊

MAX5882 14位、4.6Gsps電纜下行RF直接合成DAC技術(shù)手冊

MAX5882 14位、4.6Gsps電纜下行RF直接合成DAC技術(shù)手冊

評論