小數分頻是頻率合成中的一項新技術。這種技術的特點是使單環鎖相頻率合成器的平均分頻比變為小數。通過使分頻比變為小數,可獲得任意小的頻率間隔,實現高頻率分辨力的頻率合成,利用小數分頻技術完成的小數分頻頻率合成器,不僅頻率分辨力高,而且頻率轉換速度快,還可使頻譜改善、線路簡化、體積縮小、程控方便、集成容易。

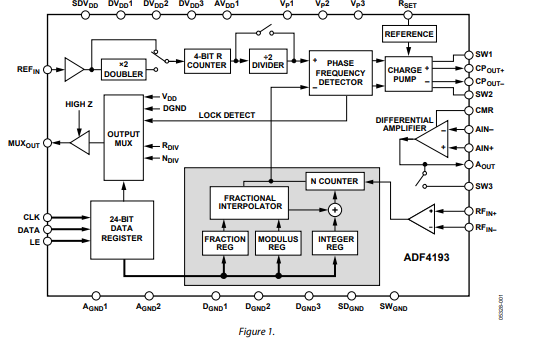

在數字移動通信系統的設計過程中,經常采用跳頻方法來提高通信系統的抗干擾、抗多徑衰落能力。但這要求快速跳頻系統中的超快速跳頻PLL能夠在幾十微秒(μs)內穩定到所要求的相位和頻率。為達到這個要求,可采用"乒乓"體系結構。但這種結構需要兩個頻率合成器。其中當一個頻率合成器作為LO工作時。另一個頻率合成器的作用是鎖定下一步要求的頻率。而現在。也可以用一個快鎖芯片來實現。美國ADI公司生產的ADF4193快速開關頻率合成器就是采用一個PLL的快鎖芯片。它能滿足"乒乓"結構的切換指標,故可用在無線發射機和接收機的上變頻和下變頻電路的LO電路中。

1 ADF4193的特點和PLL工作原理

ADF4193是基于小數分頻的快鎖芯片。該芯片的主要特點如下:

◇ 具有快速調整的小數-N鎖相環結構;

◇ 可用單片鎖相環代替開關式合成器;

◇可在GSM頻帶內實現5μs跳頻,并可在20μs內使相位穩定;

◇ 2GHz輸出時具有0.5級的相位誤差;

◇ 可編程輸出相位;

◇ 射頻輸入范圍可達3.5 GHz;

◇ 帶有3線串行接口;

◇ 芯片內置低噪聲差動放大器;

◇ 其相位噪聲靈敏度可達-216 dBc/Hz.

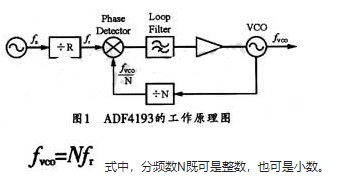

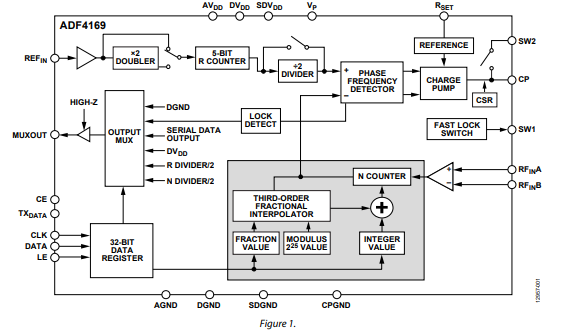

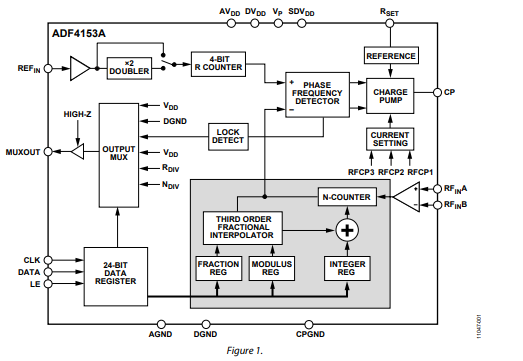

ADF4193主要是基于"乒乓"體系結構的跳頻原理。ADF4193的工作原理如圖1所示,圖中,VCO的作用是提供一個參考頻率fx,fx經過預分頻R得到鑒相器輸入端的參考頻率,圖1中的環路濾波器的作用是濾除鑒相器輸出信號的高頻成分和噪聲,并將鑒相器的輸出電流轉化為電壓送到VCO的輸入端。以控制VCO的輸出頻率。同時將VCO輸出頻率經過N分頻后反饋給鑒相器。鑒相器的作用是對反饋頻率和參考鑒相頻率進行比較,當鑒相器兩個輸入信號的相位同步(且fvco/N=fr)時,VCO的輸出頻率就是要鎖定的頻率。

2 分頻器對PLL的指標影響

2.1 相位噪聲

一般情況下,分頻器的分頻比N對PLL的有關指標的影響比較大。這里主要介紹其對相位噪聲、鎖定時間的影響。影響相噪的因素通常有分頻比、鑒相頻率、PLL固有底噪和閉環傳遞函數等。其近端帶內相噪的大小可用下式表示:

式中,PN/Hz表示PLL的固有底噪,N為分頻比,fcomp為鑒相比較頻率;

從(2)式可以看出,在通帶內,相噪主要由鑒相器決定,當鑒相頻率fcomp增大一倍時,對應值減小一半,輸出頻率保持不變,其相噪可改善了3dB.所以,為了減小通帶內的相噪,設計時應該盡量使用分頻比比較小的PLL.

2.2 鎖定時間

鎖定時間和閉環帶寬有很大關系,環路帶寬越大,鎖定時間越短,環路帶寬越小,鎖定時間越長。對于2階環,其鎖定時間T∝1/ωξ(其中ω為環路帶寬,ξ為阻尼系數)。所以,一般情況下,可以通過改變環路帶寬的值來改變鎖定時間。

對于整數分頻來說,環路帶寬的選取最多只能是參考頻fr的1/10.所以,僅靠環路帶寬來改變鎖定時間的方法有其很大的局限性。

對于小數分頻,環路帶寬的選取基本上和參考頻率fr的關系很小,小數分頻的參考頻率可以選的很大,如ADF4193的fr可選為13MHz.如果1/10按來計算,環路帶寬可以寬到1.3MHz,所以小數分頻的環路帶寬的選取幾乎可以不考fr.

雖然環路帶寬越寬,鎖定時間越短,但是,也不能把環路帶寬設置的特別大,因為環路帶寬越大,濾波效果越差,這樣,PLL輸出頻率的底噪就越高。

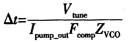

在環路鎖定的情況下,參考時鐘和再生時鐘通常都存在固定的相位差,若將相差假設為△t,則其相位誤差計算公式如下:

其中:Vtune是VCO或VCXO的調諧端電壓,單位V;Ipump_out為鑒相器的輸出鑒相電流,單位mA;Fcomp表示鑒相頻率,單位kHz;ZVCO是VCO或VCXO的輸入阻抗,單位歐姆。

由式(3)此可以看出,要使參考時鐘和再生時鐘的相位差盡量小,起主要作用因素的是系統的鑒相頻率和振蕩器的輸入阻抗要足夠大。△t的范圍與鎖定是密切相關的。大多數的PLL芯片都要求在鎖定時刻,其連續3個或5個鑒相周期的絕對相位誤差要小于15ns,否則即視為失鎖。具體選取3個還是5個鑒相周期,可通過相應的寄存器來設置。在鎖定期間,任一周期的相位誤差大于25ns,即為失鎖。

一般情況下,環路帶寬、鎖定時間和相位噪聲會相互影響、相互制約。要獲得較短的鎖定時間,就需要較大的環路帶寬,但也會引入更多的噪聲,因而有可能導致相位噪聲的惡化。同樣,如果需要良好的相位噪聲,則環路帶寬就要變窄,此時的鎖定時間就會增加。如果想在不改變環路帶寬的情況下改善相位噪聲,根據公式(2),可在分頻器Ⅳ和鑒相頻率Fcomp做一些改善。

3 FPGA對ADF4193的配置過程

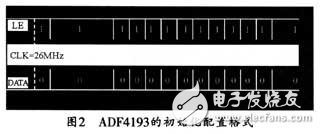

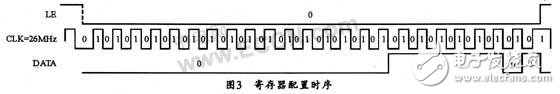

通過Verilog語言進行編程,可用FPGA來實現對ADF4193的配置。ADF4193中有八個寄存器,通過對這八個寄存器的配置,可以使ADF4193進入正常工作狀態。ADF4193有一個3線串行接口,這三個接口分別為LE、CLK、DATA.數據可在時鐘的上升延從ADF4193的3線串行接口輸入到24-bit的輸入移位寄存器,高字節在前。在使能信號LE的上升延,移位寄存器的數據將被鎖入到8個寄存器R0~R7的其中之一。具體寫給哪個寄存器,可由移位寄存器的24-bit最低位的三個控制比特c3、c2、c1來決定。

按照一定的方式將初始化配置數據發送到ADF4193對應的寄存器,即可實現ADF4193的初始化。圖2所示是用邏輯分析儀抓到的配置圖。

圖2給出了ADF4193的17步配置過程。其中寄存器R0和R2的值決定了鎖相環的輸出頻率。圖2中,在配置完前兩個寄存器后,還需要等待10ms的時間,以便環路濾波器的電容能夠放電。通過這樣的配置可以將ADF4193配置在任何一個需要的頻率上。需要說明的是,只有當初始化過程穩定,才可以進行跳頻操作。否則,ADF4193將無法進行正常的跳頻功能。

對應圖2,即可得到第一個被配置的寄存器的配置時序,其具體的時序圖如圖3所示。

從圖3可見,給一個寄存器配置數據可通過LE信號進行控制。在LE為低電平時。恰好有24個時鐘周期卡在LE的前一個下降延和后一個上升延之內。從數據的后三位可以看出,這次配的寄存器是R5.其它寄存器的配置過程為此相同。

4 PLL指標的測量

4.1 相噪的測量

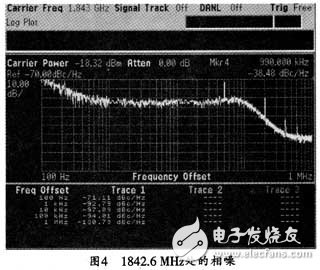

利用儀表的相噪模板可對ADF4193的輸出相噪進行測量。其測量結果如圖4所示。

從圖4可以看到,FreqOffset在:100Hz、1kHz、10kHz、100kHz和1MHz處都可以達到很好的指標。

4.2 鎖定時間的測量

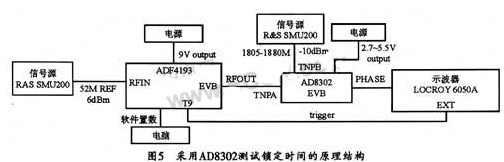

為了節約成本,可以采用ADI公司提供的AD8302并結合示波器對鎖定時間進行測量,基于AD8302的測量原理結構如圖5所示。

實際使用證明,ADF4193的鎖定時間可以達到所需要的指標。此外,采用FPGA來實現對ADF4193的配置,其過程相對比較簡單且易實現,而同時性能也能得到保證。

5 結語

由ADF4193的配置時序可以看出,ADF4193是一款易配置和使用的芯片,使用它可以簡化設計復雜度,縮短項目調試周期。從測量的相位噪聲和鎖定時間的結果可以看出:ADF4193具有很好的性能指標,而且穩定性比較好。ADF4193的最主要的優點是可以簡單的實現跳頻,它不再需要使用"乒乓切換"電路,因而可縮短系統的切換時間,以在時隙的保護時間內實現頻率切換。ADF4193比"乒乓切換"電路更能簡化電路,減少成本,同時可節省PCB的布板面積。很適合在通信系統中使用。

-

FPGA

+關注

關注

1645文章

22028瀏覽量

617706 -

芯片

+關注

關注

459文章

52446瀏覽量

439862 -

pll

+關注

關注

6文章

888瀏覽量

136326

發布評論請先 登錄

小數分頻頻率合成器的實現方法

ADF4193 低相位噪聲、快速建立PLL頻率合成器

ADF4169直接調制/快速波形產生13.5 GHz小數N分頻頻率合成器技術手冊

ADF4153A小數N分頻頻率合成器技術手冊

ADF4193低相位噪聲、快速建立PLL頻率合成器技術手冊

小數分頻技術與ADF4193快速開關頻率合成器的研究

小數分頻技術與ADF4193快速開關頻率合成器的研究

評論