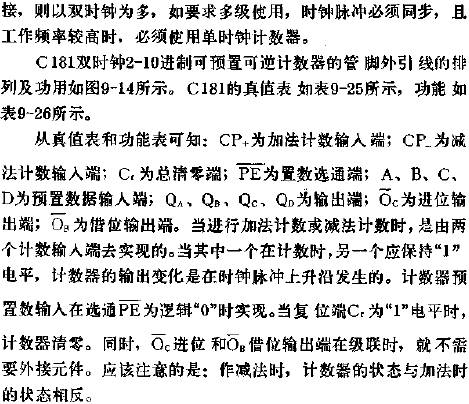

計數器是數字系統中用得較多的基本邏輯器件。它不僅能記錄輸入時鐘脈沖的個數,還可以實現分頻、定時、產生節拍脈沖和脈沖序列等。例如,計算機中的時序發生器、分頻器、指令計數器等都要使用計數器。 計數器的種類很多。按時鐘脈沖輸入方式的不同,可分為同步計數器和異步計數器;按進位體制的不同,可分為二進制計數器和非二進制計數器;按計數過程中數字增減趨勢的不同,可分為加計數器、減計數器和可逆計數器。

2進制計數器設計方案一

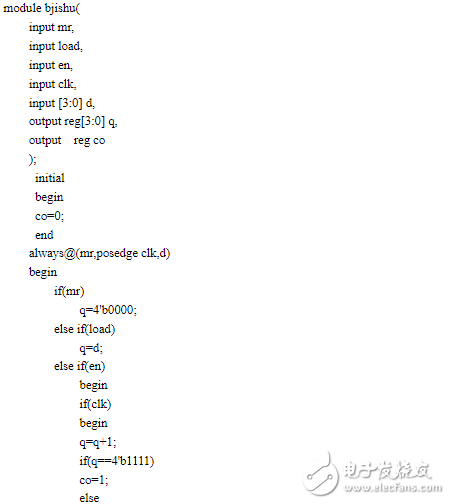

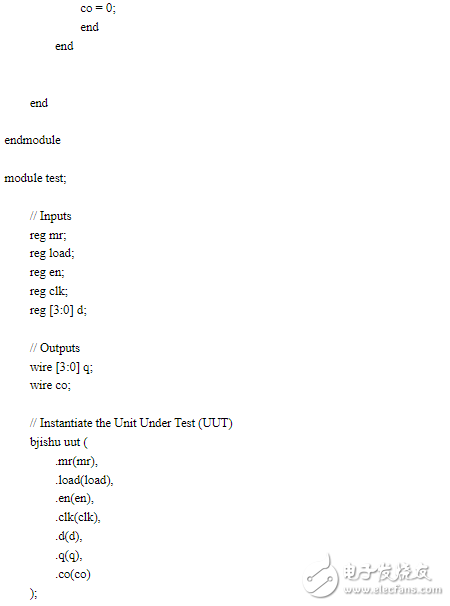

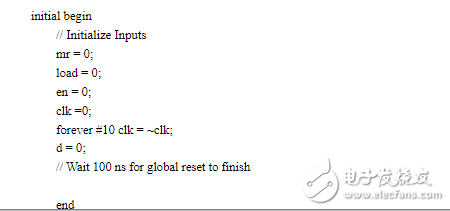

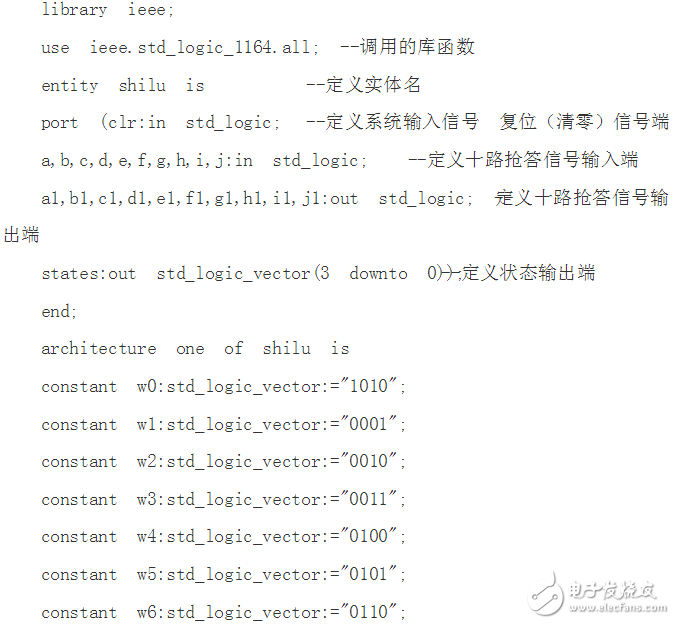

程序源代碼

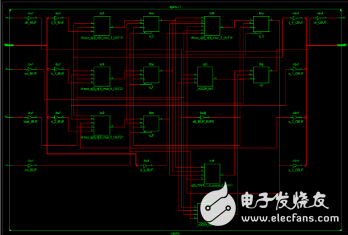

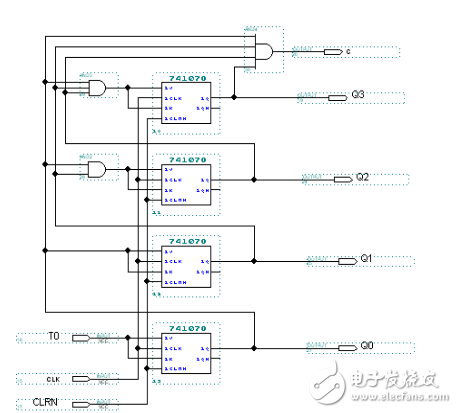

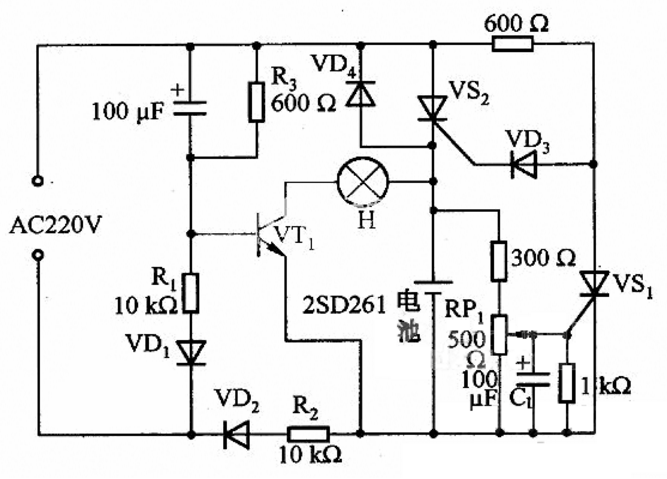

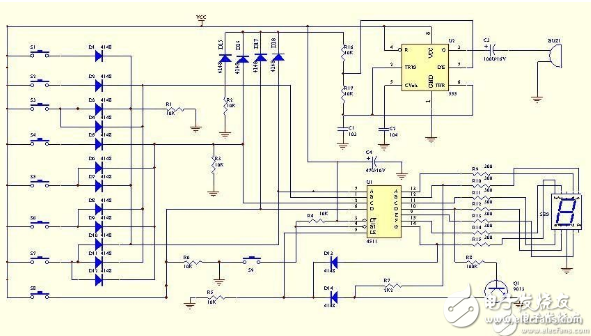

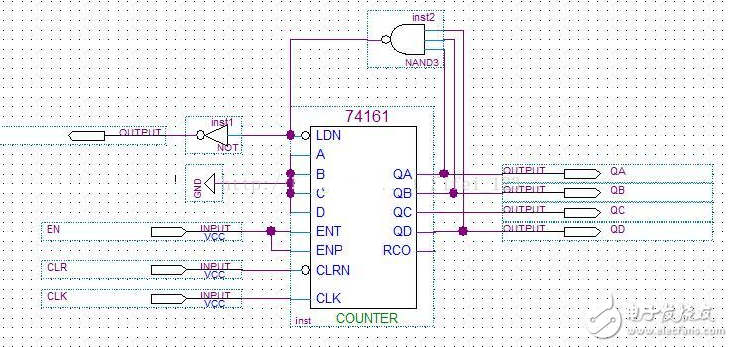

電路圖

2進制計數器設計方案二

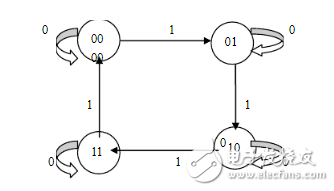

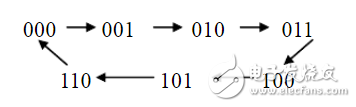

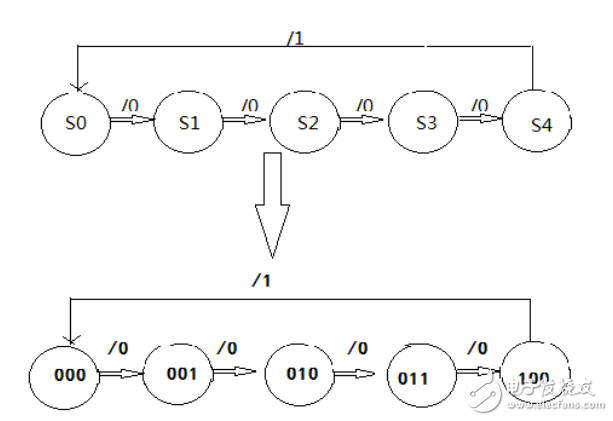

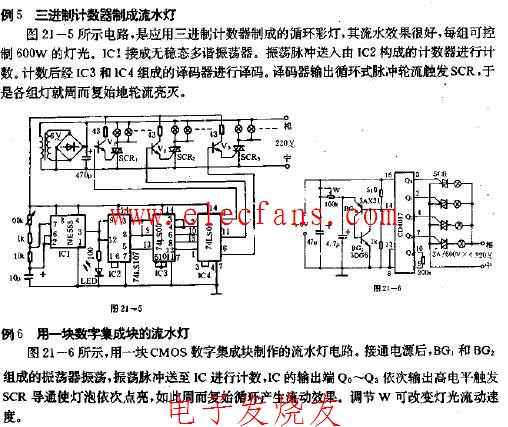

原始狀態圖

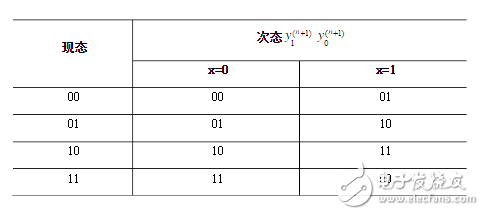

二位二進制計數器狀態表

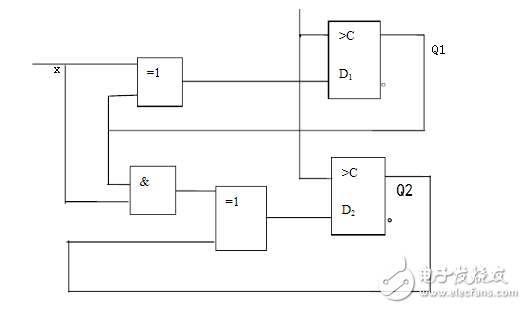

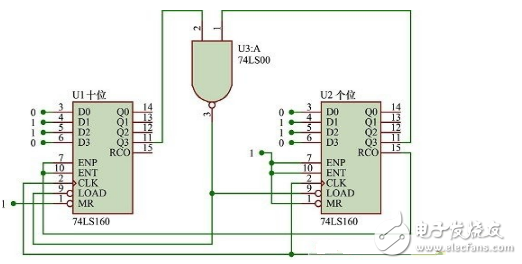

邏輯電路圖

2進制計數器設計方案三

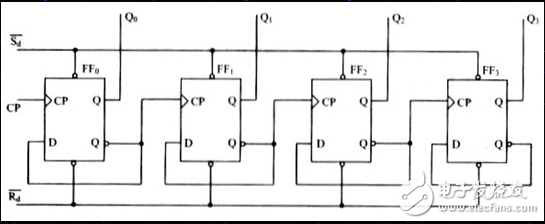

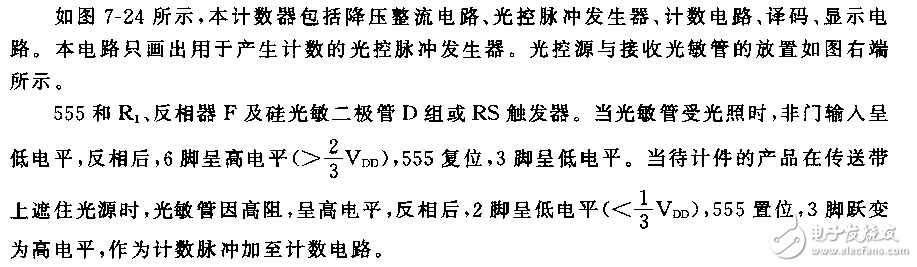

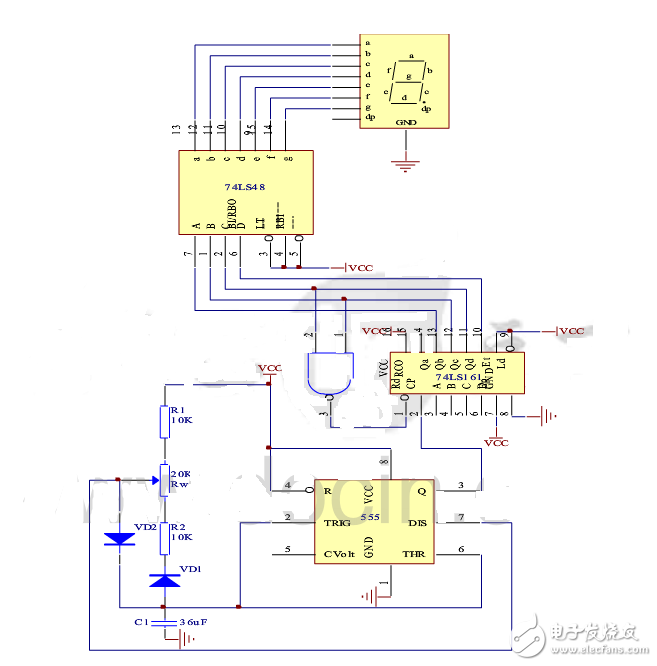

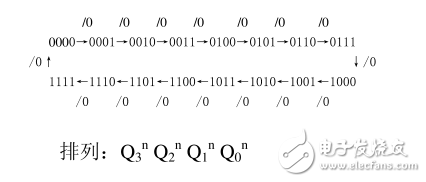

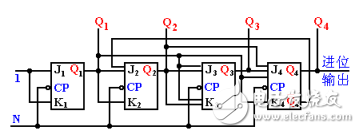

觸發器構成的同步二進制加法計數器

觸發器構成的同步二進制加法計數器

2進制計數器設計方案四

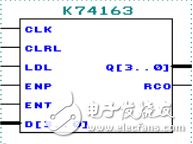

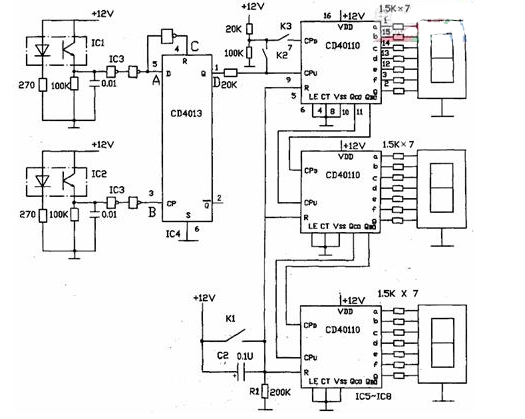

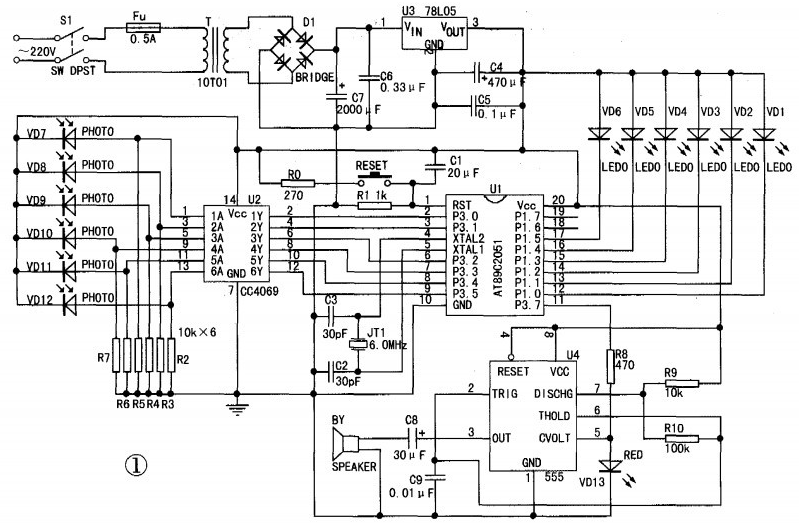

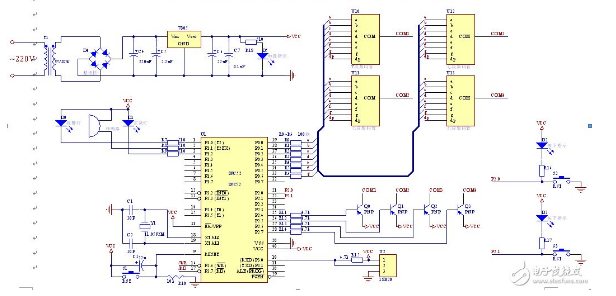

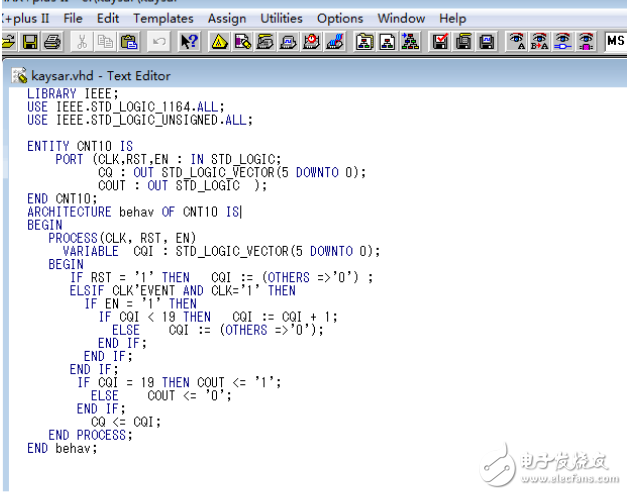

采用VHDL語言設計一個4位二進制計數器74163,它具有同步清零、同步置數、計數控制和進位輸出控制功能。如下圖所示。

4位二進制計數器74163

各端口功能

CLK:時鐘信號,上升沿計數;

CLRL:同步清零端,低電平有效;

LDL:同步置位控制端,低電平有效;

ENP:與ENT同時為‘1’時,計數使能;

ENT:為‘1’時,可進行進位;

D[3..0]:計數器置數輸入;

Q[3..0]:計數器狀態輸出;

RCO:計數器進位輸出。

程序設計

2進制計數器設計方案五

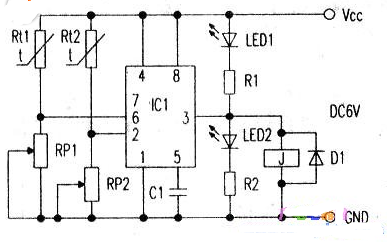

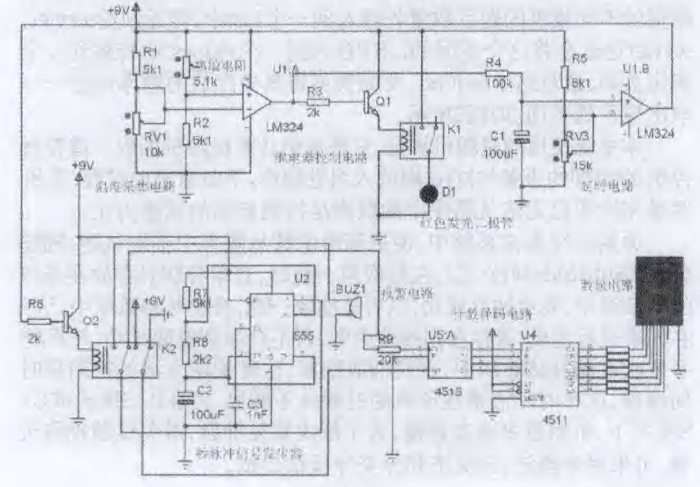

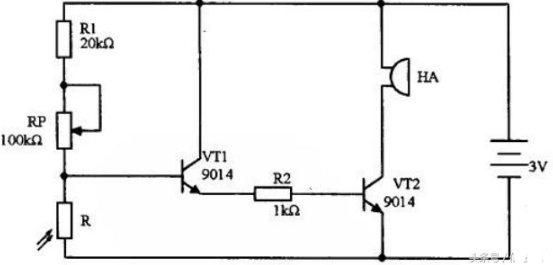

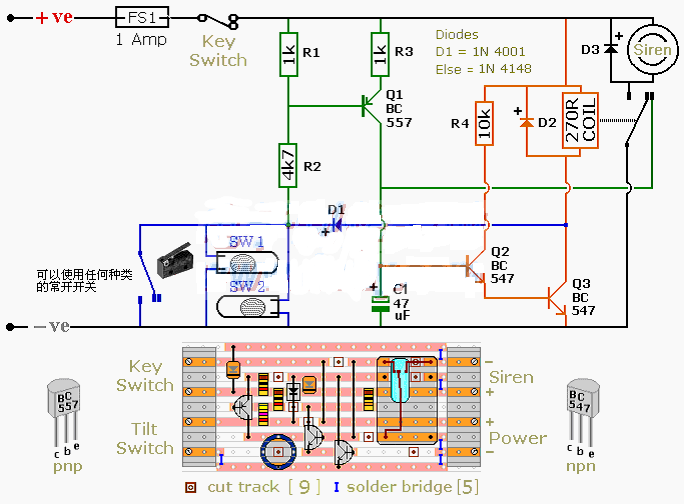

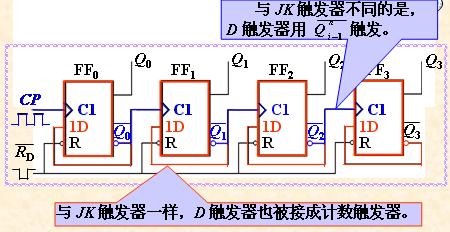

用觸發器組成計數器。觸發器具有0 和1兩種狀態,因此用一個觸發器就可以表示一位二進制數。如果把n個觸發器串起來,就可以表示n位二進制數。對于十進制計數器,它的10個數碼要求有10個狀態,要用4位二進制數來構成。下圖是由D觸發器組成的4位異步二進制加法計數器。

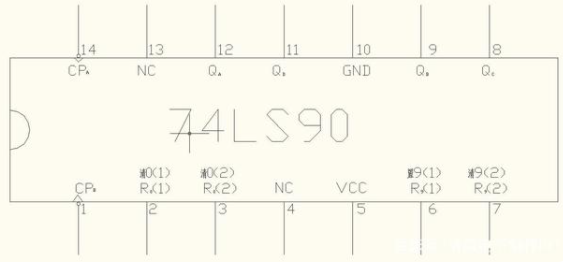

布線

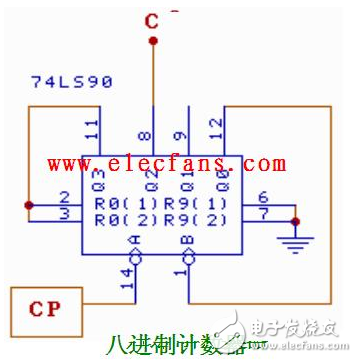

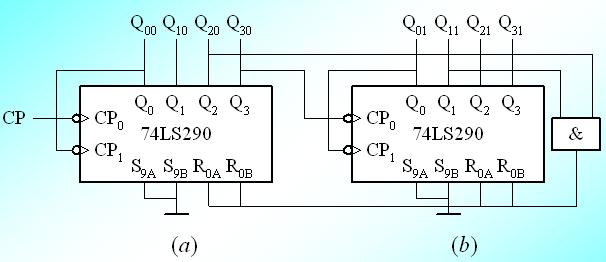

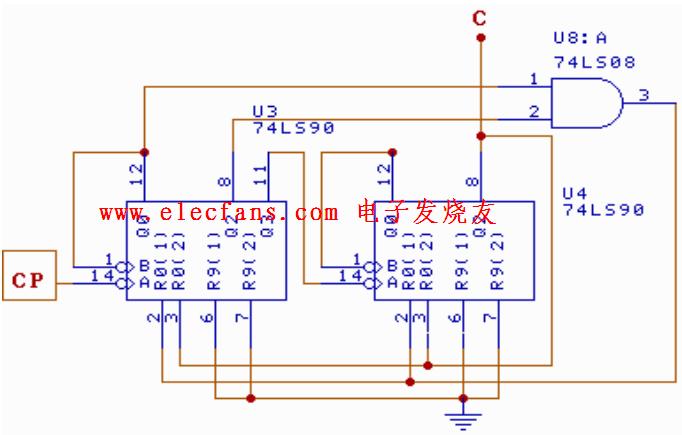

1、將芯片(1)的引腳4、10連到一起,

2、將芯片(2)的引腳4、10連到一起,

3、將芯片(1)的引腳10和芯片(2)的引腳10連到一起,

4、將芯片(1)的引腳10連到+5V;

5、將芯片(1)的引腳1、13連到一起,

6、將芯片(2)的引腳1、13連到一起,

7、將芯片(1)的引腳13和芯片(2)的引腳13連到一起,

8、將芯片(1)的引腳13連到+5V;

9、將芯片(1)的引腳3接到時鐘信號CP

10、將芯片(1)的引腳2、6接到一起,再將引腳2接到引腳11

11、將芯片(1)的引腳8、12接到一起,再將芯片(1)的引腳8接到芯片(2)的引腳3

12、將芯片(2)的引腳2、6接到一起,再將引腳6接到引腳11

13、將芯片(1)的引腳5、9分別接到Q0、Q1,再將芯片(2)的引腳5、9分別接到Q2、Q3

14、分別將兩芯片的14腳接電源+5V,分別將兩芯片的7腳接地0V。

電子發燒友App

電子發燒友App

評論