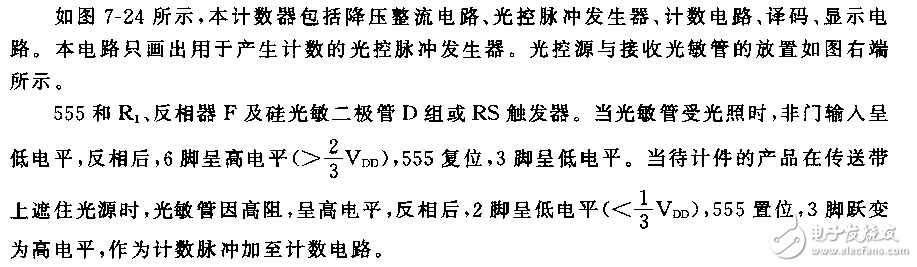

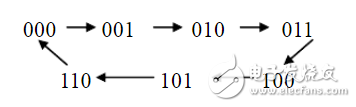

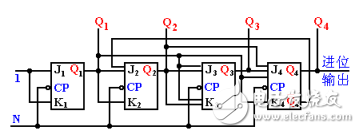

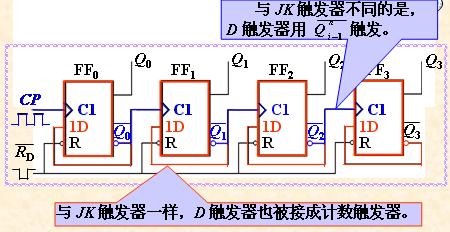

計數(shù)是一種最簡單基本的運算,計數(shù)器就是實現(xiàn)這種運算的邏輯電路,計數(shù)器在數(shù)字系統(tǒng)中主要是對脈沖的個數(shù)進行計數(shù),以實現(xiàn)測量、計數(shù)和控制的功能,同時兼有分頻功能,計數(shù)器是由基本的計數(shù)單元和一些控制門所組成,計數(shù)單元則由一系列具有存儲信息功能的各類觸發(fā)器構(gòu)成,這些觸發(fā)器有RS觸發(fā)器、T觸發(fā)器、D觸發(fā)器及JK觸發(fā)器等。本文為大家?guī)砥叻N任意進制計數(shù)器設(shè)計方案及其電路設(shè)計的原理詳解。

任意進制計數(shù)器設(shè)計方案一:采用反饋置數(shù)法來設(shè)計任意進制計數(shù)器

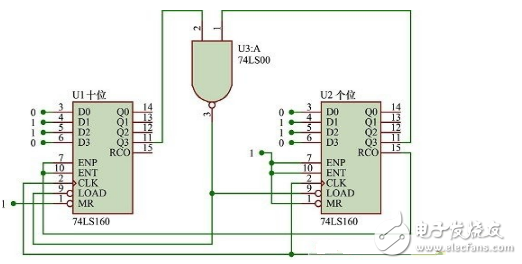

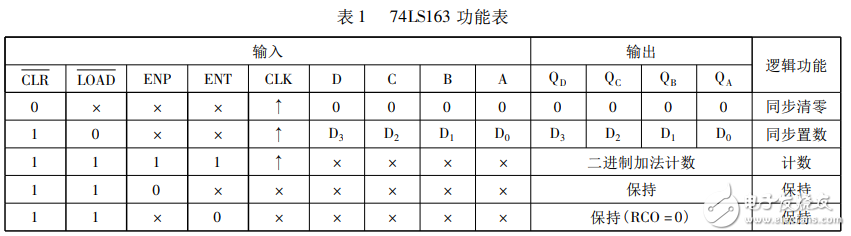

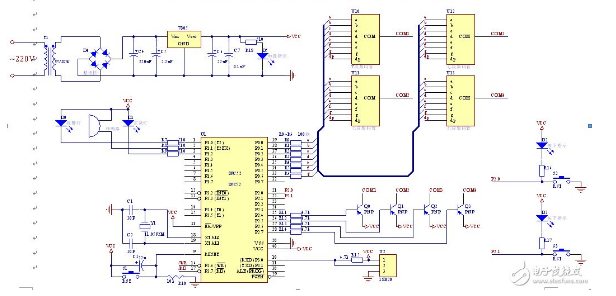

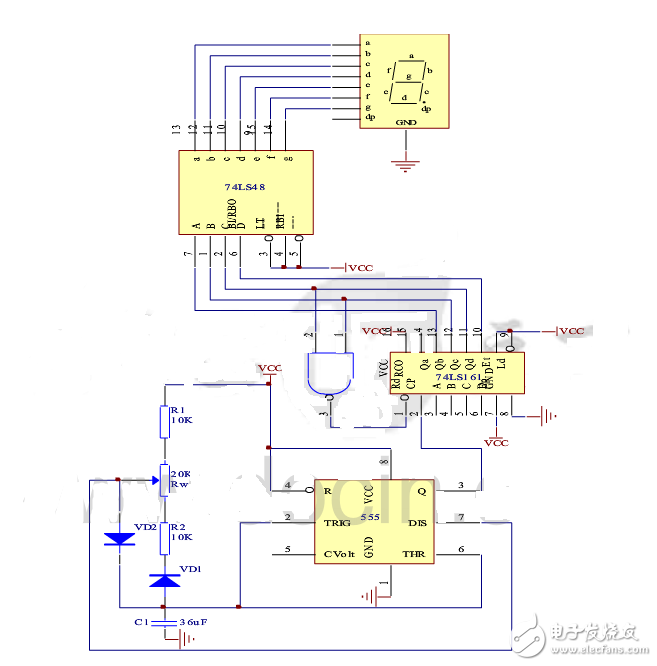

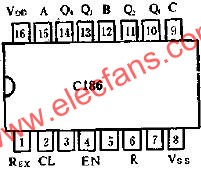

此方法適用于某些具有預(yù)置數(shù)的計數(shù)器,它是采用預(yù)置數(shù)控制端LOAD來實現(xiàn)。對于74LS160屬于同步式預(yù)置數(shù)的計數(shù)器來說,當LOAD出現(xiàn)有效電平低電平后待下一個時鐘脈沖信號到來后計數(shù)器輸出端的狀態(tài)Q3Q2Q1Q0=D3D2D1D0.使其跳過某些狀態(tài)來設(shè)計任意進制計數(shù)器。下面就以74LS160為例,用并行置數(shù)法設(shè)計23進制計數(shù)器,其中預(yù)置數(shù)端D3D2D1D0可以置零,也可以置十以內(nèi)的任意四位二進制數(shù)。那么此電路在其置數(shù)時十位和個位的D3D2D1D0置入(01100110)8421BCD碼=(66)10,而反饋代碼十位和個位為(10001000)8421BCD碼=(88)10,相當于十進制數(shù)的88.由此分析可得到計數(shù)器的模為(88-66)+1=23,故計數(shù)器為23進制計數(shù)器,其設(shè)計電路圖如圖5所示。由此可以得到置數(shù)法的設(shè)計要點為:反饋代碼轉(zhuǎn)換成的十進制數(shù)-預(yù)置數(shù)端的代碼轉(zhuǎn)換成的十進制數(shù)+1=所設(shè)計的計數(shù)器的模。

任意N進制計數(shù)器的設(shè)計方法及步驟

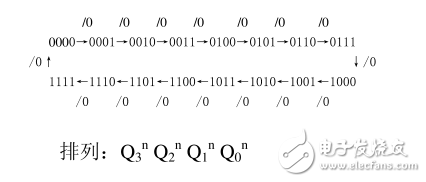

(1)根據(jù)計數(shù)模N來確定所需要計數(shù)器芯片的個數(shù)n.n=INT(logm(N-1))+1,INT表示取整。m:當芯片為十進制計數(shù)器時m取10,當芯片為四位二進制計數(shù)器時m取16.

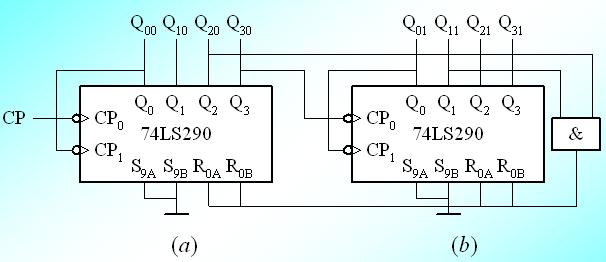

(2)當n個計數(shù)器芯片連接成模為m的計數(shù)器

(3)選用并行法或串行法將n個計數(shù)器連接起來。

(4)確定反饋置零代碼。如果計數(shù)器芯片采用異步置零反饋代碼為(N)10,若是采用同步置零,則反饋代碼為(N??1)10.

(5)反饋置零代碼形式的轉(zhuǎn)換。如果芯片為十進制制計數(shù)器,將反饋代碼轉(zhuǎn)換成8421BCD碼的形式。若是四位二進制計數(shù)器,則將反饋代碼轉(zhuǎn)換成二進制數(shù)。

(6)將轉(zhuǎn)換結(jié)果與計數(shù)器的狀態(tài)輸出端進行比較,讓與1對應(yīng)的引腳作用到與非門(反饋置零端低電平有效)或者與門(反饋置零端高電平有效)的輸入端,然后將與非門或者與門的輸出,連接到計數(shù)器芯片的反饋置零端即可。

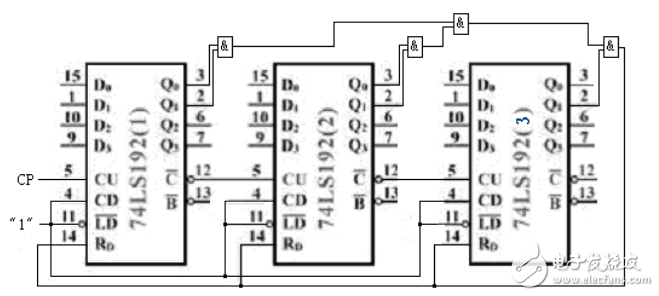

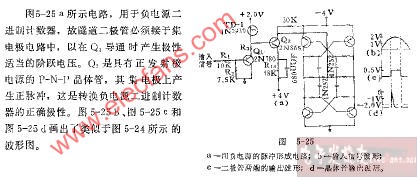

任意進制計數(shù)器設(shè)計方案二:采用清零法來設(shè)計任意進制計數(shù)器

CR(RD)=(Q1Q0)百(Q1Q0 )拾(Q1)個 初態(tài):0000

終態(tài):233-1=232即:0010 0011 0010

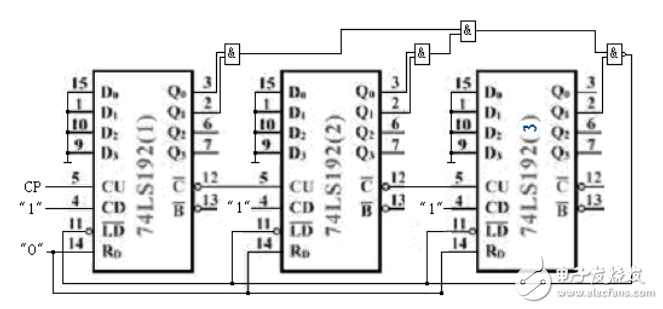

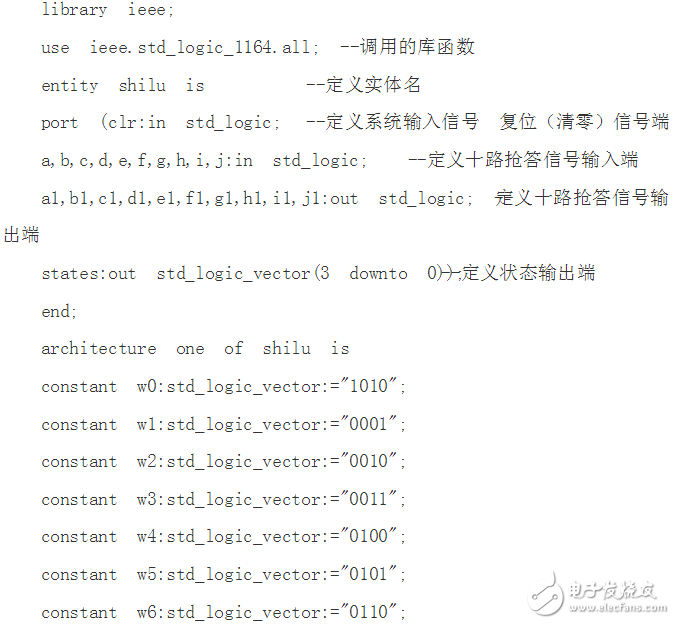

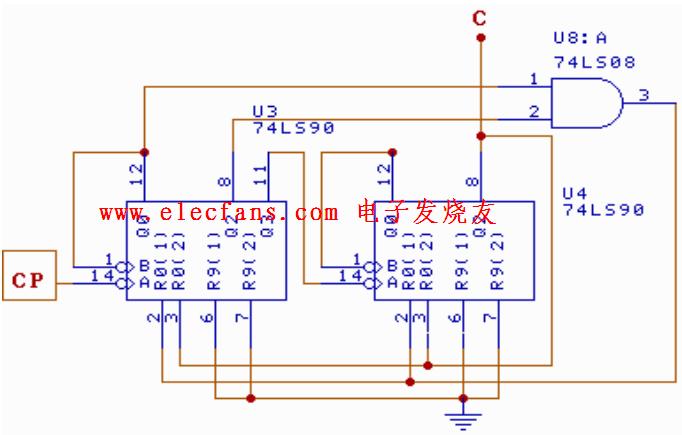

任意進制計數(shù)器設(shè)計方案三

LD=(Q1Q0)百(Q1Q0 )拾(Q2Q0)個 (或LD=CO)

初態(tài):0000 (或1000-332=668)

終態(tài):332-1=331即:0011 0011 0001 (或999)

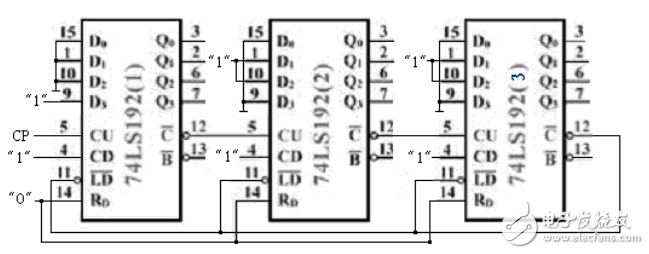

任意進制計數(shù)器設(shè)計方案四:采用置數(shù)法來設(shè)計任意進制計數(shù)器1

由于74LS192是具有異步清零、置數(shù)功能的十進制計數(shù)器,因此保留哪233種狀態(tài),方法有多種。

任意進制計數(shù)器設(shè)計方案五:采用置數(shù)法來設(shè)計任意進制計數(shù)器2

電子發(fā)燒友App

電子發(fā)燒友App

評論