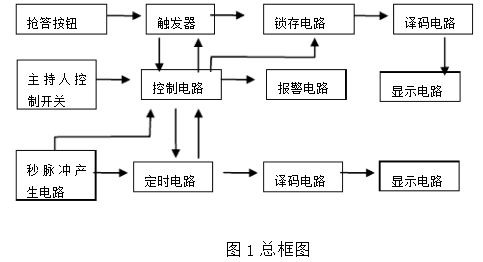

本文為大家介紹三個20進(jìn)制計數(shù)器設(shè)計方案。

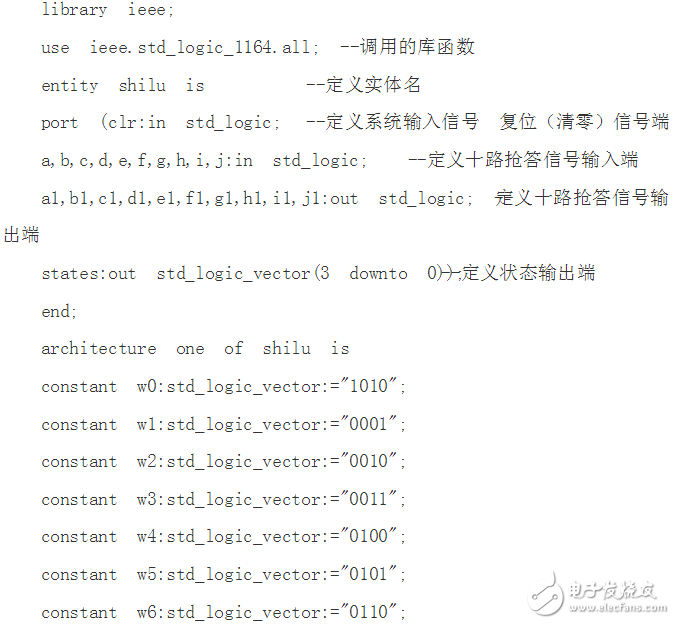

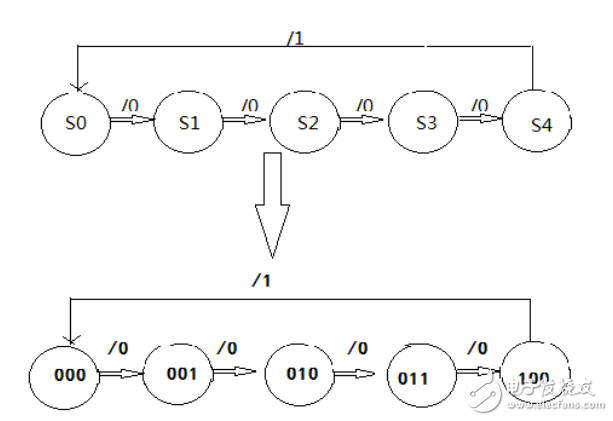

20進(jìn)制計數(shù)器設(shè)計方案一:基于MAX+PLUSⅡ的20進(jìn)制計數(shù)器設(shè)計

創(chuàng)建電路

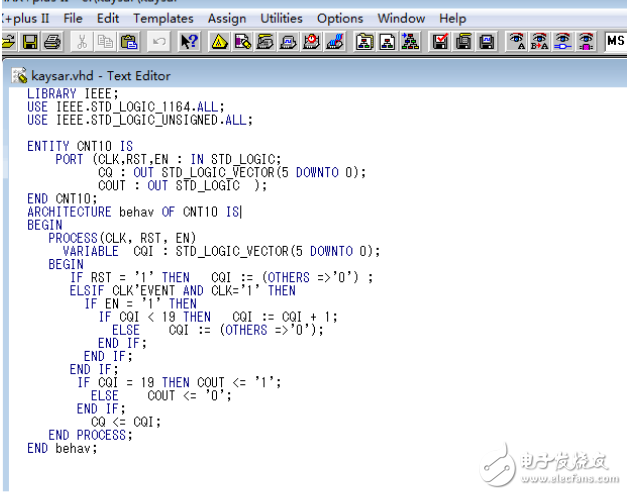

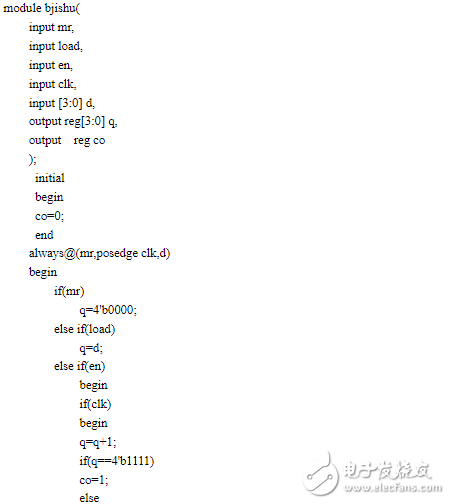

文本圖:

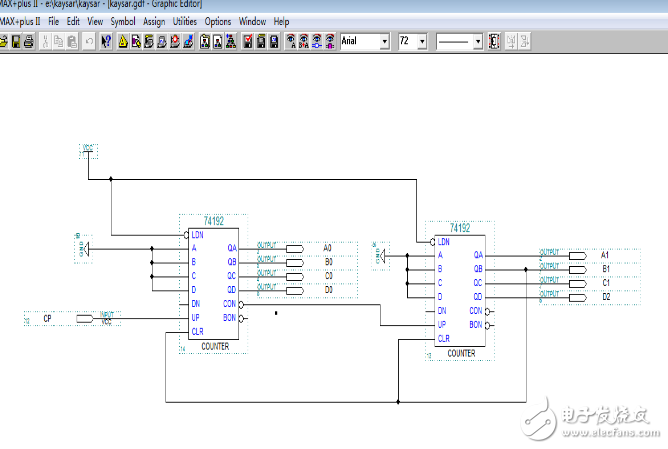

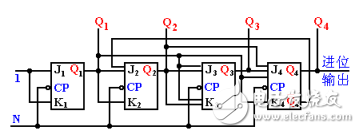

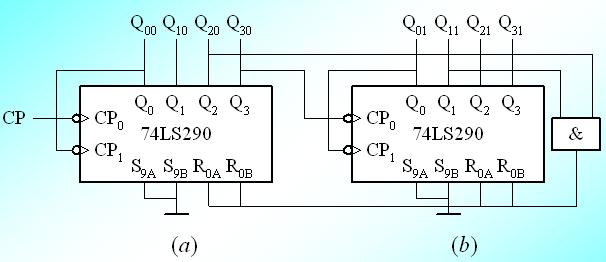

20進(jìn)制計數(shù)器的原理圖

原理圖輸出波形圖

可見當(dāng)LD信號為“1”是不管CLK信號是什么都不工作。只要LD為“0”是才能正常工作。

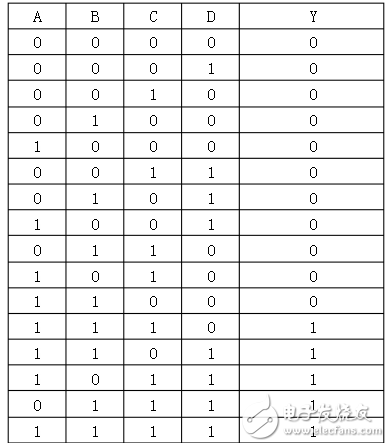

功能表

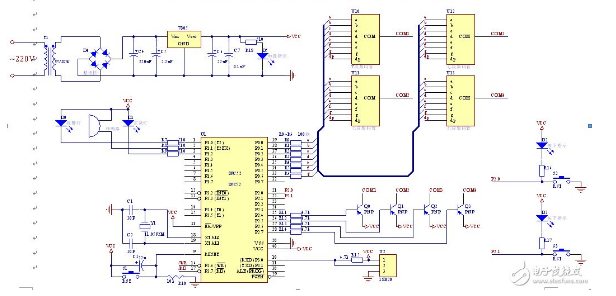

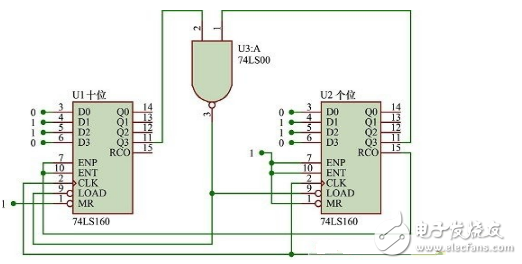

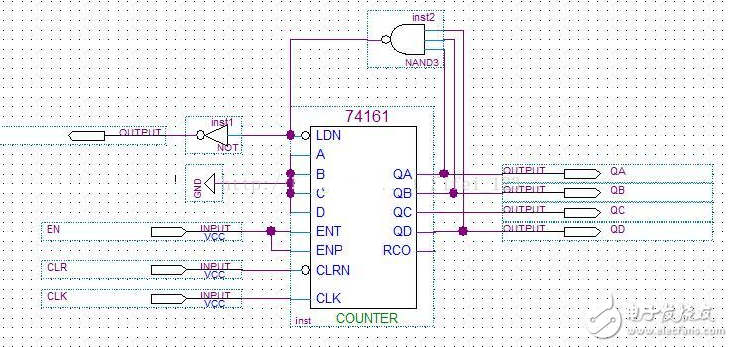

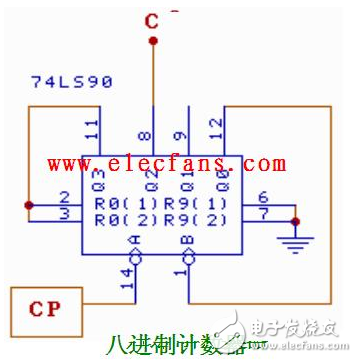

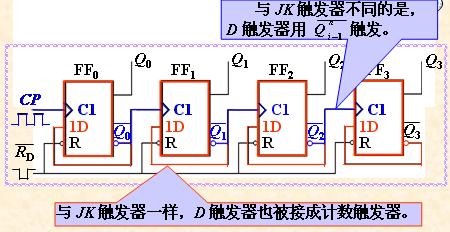

20進(jìn)制計數(shù)器設(shè)計方案二:FPGA利用74161設(shè)計20進(jìn)制計數(shù)器

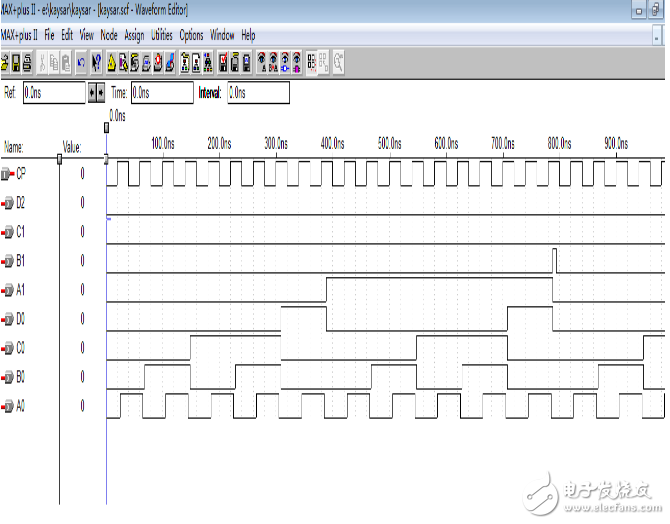

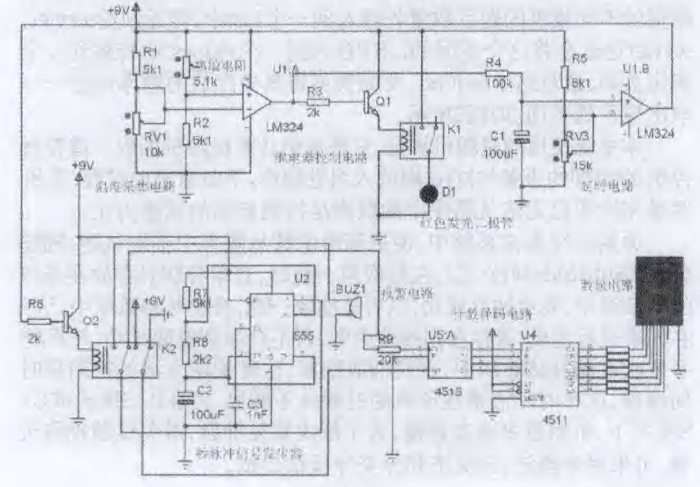

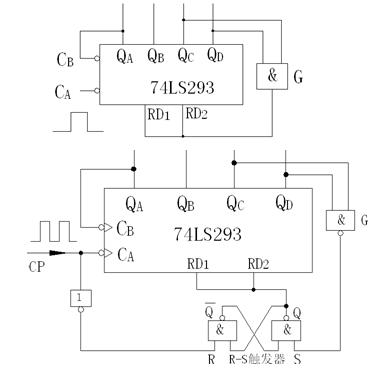

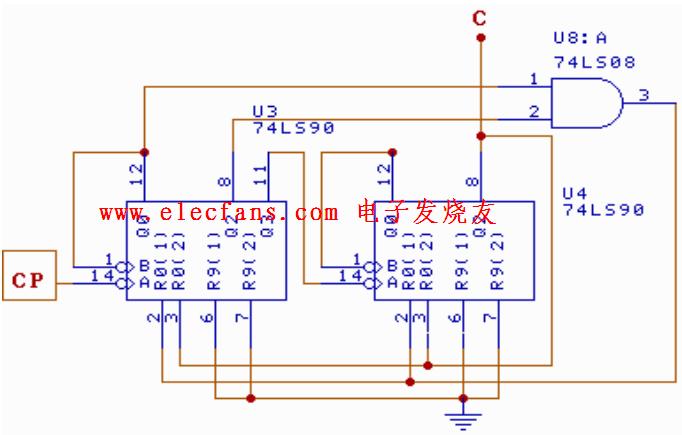

1.首先,建立工程,新建BDF文件,在BDF文件中畫出電路圖,如圖所示:

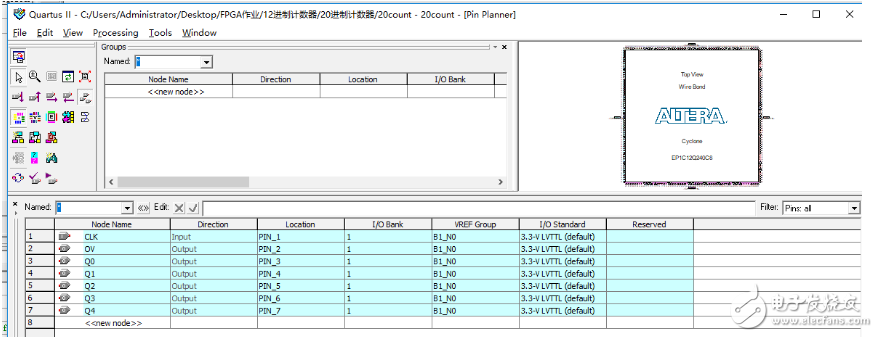

2.由于輸入輸出數(shù)目較少,PIN管腳設(shè)置采用手動輸入的方法,設(shè)置后如圖所示:

然后點擊startcompilcation進(jìn)行編譯,得到如下結(jié)果:

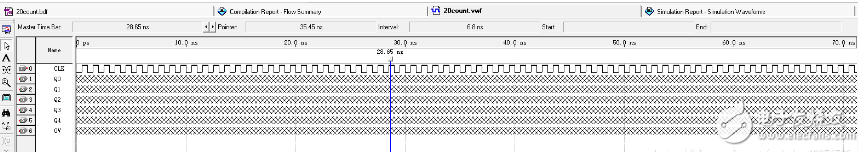

3.最后,進(jìn)行仿真設(shè)計,先新建一個VWF文件,再將nodefinder中的關(guān)鍵引腳拖至仿真區(qū),設(shè)置好仿真時間以及輸入信號,如圖所示:

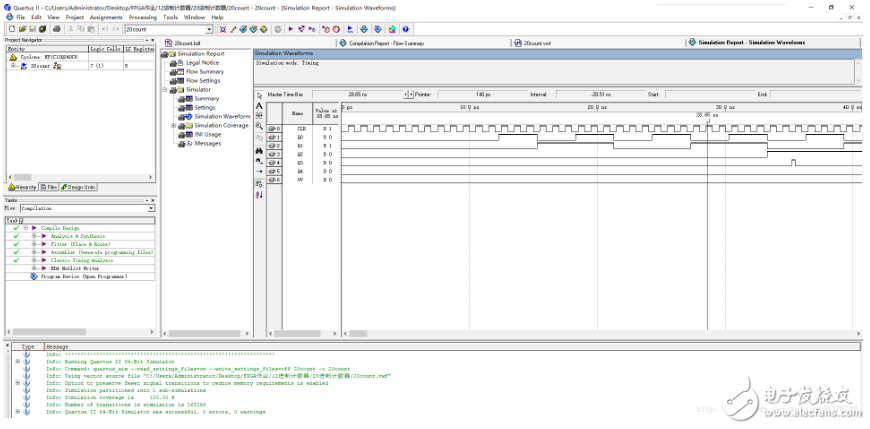

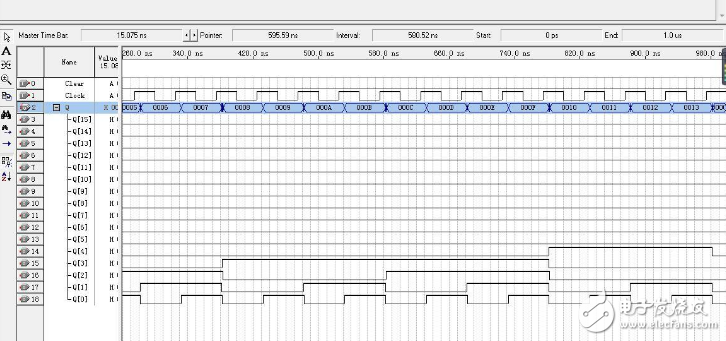

點擊startsimliation進(jìn)行仿真,得到仿真結(jié)果如圖所示:

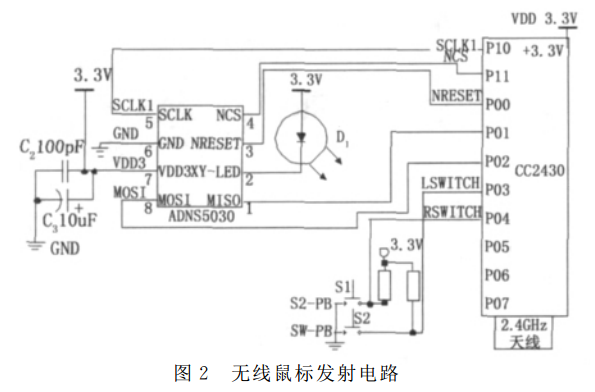

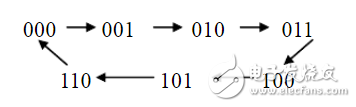

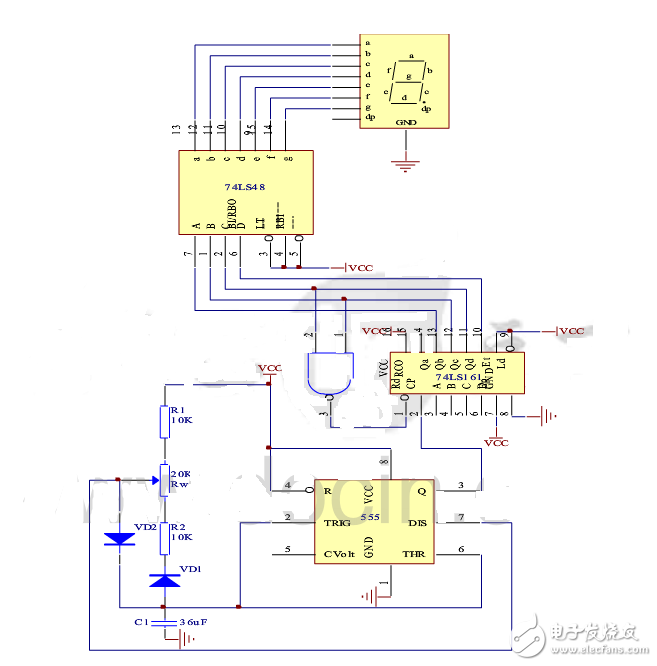

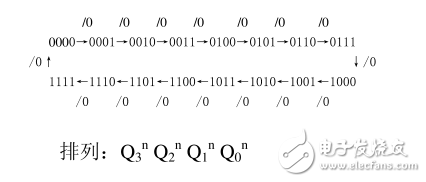

20進(jìn)制計數(shù)器設(shè)計方案三:用verilog語言實現(xiàn)的20進(jìn)制計數(shù)器

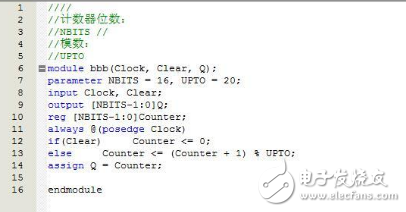

程序設(shè)計

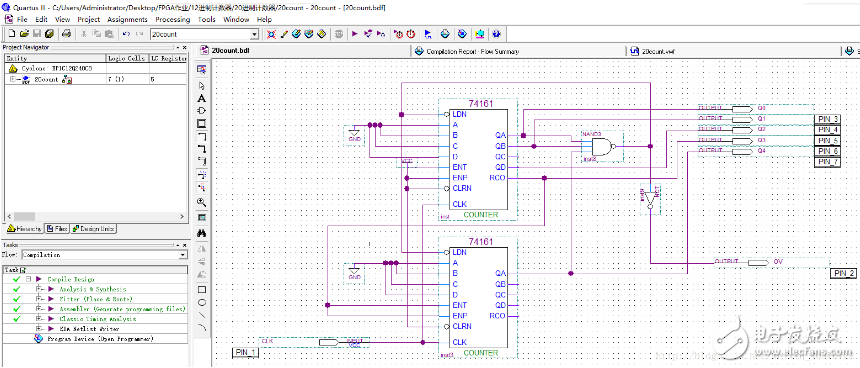

仿真波形

電子發(fā)燒友App

電子發(fā)燒友App

評論