加法器是產(chǎn)生數(shù)的和的裝置。加數(shù)和被加數(shù)為輸入,和數(shù)與進(jìn)位為輸出的裝置為半加器。若加數(shù)、被加數(shù)與低位的進(jìn)位數(shù)為輸入,而和數(shù)與進(jìn)位為輸出則為全加器。常用作計(jì)算機(jī)算術(shù)邏輯部件,執(zhí)行邏輯操作、移位與指令調(diào)用。在電子學(xué)中,加法器是一種數(shù)位電路,其可進(jìn)行數(shù)字的加法計(jì)算。

加法器電路設(shè)計(jì)方案一:BCD加法器的設(shè)計(jì)

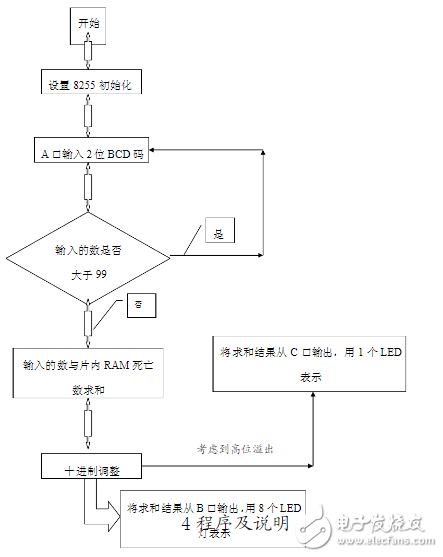

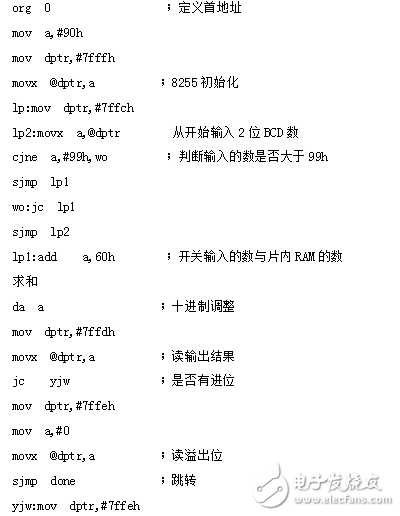

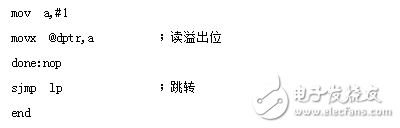

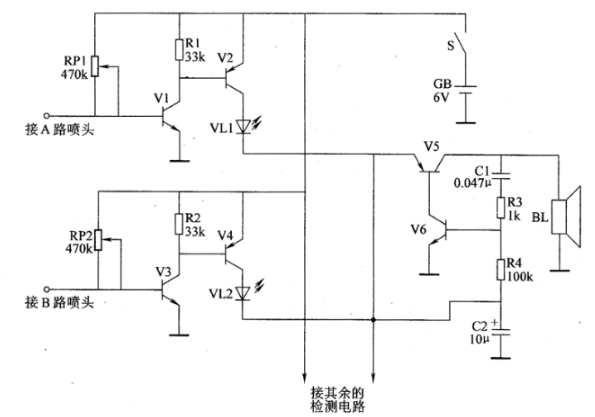

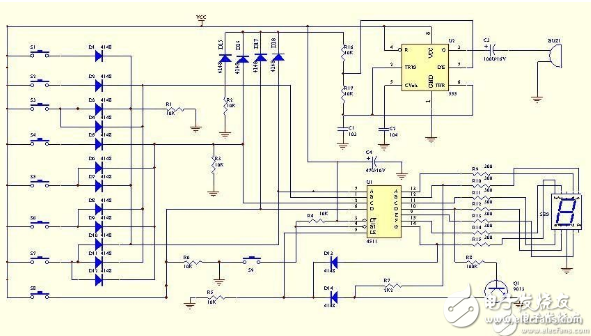

BCD加法器的設(shè)計(jì), 目的是根據(jù)彩燈亮滅的方式,來顯示兩個(gè)BCD碼相加之和。

本設(shè)計(jì)要求考慮高位溢出,無高位溢出時(shí),求和結(jié)果用8個(gè)LED燈顯示,亮的為1,滅的為0,讀出BCD碼轉(zhuǎn)化為十進(jìn)制,即為結(jié)果;若有高位溢出時(shí),第9個(gè)燈亮,所得結(jié)果已超過兩位,通過9個(gè)燈結(jié)合讀出結(jié)果。

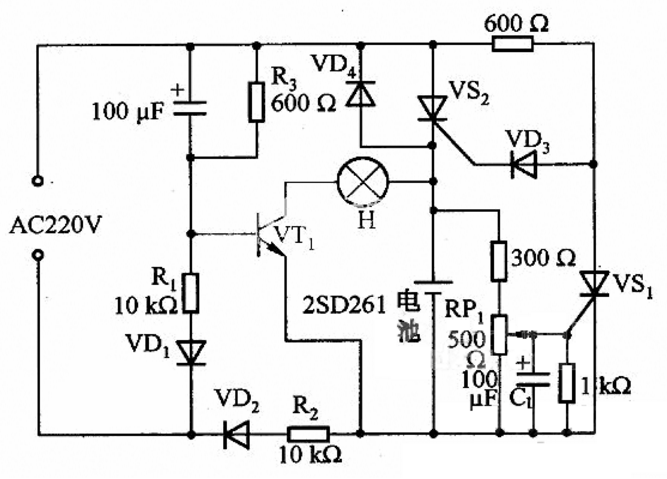

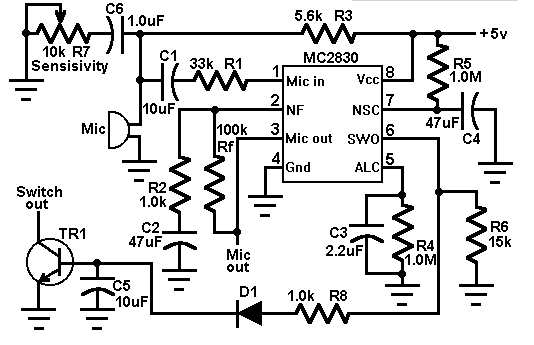

硬件接線圖

程序流程圖

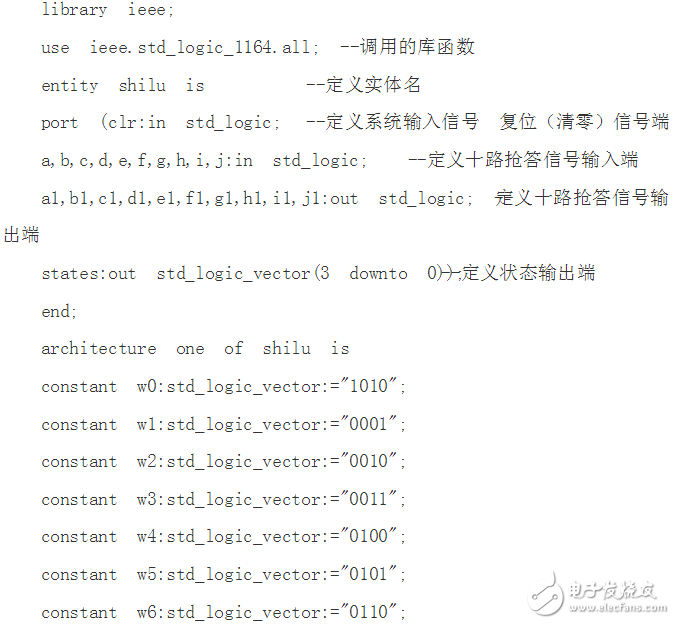

程序設(shè)計(jì)

加法器電路設(shè)計(jì)方案二:8位級(jí)聯(lián)加法器的設(shè)計(jì)

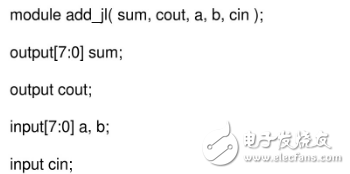

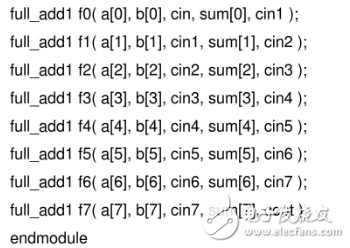

8位級(jí)聯(lián)加法器的設(shè)計(jì)程序

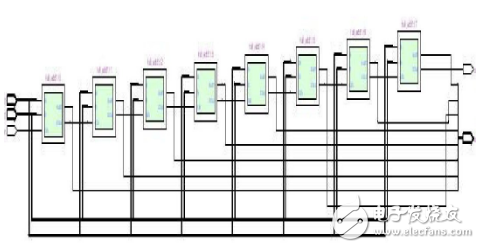

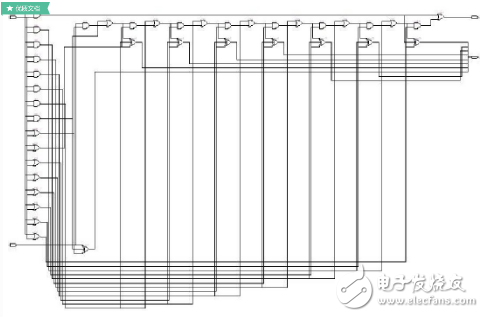

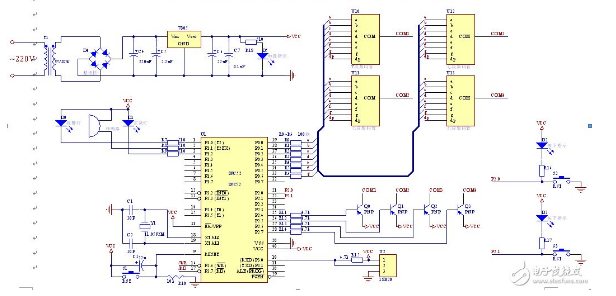

8位級(jí)聯(lián)加法器RTL圖

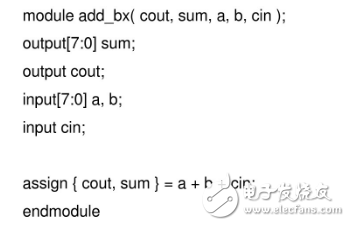

加法器電路設(shè)計(jì)方案三:八位并行加法器設(shè)計(jì)

它的結(jié)構(gòu)為用加法運(yùn)算符描述,由EDA軟件綜合,其優(yōu)點(diǎn)是運(yùn)算速度快。

程序

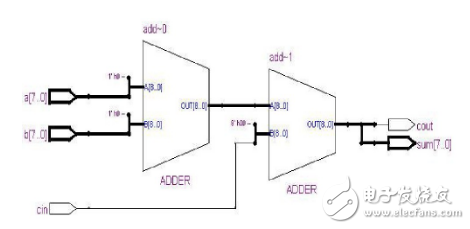

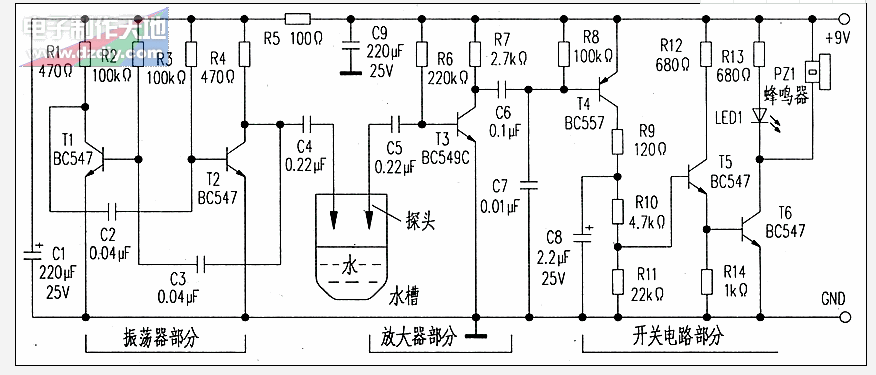

8位并行加法器RTL圖

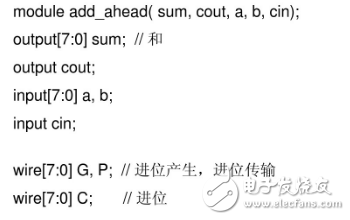

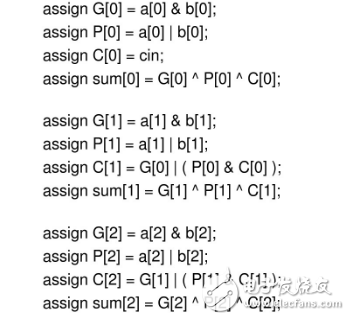

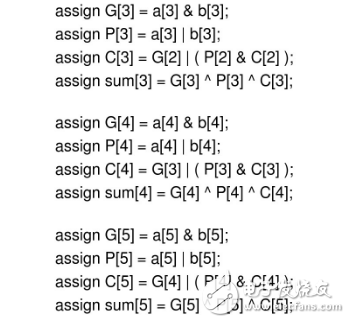

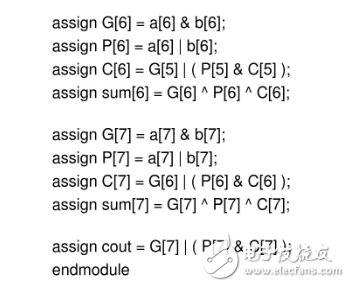

加法器電路設(shè)計(jì)方案四:八位超前進(jìn)位加法器設(shè)計(jì)

程序

八位超前進(jìn)位加法器RTL圖

加法器電路設(shè)計(jì)方案五:四位串行進(jìn)位加法器設(shè)計(jì)

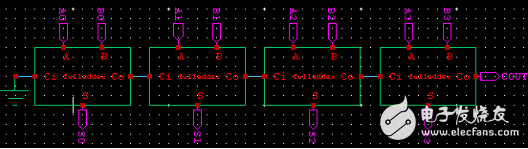

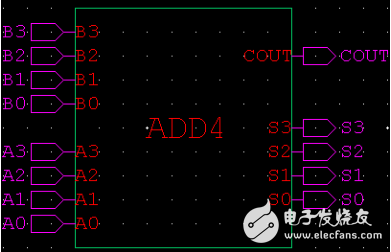

根據(jù)四位串行進(jìn)位加法器的邏輯關(guān)系,用S-Edit完成串行進(jìn)位加法器的電路圖以及模塊符號(hào)圖的設(shè)計(jì),如圖1和圖2所示。

圖1 四位串行進(jìn)位加法器電路圖

圖2?四位串行進(jìn)位加法器模塊符號(hào)圖

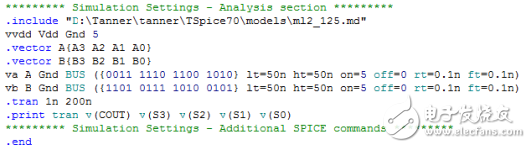

加載SPICE文件

完成四位串行進(jìn)位加法器的設(shè)計(jì),提取設(shè)計(jì)電路的SPICE 文件,并對(duì)SPICE 文件進(jìn)行文件加載設(shè)定,以完成整個(gè)電路的仿真。加載包含文件如下圖所示。

加載SPICE文件圖

仿真

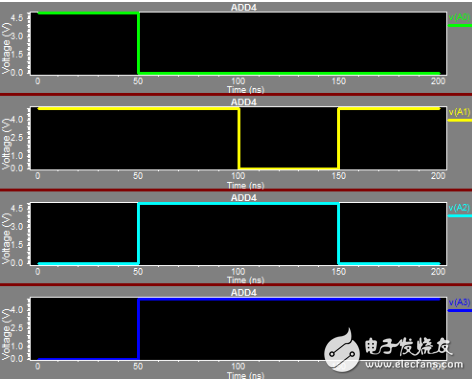

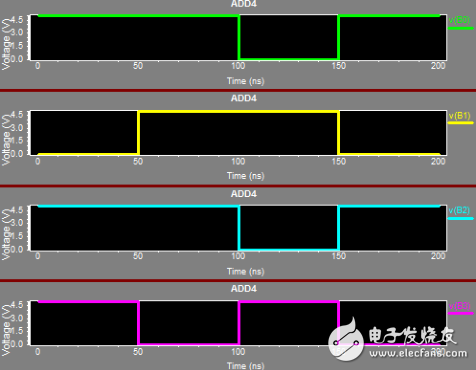

完成加載設(shè)定后,對(duì)設(shè)計(jì)電路進(jìn)行仿真,其仿真結(jié)果如圖3、圖4 所示,圖3為輸入信號(hào)A 設(shè)定的電平波形,從上到下依次為A0、Al、A2、示。A3。圖4為輸入信號(hào)B 設(shè)定的波形圖,從上到下依次為B0、B1、B2、B3。

圖3 輸入信號(hào)A波形圖

圖4 輸入信號(hào)B波形圖

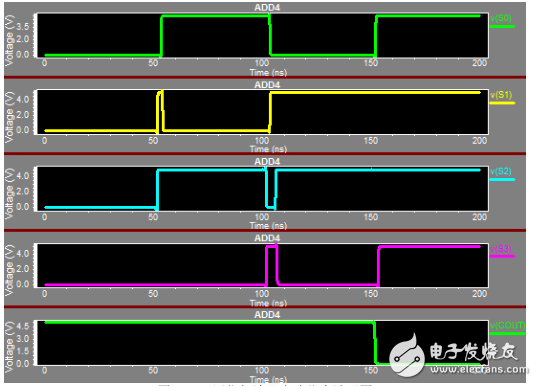

通過對(duì)輸入信號(hào)A、B的設(shè)定,通過四位串行進(jìn)位加法器電路的仿真運(yùn)算,其仿真結(jié)果如圖5所示。該圖從上至下的信號(hào)端依次為SO、S1、S2、S3、COUT.

圖5 四位加法器電路仿真波形圖

通過上述波形圖可知,當(dāng)t=0-50ns 時(shí),A3A2A1A0=0011,B3B2B1B0=1101,輸出和S3S2S1S0=0000,輸出進(jìn)位COUT=1;當(dāng)t=50-100ns 時(shí),A3A2A1A0=1110,B3B2B1B0=0111,輸出和S3S2S1S0=0101,輸出進(jìn)位COUT=1;當(dāng)t=100-150ns時(shí),A3A2A1A0=1100,B3B2B1B0=1010,輸出和S3S2S1S0=0110,輸出進(jìn)位時(shí),輸出和COUT=1;當(dāng)t=150-200ns,A3A2A1A0=1010,B3B2B1B0=0101,S3S2S1S0=111,輸出進(jìn)位COUT=0。通過對(duì)仿真波形圖的分析,可以看出該仿真結(jié)果存在0-10ns 的延時(shí),除此之外均符合四位串行進(jìn)位加法器的邏輯功能。

加法器電路設(shè)計(jì)方案六:反相加法器的電路設(shè)計(jì)1

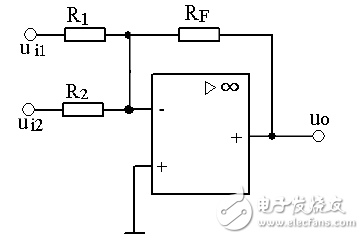

下圖是由運(yùn)算放大器構(gòu)成的反相加法器的電路圖

uo=-[ui1*RF/R1+ui2*RF/R2]

加法器電路設(shè)計(jì)方案七:反相加法器的電路設(shè)計(jì)2

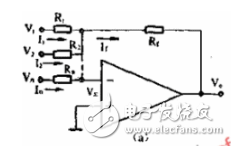

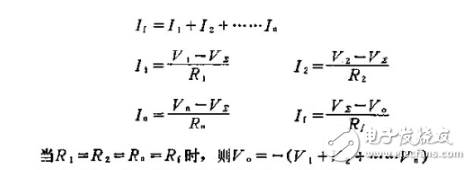

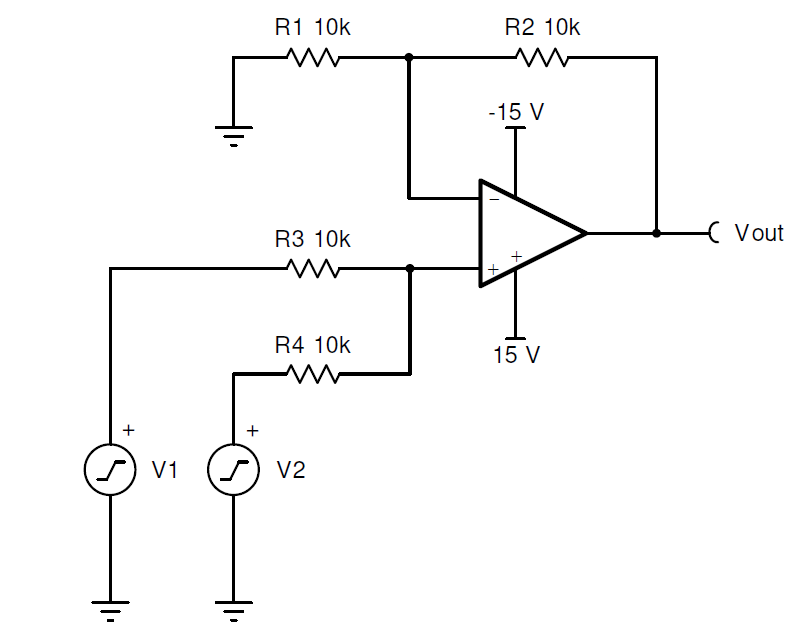

下圖為一個(gè)反相加法器電路

由圖可知

加法器電路設(shè)計(jì)方案八:同相加法器電路設(shè)計(jì)

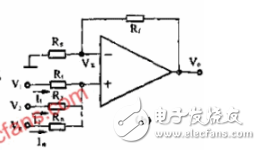

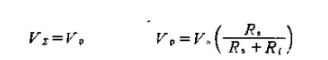

下圖為同相加法器電路

從圖中可知同向放大器的真正輸入信號(hào)是外接信號(hào)與反饋信號(hào)VΣ相串聯(lián)的,因此可得出

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論