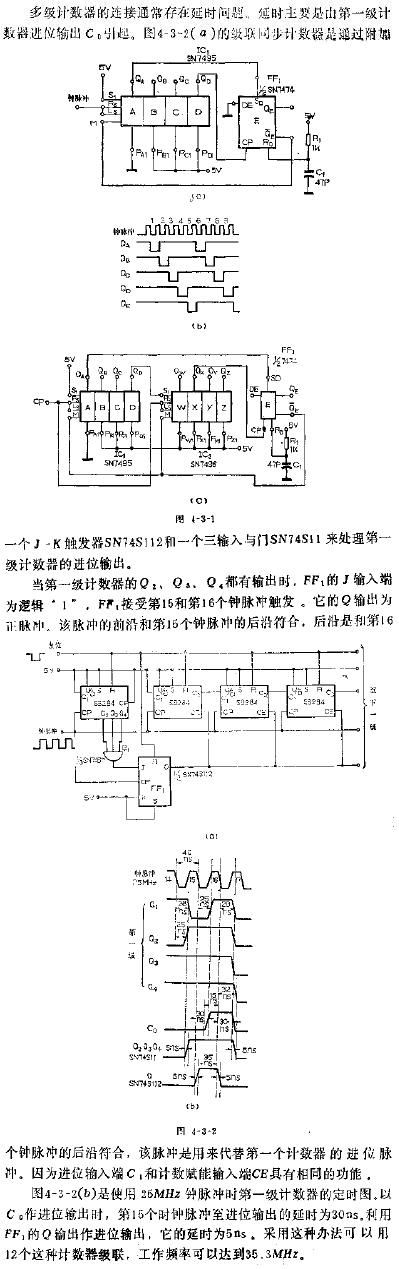

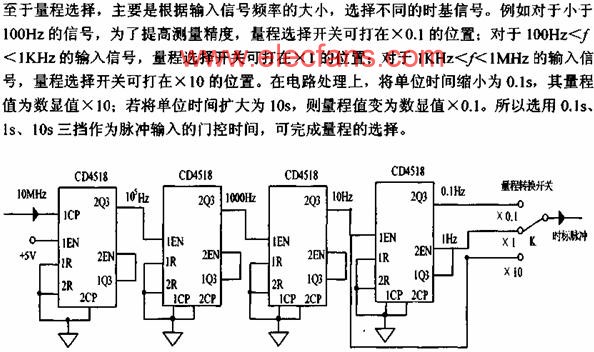

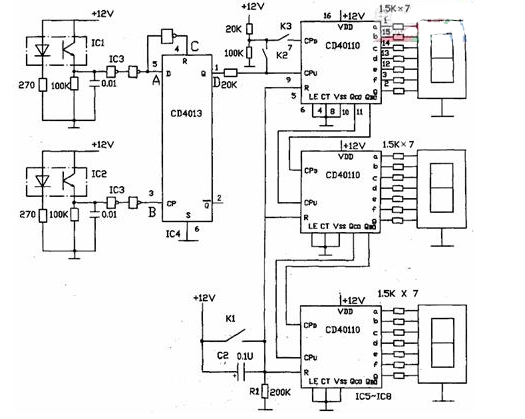

十進(jìn)制同步加法計(jì)數(shù)器CD4518:

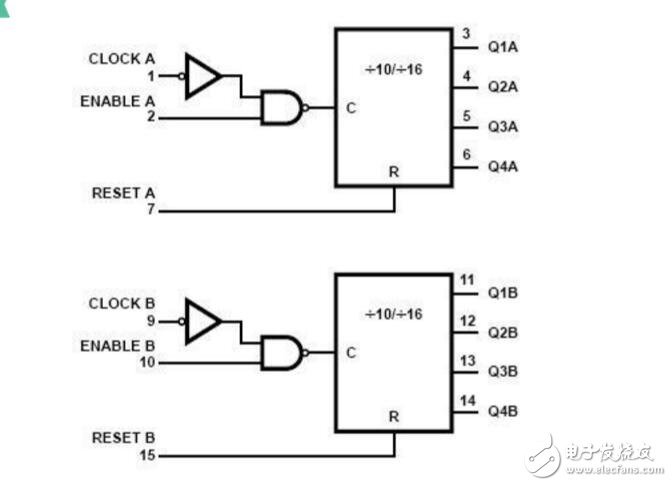

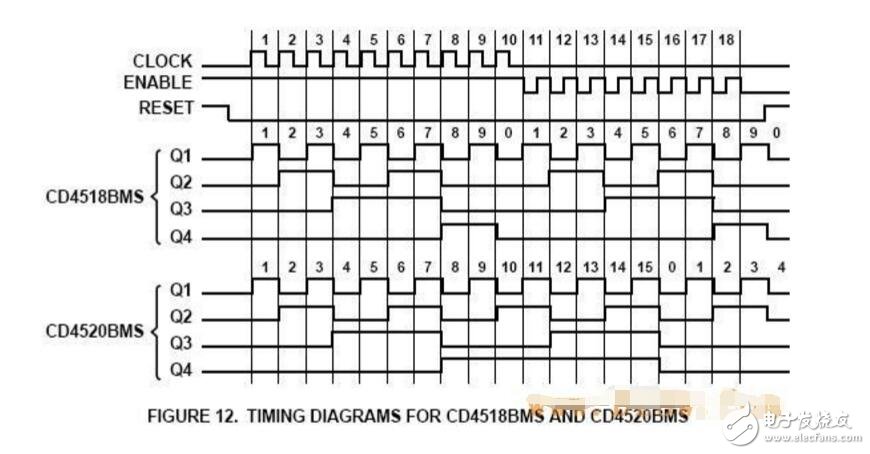

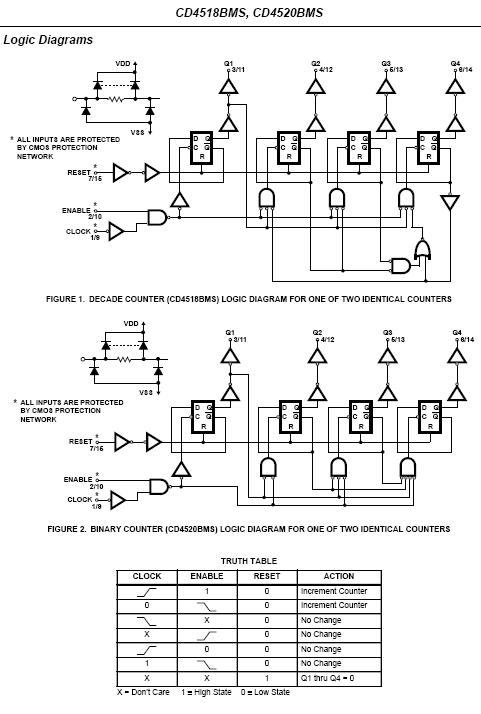

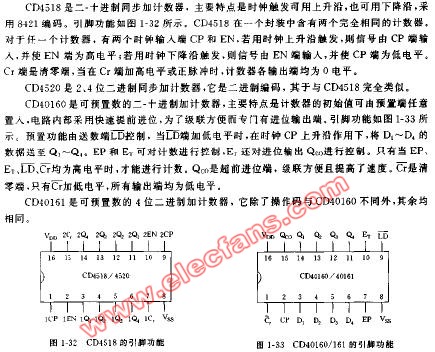

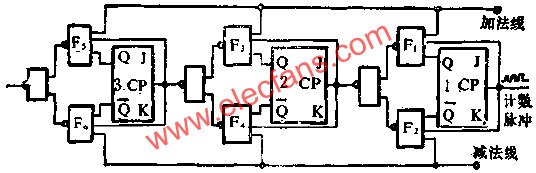

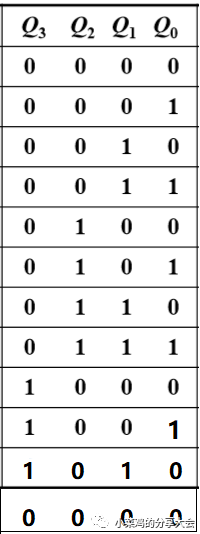

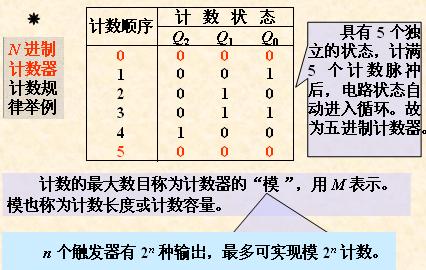

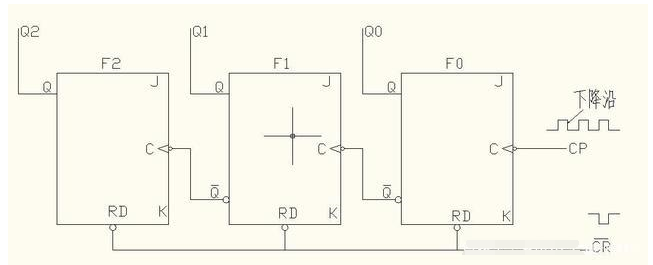

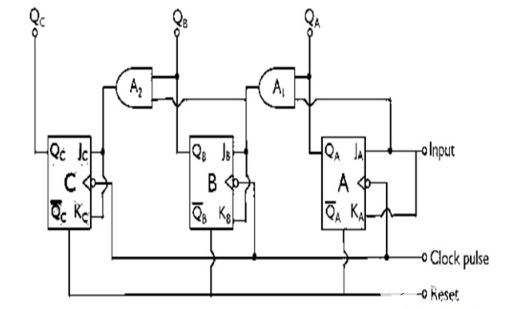

CD4518/CC4518是二、十進(jìn)制(8421編碼)同步加計(jì)數(shù)器,內(nèi)含兩個單元的加計(jì)數(shù)器,其功能表如真值表所示。每單個單元有兩個時(shí)鐘輸入端CLK和EN,可用時(shí)鐘脈沖的上升沿或下降沿觸發(fā)。由表可知,若用ENABLE信號下降沿觸發(fā),觸發(fā)信號由EN端輸入,CLK端置“0”;若用CLK信號上升沿觸發(fā),觸發(fā)信號由CL℃K端輸入,ENABLE端置“1”。RESET端是清零端,RESET端置“1”時(shí),計(jì)數(shù)器各端輸出端Q1~Q4均為“0”,只有RESET端置“0”時(shí),CD4518才開始計(jì)數(shù)。

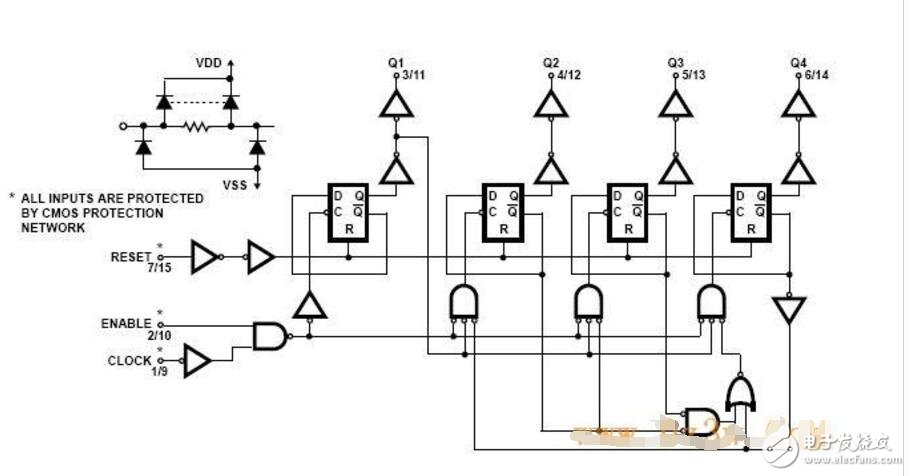

CD4518采用并行進(jìn)位方式,只要輸入一個時(shí)鐘脈沖,計(jì)數(shù)單元Q1翻轉(zhuǎn)一次;當(dāng)Q1為1,Q4為0時(shí),每輸入一個時(shí)鐘脈沖,計(jì)數(shù)單元Q2翻轉(zhuǎn)一次;當(dāng)Q1=Q2=1時(shí),每輸入一個時(shí)鐘脈沖Q3翻轉(zhuǎn)一次;當(dāng)Q1=Q2=Q3=1或Q1=Q4=1時(shí),每輸入一個時(shí)鐘脈沖Q4翻轉(zhuǎn)一次。這樣從初始狀態(tài)(“0”態(tài))開始計(jì)數(shù),每輸入10個時(shí)鐘脈沖,計(jì)數(shù)單元便自動恢復(fù)到“0”態(tài)。若將第一個加計(jì)數(shù)器的輸出端Q4A作為第二個加計(jì)數(shù)器的輸入端ENB的時(shí)鐘脈沖信號,便可組成兩位8421編碼計(jì)數(shù)器,依次下去可以進(jìn)行多位串行計(jì)數(shù)。

CD4520為二進(jìn)制加計(jì)數(shù)器,由兩個相同的內(nèi)同步4級計(jì)數(shù)器構(gòu)成。計(jì)數(shù)器級為D型觸發(fā)器,具有內(nèi)部可交換CP和EN線,用于在時(shí)鐘上升沿或下降沿加計(jì)數(shù)。在單個單元運(yùn)算中,EN輸入保持高電平,且在CP上升沿進(jìn)位。CR線為高電平時(shí),計(jì)數(shù)器清零。計(jì)數(shù)器在脈動模式可級聯(lián),通過將Q3連接至下—計(jì)數(shù)器的EN輸入端可實(shí)現(xiàn)級聯(lián),同時(shí)后者的CP輸入保持低電平。

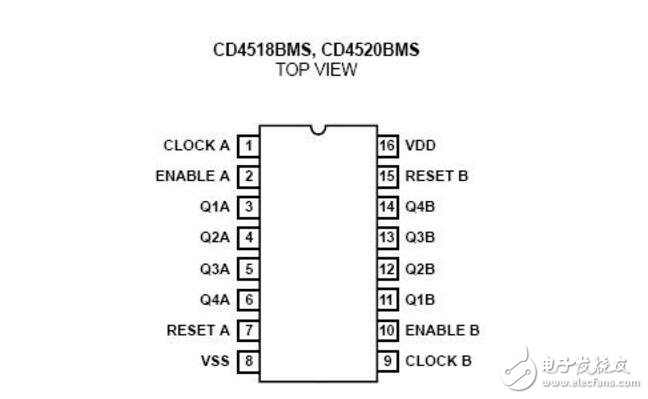

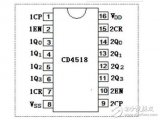

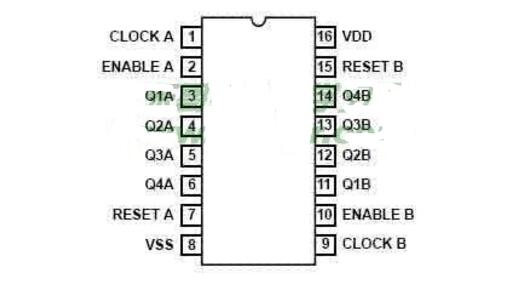

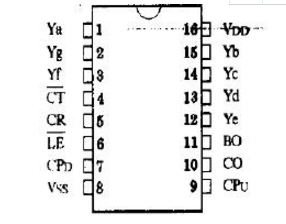

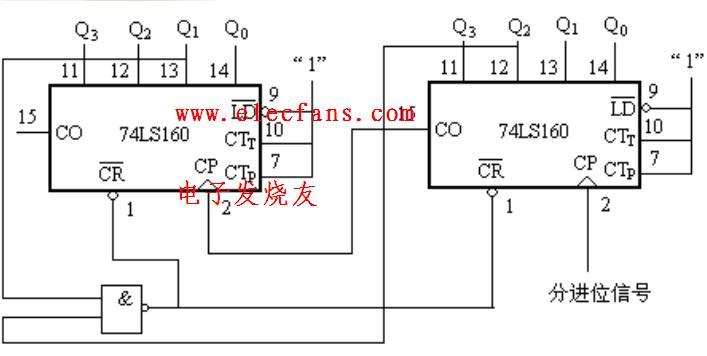

CD4518 引腳圖:

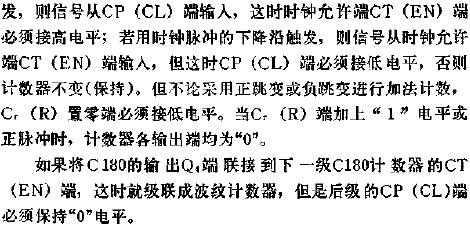

引腳符號功能:

1 9CLOCK時(shí)鐘輸入端

7 15RESET消除端

2 10ENABLE計(jì)數(shù)允許控制端

3 4 5 6Q1A-Q4A計(jì)數(shù)輸出端

11 12 13 14Q1B-Q4B計(jì)數(shù)輸出端 8 VSS地

16VDD電源正

功能圖:

CD4518邏輯圖:

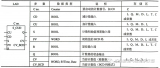

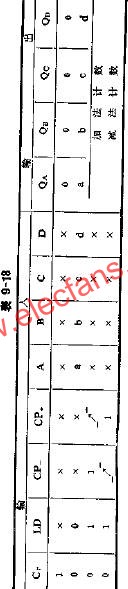

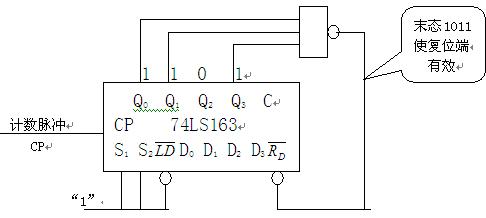

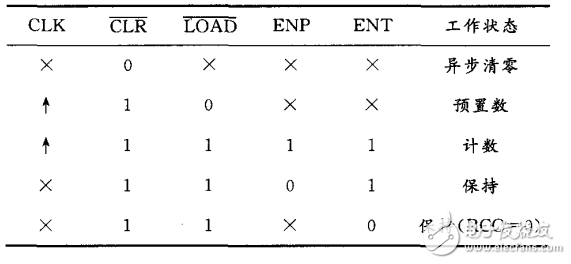

真值表功能:

上升沿 10加計(jì)數(shù)

0下降沿 0加計(jì)數(shù)

下降沿 X0不變

X上升沿 0不變

上升沿 00不變 1下降沿 0不變

XX1Q0~Q4=0

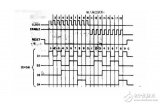

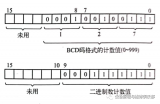

CD4518 CD4520時(shí)序圖

極限參數(shù): DC Supply Voltage Range, (VDD)-0.5V to +20V

(Voltage Referenced to VSS Terminals)

Input Voltage Range, All Inputs輸入電壓范圍,所有投入 -0.5V to VDD +0.5V

DC Input Current, Any One Input直流輸入電流±10mA

Operating Temperature Range 工作溫度范圍-55℃ to +125℃

Storage Temperature Range (TSTG)儲存溫度范圍-65℃ to +150℃

電子發(fā)燒友App

電子發(fā)燒友App

評論