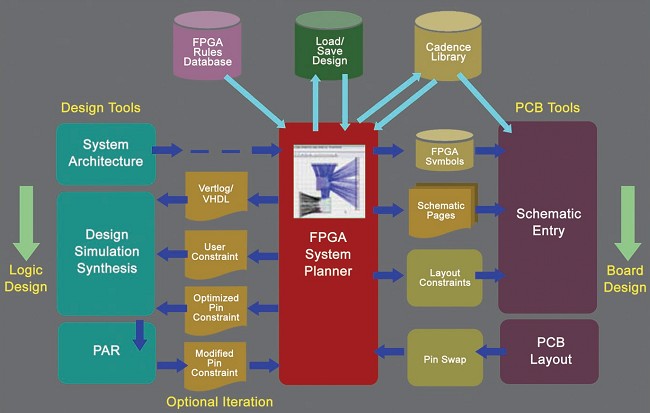

因為手上有一塊Xilinx的Spartan--3E開發板,前些日子陸陸續續學習了ISE的一般工程開發,熟悉了Xilinx ISE 10.x的軟件操作和開發板的使用。近來沒有事情,于是乎,又把那開發板拿出來把弄把弄,開始學習Xilinx的FPGA的DSP開發設計。在這里先介紹一下Xlinx FPGA的DSP設計工具和設計流程。

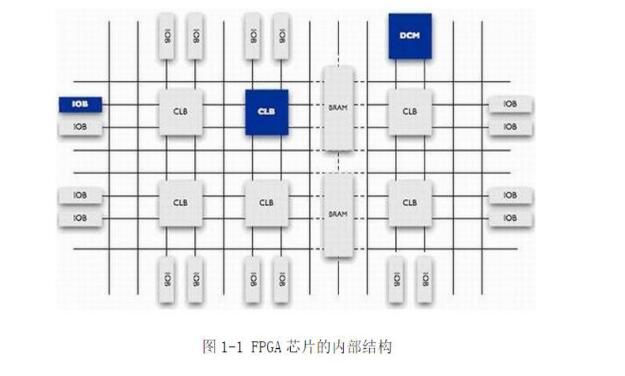

近年來,隨著多媒體技術和無線通信技術的迅猛發展,信息技術領域對DSP應用的需求不斷增長,傳統的DSP處理器(現在用得最多的當屬IT的DSP,種類多,功能強大,軟件技術也很成熟)雖然時鐘速率很高,當DSP處理器在運行時按指令順序執行,因而資源利用率不高,數據的吞吐量較低,難以實現高速率,高復雜度的設計。而FPGA擁有大量可編程邏輯資源,比如專用的DSP塊,乘法器、雙端口RAM、LUT、寄存器和DCM等,同時配合嵌入式處理器,像Altera的NiosII核、Xilinx的MicroBlaze和PowerPC405等處理器軟核或硬核,可以輕松實現高數據率的數字信號處理設計,而且性能原聲與傳統的DSP處理器,具有可裁剪,靈活性大等特點,正越來越被人們所重視。

使用FPGA進行DSP算法設計時,傳統方式下,設計者首先要進行浮點數的算法驗證和仿真,然后再將其轉換為定點數程序;其次將定點數算法編寫成HDL代碼,通過反復的功能仿真,后仿真驗證程序的正確性,最終生成比特流。Xilinx公司推出的系統建模工具System Generator簡化了整個DSP設計流程。設計者只需要根據設計要求咱Simulink下進行系統建模,使用System Generator工具即可自動生成可執行比特流、測試文件等,去掉繁瑣的仿真、對比和驗證過程。由于提供了適合硬件設計的數字信號處理(DSP)建模環境,加速、簡化了FPGA的DSP系統級硬件設計。

關于System Generator的下載和安裝過程,我在此就不詳細說明了,在google上搜索一下就能找到的。關于System Gnenrator的使用說明我在此向大家推薦一本很好的教材--《Xilinx ISE Design suite 10.x FPGA開發指南》(人民郵電出版社、田耕 胡彬 徐文波等著)我是在學校圖書館借到的這本書,寫得很詳細,相當不錯。我寫這篇文章的之前做的實驗也是參考上面做的。下面我進入正題,具體介紹我在用SystemGenerator工具完成DSP設計后使用Xilinx ISE 10.x 調用Modelsim SE 6.5進行仿真驗證時遇到的的若干問題及其解決方法。

下圖為我設計的用Matlab Simulink工具設計DSP工程。

在用System Generator進行FPGA的DSP模塊設計是以下幾點值得特別注意:

①設計的的FPGA DSP模塊的全局輸入和輸出數據(也就是在非Xilinx庫提供的數據源或者數據顯示、測量終端,比如下面設計中的Step信號源和Scope示波器等)必須經過Xilinx提供的Gateway In和Gateway OUT進行采樣,進而得到FPGA內部能夠處理的定點數。

②每個設計中至少要包含一個System Generator圖標,因為它是聯系MATLAB設計與Xilinx FPGA 硬件實現的主要橋梁,通過它可以實現FPGA實現屬性的設置和修改,雙擊該圖標會出現如圖-2所示的對話框。

③由于在System Generator中進行設計是需要對外部數據進行采樣,所以設計中各個Gateway In和Gateway Out模塊都有一個采樣周期和采樣后所得定點數精度的設置,另外在整個系統也必須有一個系統采樣設置,多數情況下就對應著FPGA實現設計是的全局時鐘,其設置在 圖-2中的Simulink System Clock(sec)。這里需要特別注意,系統設置必須是整個FPGA的最高時鐘,而Gateway In和Gateway Out模塊的采樣周期都必須是它的整數倍,否則系統會報錯,設計失敗。

?

下圖為System Generator的系統設置,請注意其中勾選了Create testbench選項,這樣在點擊Generator以后,系統才會自動生成勇于Modelsim仿真的測試文件,十分方便。

?

當一切設計好之后,點擊圖-2中的Generator按鈕,系統就會自動調用ISE工具進行綜合并產生所以需要的設計文件和仿真文件。

接下來,運行ISE,打開Open Project,將路徑切換至MATLAB的work工作目錄文件下找到netlist文件,進入就會看到一個已經生產的<工程名>_dcm_mcw.ise的ISE工程文件如圖-3示,點擊打開.

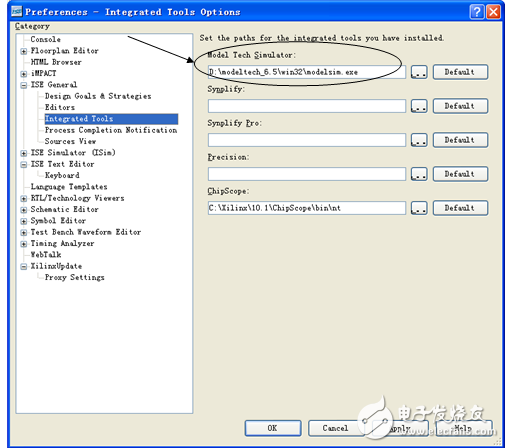

接著,設置ISE調用Modelsin進行仿真的路徑:

點擊ISE窗口的Edit---->Prefrence,出現圖-4窗口,點擊展開ISE General--->Intergrated Tools,如下所示,在Model Tech simulator項選擇你的Modelsim安裝路徑完成設置。另外ISE也提供利用其他綜合工具進行設計綜合的軟件接口,如Synplify 或者Synplify Pro。

圖-4 點擊ISE窗口的Edit---->Prefrence

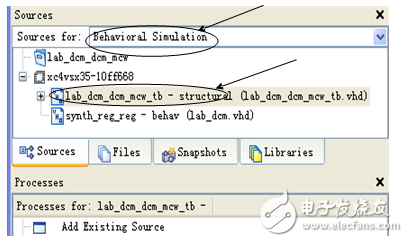

然后,回到ISE工程界面,在source窗口選擇Source for 切換至Behavior Simulation,此時在Sources窗口就能看見剛才System Generator自動生成的testbench測試文件了以<工程名>-dcm_mcw_tb-structure形式命名。如圖-5示:

?

接下來的一步是決定ISE能否成功調用Modelsim SE6.5進行仿真工作的關鍵。我遇到的問題也大都在于此。如果此時,你和我一樣迫不及待的想看到仿真的結果而草草的點擊圖-6中Process窗口的Simulate Behavioral Model的話,一連串的問題也就隨之出現了。

如圖-6所示,Modelsim的命令窗口輸出了以下錯誤信息

# ** Error: lab_dcm.vhd(41): Library xilinxcorelib not found.

# ** Error: lab_dcm.vhd(43): VHDL Compiler exiting

# ** Error: D:/modeltech_6.5/win32/vcom failed.

# Error in macro ./pn_behavioral.do line 9

# D:/modeltech_6.5/win32/vcom failed.

# while executing

?

上面的信息提示://沒找到 Library xilinxcorelib所以編譯器不能對當前工程進行編譯和仿真,所編譯器退出。

看到如此的信息,當時很茫然,這到底是怎么回事呢?從 xilinxcorelib來看似乎是Modelsim里面沒有Xilinx的仿真庫呀!

到google上面一查才知道,原來用Modelsim進行仿真時,先要對設計中調用的元件庫進行編譯,也就是compile,通過之后才能進行波形仿真(simulate)。而Modelsim 的SE版本屬于通用版,僅集成(也就是自帶的)一般的庫,比如ieee庫,Verilog庫和標準庫std等。不像其專業版,如跟Altera設計的ModelSim-Altera版就自帶了AlteraFPGA的全部設計庫。

另外,Modelsim在啟動時,會調用一個非常關鍵的初始化文件--Modelsim.ini,這個文件決定了本次Modelsim軟件啟動后所具備的庫的多少和映射關系。在知道了這一點后,我就在電腦上搜索Modelsim.ini,結果驚訝的發現了在我的電腦上面居然有好幾個Modelsim.ini文件。如圖-7所示:

?

看到上面的搜索結果,我才想起以前曾經使用過Modelsim,但都是FPGA軟件安裝包配套的版本,有ACTEL的FPGA設計軟件Libero8.3自帶的專業許可的Modelsim版本和Altera 的FPGA設計軟件Quartus9.0自帶的ModelSim-Altera 6.4a (Quartus II 9.0) Starter Edition版本,在使用的時候由于是專業版,都安裝好了各自FPGA廠商的設計庫,在用FPGA軟件調用Modelsim是從未遇到過此類數據庫lib方面的問題。

由此,我也發現EDA工具在生成Modelsim測試文件時會根據FPGA的設計環境生產一個Modelsim.ini文件,用于調用Modelsim軟件仿真時初始化Modelsim的啟動環境。該初始化文件一般都包含在各自的工程設計文件目錄下。如圖-8所示。

我打開我當前的設計工程目錄:D:\Program Files\MATLAB\R2007a\work\my_lab\netlist下的Modelsim.ini文件,發現其中的庫設置內容如下:

[Library]

others = $MODEL_TECH/../modelsim.ini

;vhdl_psl_checkers = $MODEL_TECH/../vhdl_psl_checkers // Source files only for this release

;verilog_psl_checkers = $MODEL_TECH/../verilog_psl_checkers // Source files only for this release

;mvc_lib = $MODEL_TECH/../mvc_lib

上面語句的意思是每個庫的名稱及其映射路徑,從上面并沒有發現錯誤中所提到的xilinxcorelib這個庫及其映射路徑。所以出錯也就理所當然啦!

另外從上面的語句還可以看出,Modelsim在啟動時首先調用的是當前工程設計目錄下的modelsim.ini文件,其他它通過others = $MODEL_TECH/../modelsim.ini還會調用modelsim安裝目錄下的初始化文件,進行庫的映射。

好了,在打開modelsim安裝目錄下的初始化文件modelsim.ini文件發現其庫映射設置如下:

[Library]

std = $MODEL_TECH/../std

ieee = $MODEL_TECH/../ieee

verilog = $MODEL_TECH/../verilog

vital2000 = $MODEL_TECH/../vital2000

std_developerskit = $MODEL_TECH/../std_developerskit

synopsys = $MODEL_TECH/../synopsys

modelsim_lib = $MODEL_TECH/../modelsim_lib

sv_std = $MODEL_TECH/../sv_std

mtiAvm = $MODEL_TECH/../avm

mtiOvm = $MODEL_TECH/../ovm-2.0.1

mtiUPF = $MODEL_TECH/../upf_lib

mtiPA = $MODEL_TECH/../pa_lib

floatfixlib = $MODEL_TECH/../floatfixlib

;vhdl_psl_checkers = $MODEL_TECH/../vhdl_psl_checkers // Source files only for this release

;verilog_psl_checkers = $MODEL_TECH/../verilog_psl_checkers // Source files only for this release

;mvc_lib = $MODEL_TECH/../mvc_lib

中也就是我們在圖-6的modelsim軟件界面的library欄所見到的所有庫了。

繼而,我又在google上進一步搜索ISE調用modelsim進行仿真方面的問題。看到一些論壇的回帖中談到,用Modelsim進行Xilinx FPGA設計的仿真時安裝Xilinx庫的各種方法。我將它們都一一試了一遍,問題依舊啊!特別是其中用ISE的compxlibgui.exe工具(安裝路徑\Xilinx\10.1\ISE\bin\nt\compxlibgui.exe)進行自動的Xilinx庫編譯時,由于選擇了全部的庫進行編譯,用了近3個小時才完成。于是,我很不甘心就這樣失敗了。

回想整個工程,我又在電腦上搜索modelsim.ini文件,發現此時在ISE的安裝目錄下多了一個該文件(見圖-7所示),于是迫不及待的打開,發現如下:

[Library]

others = $MODEL_TECH/../modelsim.ini

;vhdl_psl_checkers = $MODEL_TECH/../vhdl_psl_checkers // Source files only for this release

;verilog_psl_checkers = $MODEL_TECH/../verilog_psl_checkers // Source files only for this release

;mvc_lib = $MODEL_TECH/../mvc_lib

UNISIMS_VER = C:\Xilinx\10.1\ISE\verilog\mti_se\unisims_ver

UNIMACRO_VER = C:\Xilinx\10.1\ISE\verilog\mti_se\unimacro_ver

UNI9000_VER = C:\Xilinx\10.1\ISE\verilog\mti_se\uni9000_ver

SIMPRIMS_VER = C:\Xilinx\10.1\ISE\verilog\mti_se\simprims_ver

XILINXCORELIB_VER = C:\Xilinx\10.1\ISE\verilog\mti_se\XilinxCoreLib_ver

SECUREIP = C:\Xilinx\10.1\ISE\verilog\mti_se\secureip

AIM_VER = C:\Xilinx\10.1\ISE\verilog\mti_se\abel_ver\aim_ver

CPLD_VER = C:\Xilinx\10.1\ISE\verilog\mti_se\cpld_ver

UNISIM = C:\Xilinx\10.1\ISE\vhdl\mti_se\unisim

UNIMACRO = C:\Xilinx\10.1\ISE\vhdl\mti_se\unimacro

SIMPRIM = C:\Xilinx\10.1\ISE\vhdl\mti_se\simprim

XILINXCORELIB = C:\Xilinx\10.1\ISE\vhdl\mti_se\XilinxCoreLib

AIM = C:\Xilinx\10.1\ISE\vhdl\mti_se\abel\aim

PLS = C:\Xilinx\10.1\ISE\vhdl\mti_se\abel\pls

CPLD = C:\Xilinx\10.1\ISE\vhdl\mti_se\cpld

奇跡般的發現了XILINXCORELIB = C:\Xilinx\10.1\ISE\vhdl\mti_se\XilinxCoreLib

于是,欣喜萬分。將上面的全部粗體語句全部copy到當前工程目錄下的modelsim.ini文件中,再在ISE下面重復上面的過程,奇跡終于出現啦!

My God!所有的Xilinx庫都出現了,仿真波形也出來了!

?

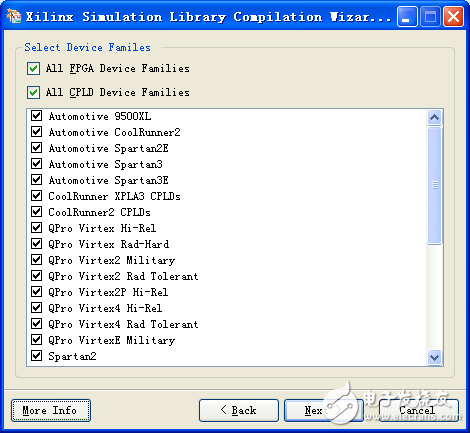

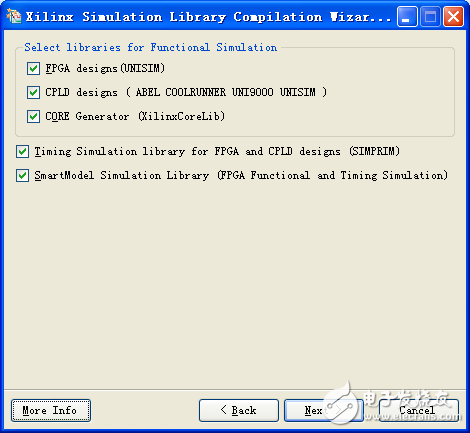

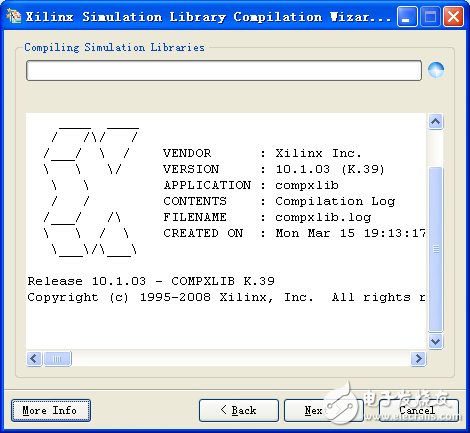

這里再附上我上傳在本網站上的Modelsim SE 6.5的完整版下載鏈接和利用ISE的compxlibgui.exe工具進行Xilinx庫編譯的流程截圖。希望對大家有幫助。Modelsim SE 6.5的完整版下載鏈接:如果未能找到,請在搜索欄中搜Modelsim SE 6.5就可以看見了,全部11個壓縮包,共202M

。

?

大家點擊附件也可以查看完整版本。

?

胡恩偉

寫于2010年3月15日于重大A區一舍

Xilinx ISE 10.x 調用Modelsim SE 6.5仿真的若干問題及其解決方法 ? 843 KB ?

?

電子發燒友App

電子發燒友App

評論