KENWOOD對講機(jī)復(fù)位方法

現(xiàn)在在廣大HAM中使用KENWOOD設(shè)備的朋友有很多,但常常會有因為錯誤操作而使設(shè)置混亂的情況發(fā)生,這時候就需

2010-02-08 09:00:39 5644

5644 對FPGA設(shè)計中常用的復(fù)位設(shè)計方法進(jìn)行了分類、分析和比較。針對FPGA在復(fù)位過程中存在不可靠復(fù)位的現(xiàn)象,提出了提高復(fù)位設(shè)計可靠性的4種方法,包括清除復(fù)位信號上的毛刺、異步復(fù)位同步釋放、采用專用全局

2014-08-28 17:10:03 8153

8153 本文描述了復(fù)位的定義,分類及不同復(fù)位設(shè)計的影響,并討論了針對FPGA和CPLD的內(nèi)部自復(fù)位方案。

2016-07-11 14:33:49 6228

6228

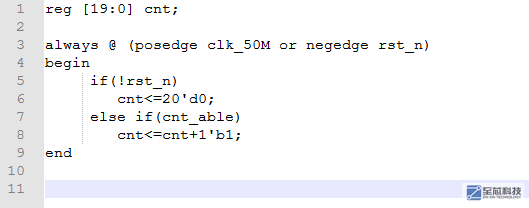

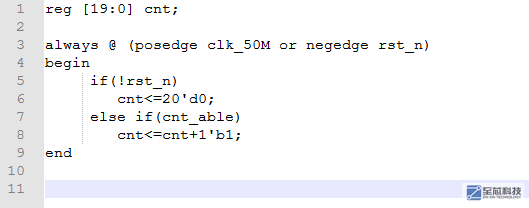

大家好,博主最近有事忙了幾天,沒有更新,今天正式回來了。那么又到了每日學(xué)習(xí)的時間了,今天咱們來聊一聊 簡談FPGA的上電復(fù)位,歡迎大家一起交流學(xué)習(xí)。 在基于verilog的FPGA設(shè)計中,我們常常

2018-06-18 19:24:11 19894

19894

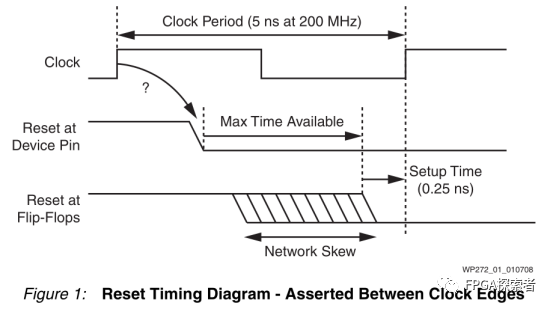

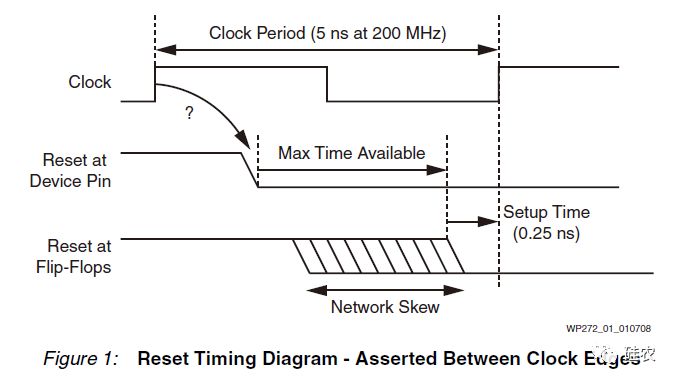

線將會是一個和時鐘一樣多扇出的網(wǎng)絡(luò),如此多的扇出,時鐘信號是采用全局時鐘網(wǎng)絡(luò)的,那么復(fù)位如何處理?有人提出用全局時鐘網(wǎng)絡(luò)來傳遞復(fù)位信號,但是在FPGA設(shè)計中,這種方法還是有其弊端。一是無法解決復(fù)位結(jié)束可能造成的時序問題,因為全

2019-02-20 10:40:44 1068

1068

在復(fù)位電路中,由于復(fù)位信號是異步的,因此,有些設(shè)計采用同步復(fù)位電路進(jìn)行復(fù)位,并且絕大多數(shù)資料對于同步復(fù)位電路都認(rèn)為不會發(fā)生亞穩(wěn)態(tài),其實不然,同步電路也會發(fā)生亞穩(wěn)態(tài),只是幾率小于異步復(fù)位電路。

2020-06-26 16:37:00 1232

1232

最近看advanced fpga 以及fpga設(shè)計實戰(zhàn)演練中有講到復(fù)位電路的設(shè)計,才知道復(fù)位電路有這么多的門道,而不是簡單的外界信號輸入系統(tǒng)復(fù)位。

2020-09-01 15:37:07 1461

1461

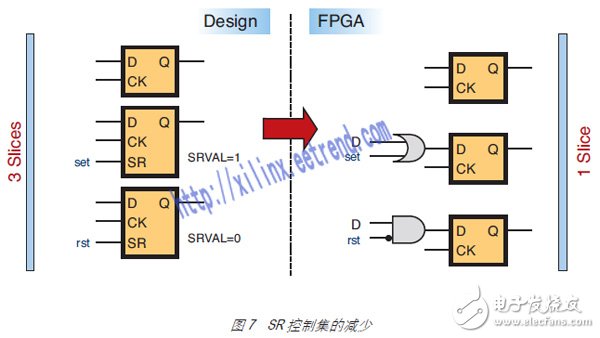

本篇文章參考Xilinx White Paper:Get Smart About Reset: Think Local, Not Global 在沒看這篇文章前,回想一下平時我們常用的復(fù)位方式

2020-11-18 17:32:38 3110

3110 作者:NingHeChuan Get Smart About Reset: Think Local, Not Global。 對于復(fù)位信號的處理,為了方便我們習(xí)慣上采用全局復(fù)位,博主在很長一段時間

2020-12-25 12:08:10 2303

2303

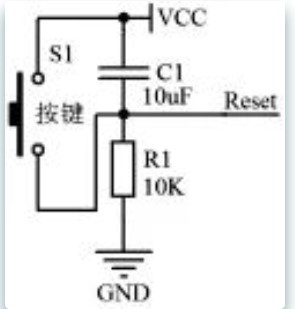

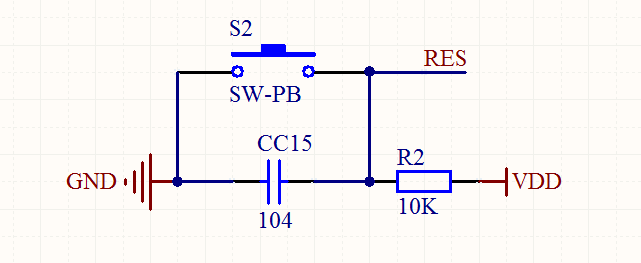

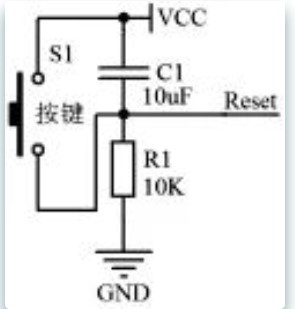

各位小伙伴們大家好,復(fù)位電路在單片機(jī)小系統(tǒng)中很常見。今天我們就探討下單片機(jī)阻容復(fù)位電路的構(gòu)成、特點和改進(jìn)方法。

2022-08-09 11:51:24 3613

3613

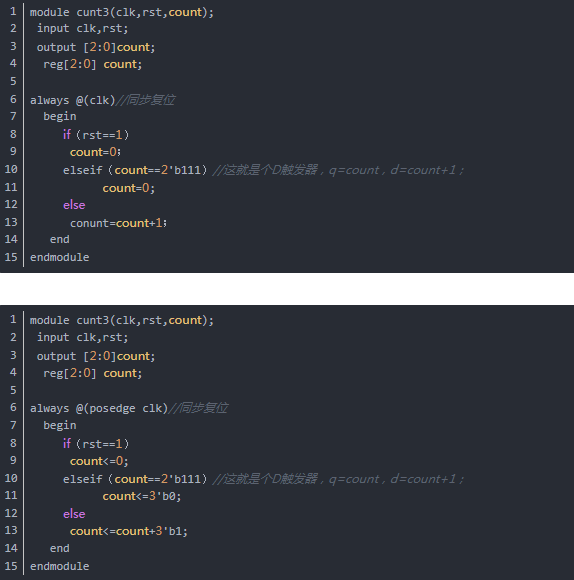

在FPGA設(shè)計中,復(fù)位電路是非常重要的一部分,它能夠確保系統(tǒng)從初始狀態(tài)開始啟動并保證正確運行。本文將分別介紹FPGA中三種常用復(fù)位電路:同步復(fù)位、異步復(fù)位和異步復(fù)位同步釋放,以及相應(yīng)的Verilog代碼示例。

2023-05-14 14:44:49 1679

1679

在FPGA設(shè)計中,當(dāng)復(fù)位整個系統(tǒng)或功能模塊時,需要將先關(guān)寄存器被清零或者賦初值,以保證整個系統(tǒng)或功能運行正常。在大部分的設(shè)計中,我們經(jīng)常用“同步復(fù)位”或“異步復(fù)位”直接將所有的寄存器全部復(fù)位,這部分可能大家都習(xí)以為常。但實際上,是否需要每個寄存器都進(jìn)行復(fù)位呢?這是一個值得探討的問題。

2023-05-14 14:49:19 1701

1701

針對異步復(fù)位、同步釋放,一直沒搞明白在使用同步化以后的復(fù)位信號時,到底是使用同步復(fù)位還是異步復(fù)位?

2023-06-21 09:59:15 647

647

51單片機(jī)復(fù)位方法:在第9引腳接個持續(xù)2us的高電平就可以實現(xiàn)。何時復(fù)位:51單片機(jī)要復(fù)位只需要在第9引腳接個高電平持續(xù)2us就可以實現(xiàn)【注】1,系統(tǒng)上電啟動的時候復(fù)位一次,當(dāng)按鍵按下的時候系統(tǒng)也會

2021-11-18 08:52:21

從Cyclone III handbook 上看,FPGA內(nèi)部是包含POR, 即上電復(fù)位的,但是我習(xí)慣自己加一個reset。如果用電阻和電容搭建的reset電路,功能上是可以滿足要求,但是這種電路

2014-06-26 22:38:52

FPGA 門數(shù)計算方法FPGA 門數(shù)計算方法 FPGA 等效門數(shù)的計算方法有兩種: 1.把FPGA 基本單元(如LUT+FF ,ESB/BRAM)和實現(xiàn)相同功能的標(biāo)準(zhǔn)門陣列比較,門陣列中包含的門數(shù)

2012-08-11 10:29:07

復(fù)位電路本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計實戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCttFPGA器件在上電后都需要有一個確定的初始狀態(tài),以

2019-04-12 06:35:31

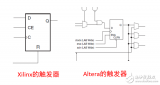

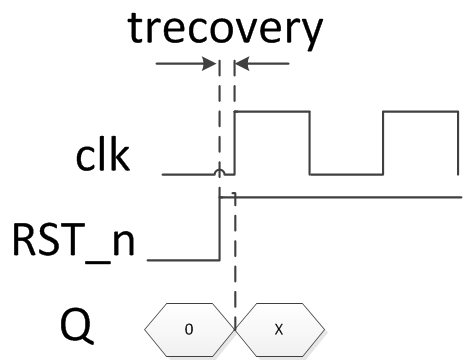

和removal時序檢查;異步復(fù)位同步撤離(推薦使用) 優(yōu)點:能避免純異步或純同步復(fù)位的潛在問題。它是FPGA設(shè)計中最受歡迎的復(fù)位,Altera建議使用這種復(fù)位方法。這種復(fù)位在使用前需要同步到各個使用時

2014-03-20 21:57:25

線將會是一個和時鐘一樣多扇出的網(wǎng)絡(luò),如此多的扇出,時鐘信號是采用全局時鐘網(wǎng)絡(luò)的,那么復(fù)位如何處理?有人提出用全局時鐘網(wǎng)絡(luò)來傳遞復(fù)位信號,但是在FPGA設(shè)計中,這種方法還是有其弊端。一是無法解決復(fù)位結(jié)束

2019-05-17 08:00:00

以前從來沒有對FPGA的復(fù)位可靠性關(guān)注過,想當(dāng)然的認(rèn)為應(yīng)該不會有什么問題。當(dāng)問題真正出在復(fù)位上的時候,才又仔細(xì)地對FPGA的復(fù)位深入的了解了一下。首先我們用的復(fù)位管腳不是FPGA的全局管腳,并且復(fù)位

2011-11-04 14:26:17

目前買了一批FPGA的核心板,在使用之前希望能先測試核心板的好壞,現(xiàn)在的測試方法是讓核心板的所有引腳輸出不同頻率的方波,然后用示波器看是否有波形輸出。但效果視乎不太理想,有的板子會有部分引腳無波形

2015-12-11 12:02:09

復(fù)位電路本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計實戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt FPGA器件在上電后都需要有一個確定的初始狀態(tài),以

2015-04-10 13:59:23

FPGA時鐘和復(fù)位電路設(shè)計本文節(jié)選自特權(quán)同學(xué)的圖書《FPGA設(shè)計實戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt FPGA的時鐘輸入都有專用引腳

2015-04-24 08:17:00

下面對FPGA設(shè)計中常用的復(fù)位設(shè)計方法進(jìn)行了分類、分析和比較。針對FPGA在復(fù)位過程中存在不可靠復(fù)位的現(xiàn)象,提出了提高復(fù)位設(shè)計可靠性的4種方法,包括清除復(fù)位信號上的毛刺、異步復(fù)位同步釋放、采用專用

2021-06-30 07:00:00

本帖最后由 eehome 于 2013-1-5 09:45 編輯

FPGA加密方法 —用于系列xilinx5/6/7一項設(shè)計被抄襲主要通過抄襲電路板和IC解密來完成常用抄板步驟1.復(fù)印掃描板卡

2013-01-01 20:44:47

fpga和單片機(jī)復(fù)位原理有哪些區(qū)別?

2023-10-16 08:22:12

你好,我想使用特定的FPGA(V5或V6)。在特殊條件下,FPGA應(yīng)在復(fù)位或丟失與電源的連接后重新編程。這應(yīng)該通過使用PROM自動完成。該舞會將在董事會中進(jìn)行整合。現(xiàn)在我正在使用ML507 EV板

2020-06-10 10:24:51

對于硬件設(shè)計來說,復(fù)位電路是必不可少的一部分,為了確保微機(jī)系統(tǒng)中電路穩(wěn)定可靠工作,復(fù)位電路的第一功能是上電復(fù)位。在 FPGA 設(shè)計中,復(fù)位起到的是同步信號的作用,能夠?qū)⑺械拇鎯υO(shè)置成已知狀態(tài)

2021-11-11 06:06:08

我正在使用 SBC FS6500 芯片。目前,SBC 會在 MCU 軟復(fù)位后發(fā)生復(fù)位(軟復(fù)位:表示 SBC 無法關(guān)閉電源,因為 SBC 為 MCU 供電)。MCU軟復(fù)位后有什么方法可以修復(fù) SBC 復(fù)位?

2023-03-29 06:24:10

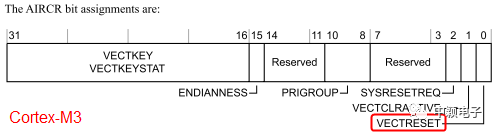

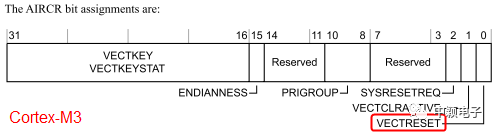

STM32系統(tǒng)軟復(fù)位的方法是什么

2021-11-26 06:11:58

除了看門狗,還有其他自復(fù)位方法嗎?無需外部上拉電阻即使 MCU 執(zhí)行軟復(fù)位,我也想保持 GPIO 為高電平。有什么辦法嗎?

2023-01-11 08:17:31

按蘋果官網(wǎng)教導(dǎo),iPad的電池是不宜放電的。最理想的充電方法,是使用附帶的10W充電插頭,由交流電直接充。想充電時間縮短,可關(guān)了機(jī)來充,會快約三分一時間。 使用USB接口充電,若在同步情況下,充電會十分緩慢。并要留意,以下幾種情況,會令電池放電而不是充電:1.當(dāng)電腦處于關(guān)機(jī)或休眠...

2021-09-14 09:24:28

盡管復(fù)位方案極其重要,可是卻是最被忽視的部分之一,許多設(shè)計人員認(rèn)為FPGA的全局復(fù)位資源將會完全解決問題,這是完全不正確的。至于為何說復(fù)位的重要性極高,是因為復(fù)位方案不好會引起不可重復(fù)的錯誤,而不可

2012-12-05 17:09:26

本帖最后由 何立立 于 2015-6-7 20:59 編輯

最近遇到FPGA復(fù)位信號的問題困擾很久,查了相關(guān)資料:FPGA設(shè)計是基于大量flip-flop或者寄存器的同步系統(tǒng)設(shè)計,所以所有這些

2015-06-07 20:39:43

例說FPGA連載12:狀態(tài)初始——復(fù)位電路特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc FPGA器件在上電后都需要有一個確定的初始

2016-07-25 15:19:04

`例說FPGA連載17:時鐘與復(fù)位電路設(shè)計特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc FPGA的時鐘輸入都有專用引腳,通過這些專用

2016-08-08 17:31:40

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載13:實驗平臺復(fù)位電路解析特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD FPGA的時鐘

2017-10-23 20:37:22

在網(wǎng)上了解到fpga的同步復(fù)位和異步復(fù)位都會存在不足,因此有人提出異步復(fù)位,同步釋放的方法來消除兩者的不足。對此也提出一些疑問,還請大家能指導(dǎo)一下:1、同步復(fù)位,同步復(fù)位的缺點包括需要復(fù)位信號的寬度

2014-04-16 22:17:53

根據(jù)一些WP文檔,最佳編碼實踐不是盡可能使用全局重置?這里有一個問題,如果沒有復(fù)位引腳,如何復(fù)位FPGA,每次想要復(fù)位時都要關(guān)閉FPGA!以上來自于谷歌翻譯以下為原文According

2019-04-18 14:19:27

fpga和單片機(jī)復(fù)位原理有哪些區(qū)別?

2023-10-15 11:49:11

主板復(fù)位電路工作原理及維修方法

復(fù)位電路的工作原理

2008-10-26 10:35:32 10436

10436

FPGA在現(xiàn)代電子系統(tǒng)設(shè)計中,由于其卓越性能、靈活方便而被廣泛使用,但基于SRAM的FPGA需要從外部進(jìn)行配置,配置數(shù)據(jù)很容易被截獲,故存遮安全隱患。總結(jié)了當(dāng)前FPGA的加密方法;提出了一種基于外部單片機(jī)的FPGA加密方法,該方法中使用外部單片機(jī)配合FPGA產(chǎn)生

2011-03-16 14:22:24 48

48 本文提出了一種基于SoPC的FPGA在線測試方法,是對現(xiàn)有FPGA在線測試方法的一種有效的補(bǔ)充。

2011-04-18 11:46:20 1145

1145

由KIA7033構(gòu)成的單片機(jī)復(fù)位電路,可手動復(fù)位,效果理想。

2012-01-04 10:50:04 2232

2232

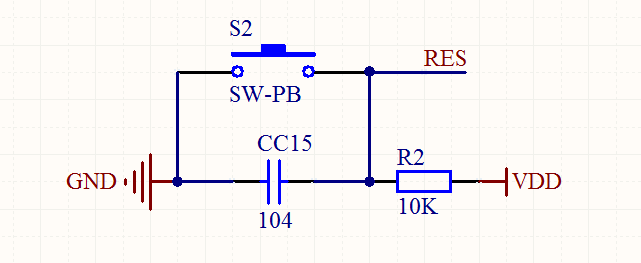

電源、時鐘和復(fù)位電路圖(Altera FPGA開發(fā)板)如圖所示:

2012-08-15 14:42:33 9398

9398

基于反熔絲的FPGA的測試方法_馬金龍

2017-01-07 19:08:43 2

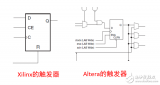

2 在Xilinx 的FPGA器件中,全局的復(fù)位/置位信號(Global Set/Reset (GSR))(可以通過全局復(fù)位管腳引入)是幾乎絕對可靠的,因為它是芯片內(nèi)部的信號。

2017-02-11 11:46:19 876

876

在FPGA中實現(xiàn)在應(yīng)用編程(In Application Programming,IAP)有兩種方法:一種是,在電路板上加外電路。例如用MCU或CPLD來接收配置數(shù)據(jù),在被動串行(PS)模式

2017-12-13 13:58:10 24009

24009

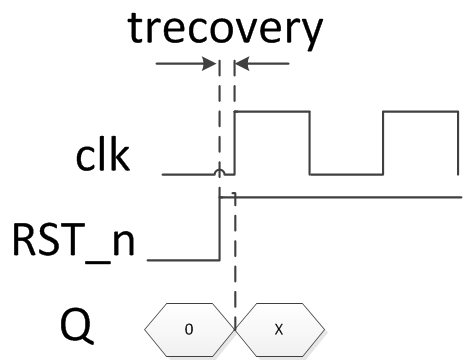

異步復(fù)位同步釋放 首先要說一下同步復(fù)位與異步復(fù)位的區(qū)別。 同步復(fù)位是指復(fù)位信號在時鐘的上升沿或者下降沿才能起作用,而異步復(fù)位則是即時生效,與時鐘無關(guān)。異步復(fù)位的好處是速度快。 再來談一下為什么FPGA設(shè)計中要用異步復(fù)位同步釋放。

2018-06-07 02:46:00 1989

1989 G120故障復(fù)位的方法介紹 1.1通過面板復(fù)位 1.2通過裝置斷電再上電復(fù)位 1.3通過端子命令復(fù)位故障 1.4通過遠(yuǎn)程控制的方式復(fù)位 1.5通過設(shè)置故障自動復(fù)位功能復(fù)位

2018-03-15 10:45:41 37

37 最近在搞430的FLASH的自定義法(利用串口)程序燒寫,燒寫完成后斷電復(fù)位,reset按鍵就可以運行新的程序。但是和學(xué)長交流了一下,這種方法不夠好,希望有一種軟復(fù)位的方式。

2018-05-20 10:04:00 6348

6348 對于xilinx 7系列的FPGA而言,flip-flop支持高有效的異步復(fù)/置位和同步復(fù)位/置位。對普通邏輯設(shè)計,同步復(fù)位和異步復(fù)位沒有區(qū)別,當(dāng)然由于器件內(nèi)部信號均為高有效,因此推薦使用高有效的控制信號,最好使用高有效的同步復(fù)位。輸入復(fù)位信號的低有效在頂層放置反相器可以被吸收到IOB中。

2018-07-13 09:31:00 6091

6091 在實際設(shè)計中,由于外部阻容復(fù)位時間短,可能無法使FPGA內(nèi)部復(fù)位到理想的狀態(tài),所以今天介紹一下網(wǎng)上流行的復(fù)位邏輯。

2018-08-07 09:17:18 10969

10969 某些系統(tǒng)允許復(fù)位,但對外設(shè)又有特殊要求:某一個IO狀態(tài)不能因為復(fù)位而改變,某一個定時器計數(shù)器不能改變等。

2018-08-08 11:32:36 98762

98762

FPGA的可靠復(fù)位是保證系統(tǒng)能夠正常工作的必要條件,本文對FPGA設(shè)計中常用的復(fù)位設(shè)計方法進(jìn)行了分類、分析和比較,并針對各種復(fù)位方式的特點,提出了如何提高復(fù)位設(shè)計可靠性的方法。

2018-08-08 15:14:23 10154

10154 問題:8051單片機(jī)復(fù)位后,各寄存器的初始狀態(tài)如何?復(fù)位方法有幾種?

解答:8051單片機(jī)復(fù)位后機(jī)器的初始狀態(tài),即各寄存器的狀態(tài):PC之外,復(fù)位操作還對其它一些特殊功能寄存器有影響。

2018-12-19 15:09:45 11027

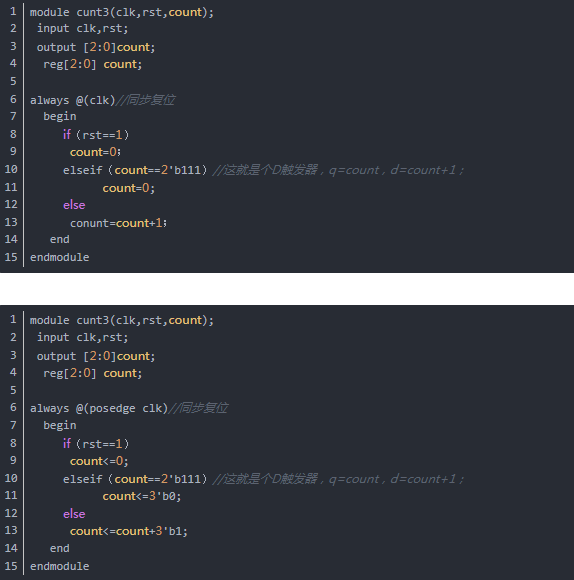

11027 分析:首先,我們可以看到有哪些信號。復(fù)位rst 、計數(shù)器3位的、時鐘信號。(用到2路選擇器。復(fù)位和不復(fù)位)

其次,怎樣實現(xiàn),一個時鐘過來,記一次數(shù)就是加一次,保存(用到D觸發(fā)器),滿之后為0;

2019-02-01 07:08:00 2354

2354

一開始接觸到FPGA,肯定都知道”復(fù)位“,即簡單又復(fù)雜。簡單是因為初學(xué)時,只需要按照固定的套路——按鍵開關(guān)復(fù)位,見寄存器就先低電平復(fù)位一次,這樣一般情況可以解決99%的問題,甚至簡單的設(shè)計,就不可能有問題。

2019-02-17 10:49:53 7670

7670

FPGA設(shè)計中,層次結(jié)構(gòu)設(shè)計和復(fù)位策略影響著FPGA的時序。在高速設(shè)計時,合理的層次結(jié)構(gòu)設(shè)計與正確的復(fù)位策略可以優(yōu)化時序,提高運行頻率。

2019-02-15 15:15:53 849

849 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA教程之FPGA系統(tǒng)設(shè)計的主要思路和方法初探資料說明包括了:1.FPGA的適用領(lǐng)域及選型FPGA系統(tǒng)設(shè)計典型流程,2.FPGA邏輯設(shè)計方法 弓|入ASIC的設(shè)計方法,3.FPGA設(shè)計的常用技巧,4.FPGA系統(tǒng)設(shè)計中的對與錯

2019-04-04 17:19:58 53

53 本文檔的詳細(xì)介紹的是FPGA設(shè)計有哪些良好的設(shè)計方法及誤區(qū)內(nèi)容包括了:1.FPGA的適用領(lǐng)域及選型,2.FPGA系統(tǒng)設(shè)計典型流程,3.FPGA邏輯設(shè)計良好設(shè)計方法一引入ASIC的設(shè)計方法,4.FPGA設(shè)計的常用技巧,5.FPGA系統(tǒng)設(shè)計中的誤區(qū)

2019-04-18 17:30:04 23

23 單片機(jī)軟復(fù)位有什么好的方法?如從機(jī)收到復(fù)位命令(軟件命令),程序怎么使機(jī)器復(fù)位?雖然要使軟件始終處于可控狀態(tài), 最好不要用“復(fù)位”,因為復(fù)位是純硬件過程,軟件是不可控的。但是我們還是要討論方法,一般

2019-09-25 17:17:00 3

3 本設(shè)計采用FPGA技術(shù),在FPGA中實現(xiàn)8051單片機(jī)的軟核,將外部SPI Flash中的代碼數(shù)據(jù)加載到FPGA內(nèi)部ram,然后復(fù)位 MC8051,實現(xiàn)外部flash啟動MC8051。

2019-06-11 17:47:00 3

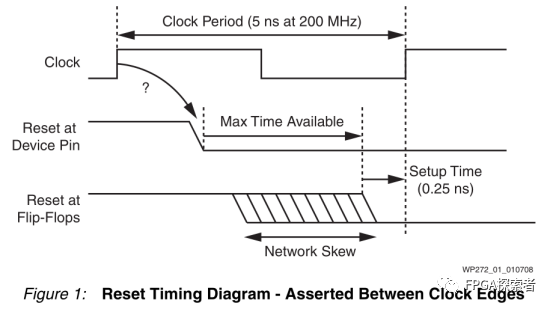

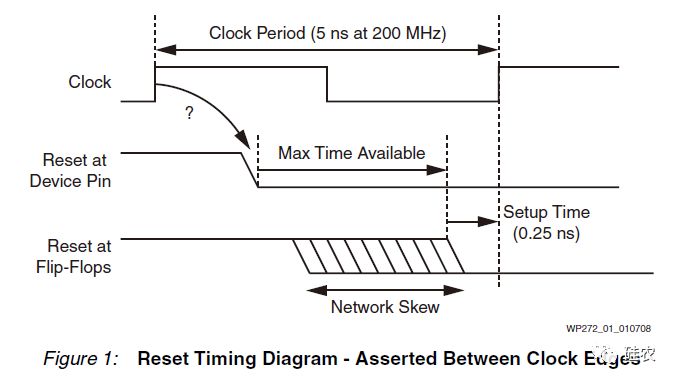

3 復(fù)位信號的有效時長必須大于時鐘周期,才能真正被系統(tǒng)識別并完成復(fù)位任務(wù)。同時還要考慮,諸如:clk skew,組合 邏輯路徑延時,復(fù)位延時等因素。

2019-08-21 17:51:49 1745

1745 本文主要介紹了熱過載繼電器接線圖及復(fù)位方法。

2019-10-28 10:38:15 65415

65415 先用FPGA的外部輸入時鐘clk將FPGA的輸入復(fù)位信號rst_n做異步復(fù)位、同步釋放處理,然后這個復(fù)位信號輸入PLL,同時將clk也輸入PLL。設(shè)計的初衷是在PLL輸出有效時鐘之前,系統(tǒng)的其他部分都保持復(fù)位狀態(tài)。

2020-03-29 17:19:00 2456

2456

FPGA開發(fā)中,一種最常用的復(fù)位技術(shù)就是“異步復(fù)位同步釋放”,這個技術(shù)比較難以理解,很多資料對其說得并不透徹,沒有講到本質(zhì),但是它又很重要,所以對它必須理解,這里給出我的看法。

2020-08-18 13:56:00 1114

1114

最近看 advanced fpga 以及 fpga 設(shè)計實戰(zhàn)演練中有講到復(fù)位電路的設(shè)計,才知道復(fù)位電路有這么多的門道,而不是簡單的外界信號輸入系統(tǒng)復(fù)位。 流程: 1. 異步復(fù)位: 優(yōu)點:⑴大多數(shù)

2020-10-30 12:17:55 323

323 最近看 advanced fpga 以及 fpga 設(shè)計實戰(zhàn)演練中有講到復(fù)位電路的設(shè)計,才知道復(fù)位電路有這么多的門道,而不是簡單的外界信號輸入系統(tǒng)復(fù)位。

2020-12-22 12:54:00 13

13 接觸FPGA的朋友們都知道“復(fù)位”,即簡單又復(fù)雜。簡單是因為初學(xué)時,只需要按照固定的套路——按鍵開關(guān)復(fù)位,見寄存器就先低電平復(fù)位一次,這樣一般情況可以解決99%的問題,甚至簡單的設(shè)計,就不可能有問題。復(fù)雜是因為復(fù)位本身是對大規(guī)模的硬件單元進(jìn)行一種操作,必須要結(jié)核底層的設(shè)計來考慮問題。

2021-04-03 09:34:00 7995

7995 電子發(fā)燒友網(wǎng)為你提供FPGA設(shè)計中常用的復(fù)位設(shè)計資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-10 08:40:04 40

40 臨床醫(yī)學(xué)中,股骨粗隆間骨折復(fù)位應(yīng)同時滿足對位和對線的醫(yī)學(xué)需求,現(xiàn)有計算杋輔助復(fù)位方法不能較好支持。為此提出一種基于對位對線的粗隆間骨折計算機(jī)輔助復(fù)位方法,以碎骨三角網(wǎng)格模型為拼接對彖,通過充分利用

2021-06-04 15:43:01 7

7 基于FPGA的小波濾波抑制復(fù)位噪聲方法

2021-07-01 14:42:09 24

24 對于硬件設(shè)計來說,復(fù)位電路是必不可少的一部分,為了確保微機(jī)系統(tǒng)中電路穩(wěn)定可靠工作,復(fù)位電路的第一功能是上電復(fù)位。在 FPGA 設(shè)計中,復(fù)位起到的是同步信號的作用,能夠?qū)⑺械拇鎯υO(shè)置成已知狀態(tài)

2021-11-06 09:20:57 20

20 異步復(fù)位,同步釋放的理解目錄目錄 同步復(fù)位和異步復(fù)位 異步復(fù)位 同步復(fù)位 那么同步復(fù)位和異步復(fù)位到底孰優(yōu)孰劣呢? 異步復(fù)位、同步釋放 問題1 問題2 問題3 問題4 問題5 參考資料同步

2022-01-17 12:53:57 4

4 說到復(fù)位,我們都不會陌生,系統(tǒng)基本都有一個復(fù)位按鍵。復(fù)位的種類有很多:上電復(fù)位、掉電復(fù)位、復(fù)位引腳復(fù)位、看門狗復(fù)位、軟件復(fù)位等。本文探討的就是在stm32中復(fù)位電路如何設(shè)計。

STM32介紹

2022-02-11 15:10:58 45

45 首先回想一下,在平常的設(shè)計中我們是不是經(jīng)常采用同步復(fù)位或者異步復(fù)位的寫法,這一寫法似乎都已經(jīng)形成了肌肉記憶----每次我們寫always塊的時候總是會對所有的寄存器寫一個復(fù)位賦初值的語句。

2022-02-19 19:10:32 2092

2092 說到復(fù)位,我們都不會陌生,對于一個MCU系統(tǒng),復(fù)位電路是必不可少的一部分。復(fù)位的種類有很多:上電復(fù)位、低電壓復(fù)位、引腳復(fù)位、看門狗復(fù)位、軟件復(fù)位等等。本文說的內(nèi)核復(fù)位是軟件復(fù)位的一種。

2022-03-14 12:04:24 1496

1496

在這些情況下,復(fù)位信號的變化與FGPA芯片內(nèi)部信號相比看起來是及其緩慢的,例如,復(fù)位按鈕產(chǎn)生的復(fù)位信號的周期至少是在毫秒級別的,而我們FPGA內(nèi)部信號往往是納米或者微秒級別的。

2022-05-06 10:48:45 2462

2462 有人說FPGA不需要上電復(fù)位電路,因為內(nèi)部自帶上電復(fù)位信號。也有人說FPGA最好加一個上電復(fù)位電路,保證程序能夠正常地執(zhí)行。不管是什么樣的結(jié)果,這里先把一些常用的FPGA復(fù)位電路例舉出來,以作公示。

2023-03-13 10:29:49 1585

1585 FPGA設(shè)計中幾乎不可避免地會用到復(fù)位信號,無論是同步復(fù)位還是異步復(fù)位。我們需要清楚的是復(fù)位信號對時序收斂、資源利用率以及布線擁塞都有很大的影響。

2023-03-30 09:55:34 806

806 。 下面將討論FPGA/CPLD的復(fù)位電路設(shè)計。 2、分類及不同復(fù)位設(shè)計的影響 根據(jù)電路設(shè)計,復(fù)位可分為異步復(fù)位和同步復(fù)位。 對于異步復(fù)位,電路對復(fù)位信號是電平敏感的,如果復(fù)位信號受到干擾,如出現(xiàn)短暫的脈沖跳變,電路就會部分或全部被

2023-04-06 16:45:02 782

782 本系列整理數(shù)字系統(tǒng)設(shè)計的相關(guān)知識體系架構(gòu),為了方便后續(xù)自己查閱與求職準(zhǔn)備。在FPGA和ASIC設(shè)計中,對于復(fù)位這個問題可以算是老生常談了,但是也是最容易忽略的點。本文結(jié)合FPGA的相關(guān)示例,再談一談復(fù)位。

2023-05-12 16:37:18 3347

3347

SoC設(shè)計中通常會有“全局”同步復(fù)位,這將影響到整個設(shè)計中的大多數(shù)的時序設(shè)計模塊,并在同一時鐘沿同步釋放復(fù)位。

2023-05-18 09:55:33 145

145

在FPGA設(shè)計中,復(fù)位電路是非常重要的一部分,它能夠確保系統(tǒng)從初始狀態(tài)開始啟動并保證正確運行。

2023-05-22 14:21:08 577

577

本文將探討在? FPGA ?設(shè)計中添加復(fù)位輸入的一些后果。 本文將回顧使用復(fù)位輸入對給定功能進(jìn)行編碼的一些基本注意事項。設(shè)計人員可能會忽略使用復(fù)位輸入的后果,但不正確的復(fù)位策略很容易造成重罰。復(fù)位

2023-05-25 00:30:01 483

483 有人說FPGA不需要上電復(fù)位電路,因為內(nèi)部自帶上電復(fù)位信號。也有人說FPGA最好加一個上電復(fù)位電路,保證程序能夠正常地執(zhí)行。不管是什么樣的結(jié)果,這里先把一些常用的FPGA復(fù)位電路例舉出來,以作公示。

2023-05-25 15:50:45 2110

2110

盡量少使用復(fù)位,特別是少用全局復(fù)位,能不用復(fù)位就不用,一定要用復(fù)位的使用局部復(fù)位;

2023-06-21 09:55:33 1337

1337

對于復(fù)位信號的處理,為了方便我們習(xí)慣上采用全局復(fù)位,博主在很長一段時間內(nèi)都是將復(fù)位信號作為一個I/O口,通過撥碼開關(guān)硬件復(fù)位。

2023-06-21 10:39:25 651

651

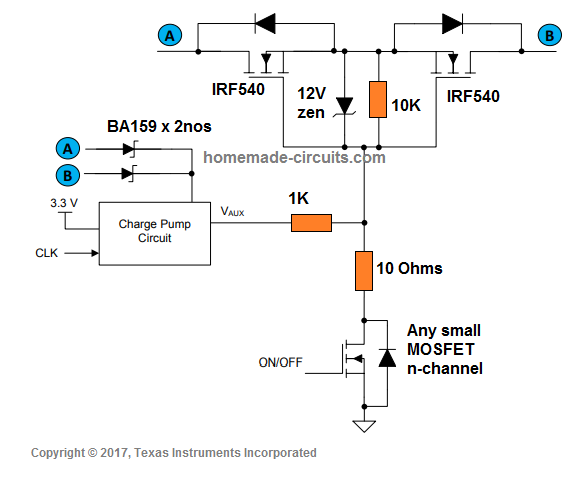

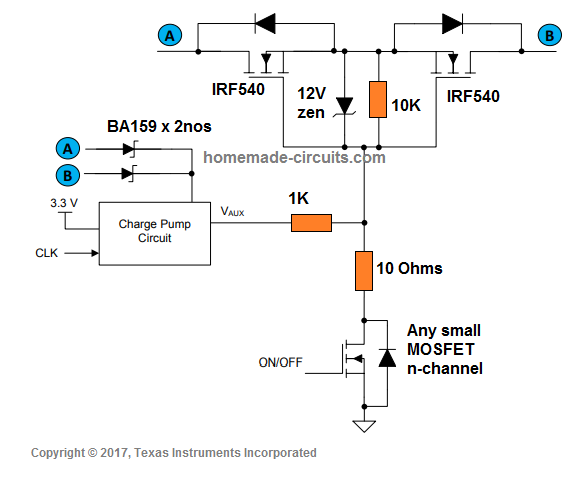

在這個設(shè)計中,我們看到了使用N溝道MOSFET實現(xiàn)BPS電路的理想方法。

2023-06-27 17:29:31 599

599

能不復(fù)位盡量不用復(fù)位,如何判斷呢?如果某個模塊只需要上電的時候復(fù)位一次,工作中不需要再有復(fù)位操作,那么這個模塊可以不用復(fù)位,用上電初始化所有寄存器默認(rèn)值

2023-06-28 14:44:46 526

526

點擊上方 藍(lán)字 關(guān)注我們 系統(tǒng)的復(fù)位對于系統(tǒng)穩(wěn)定工作至關(guān)重要,最佳的復(fù)位方式為:異步復(fù)位,同步釋放。以下是轉(zhuǎn)載博客,原文標(biāo)題及鏈接如下: 復(fù)位最佳方式:異步復(fù)位,同步釋放 異步復(fù)位; 異步

2023-09-09 14:15:01 282

282

中穎M0+內(nèi)核芯片軟件模擬內(nèi)核復(fù)位的方法

2023-09-27 15:27:38 608

608

如果FPGA沒有外部時鐘源輸入,可以通過調(diào)用STARTUP原語,來使用FPGA芯片內(nèi)部的時鐘和復(fù)位信號,Spartan-6系列內(nèi)部時鐘源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

2023-10-27 11:26:56 973

973

電子發(fā)燒友App

電子發(fā)燒友App

評論