本文主要介紹的是FPGA的片上資源使用情況,分別是從組合邏輯及時序邏輯來詳細的分析。

2018-04-18 09:06:24 15422

15422

數據。 對于第一種方法,FPGA 包括LUT/FF/RAM 等資源,分析各種資源等效門數時,總原則是等效原則,就是實現相同的功能,在標準門陣列中需要的門數就是FPGA 該資源等效門數,例如實現一個帶

2012-08-11 10:29:07

等效門數的估計方法。1.計算邏輯陣列的等效門數估算EP20K1000E 的門數時,把FPGA 特定資源和LCA300K 標準邏輯陣列的門數(LSILCA300K Data Book)比較,可以對FPGA

2012-03-01 10:08:53

是整個FPGA學習生涯的必經之路。我個人建議在選擇FPGA的時候,應該抓住如下幾個原則:1、選擇主流廠家的流行的型號,這樣更容易獲取學習資源。選擇一家主流公司的FPGA芯片:在國內目前來說,主流

2020-09-04 10:10:49

芯片。

內部互聯線(Interconnects):用于連接上述的各種資源。

而ASIC是為特定應用定制的硬件電路,其設計和制造過程是一次性的。因此,ASIC的資源與FPGA的對應關系并不直接。

在一些

2024-02-22 09:52:22

即用的硬件資源,統一的軟硬件邏輯開發接口和IP市場,阿里云能夠真正實現FPGA計算資源平民化的承諾。F3硬件架構阿里云FaaS的F3實例在底層硬件上,是使用阿里云自主研發的高性能單卡雙芯片的VU9P

2018-05-22 11:58:12

FPGA中等效邏輯門概念數的計算方法有兩種,一是把FPGA基本單元(如LUT+FF,ESB/BRAM)和實現相同功能的標準門陣列比較,門陣列中包含的門數即為該FPGA基本單元的等效門數,然后乘以

2012-08-10 14:05:35

FPGA中組合邏輯門占用資源過多怎么降低呢?有什么方法嗎?

2023-04-23 14:31:17

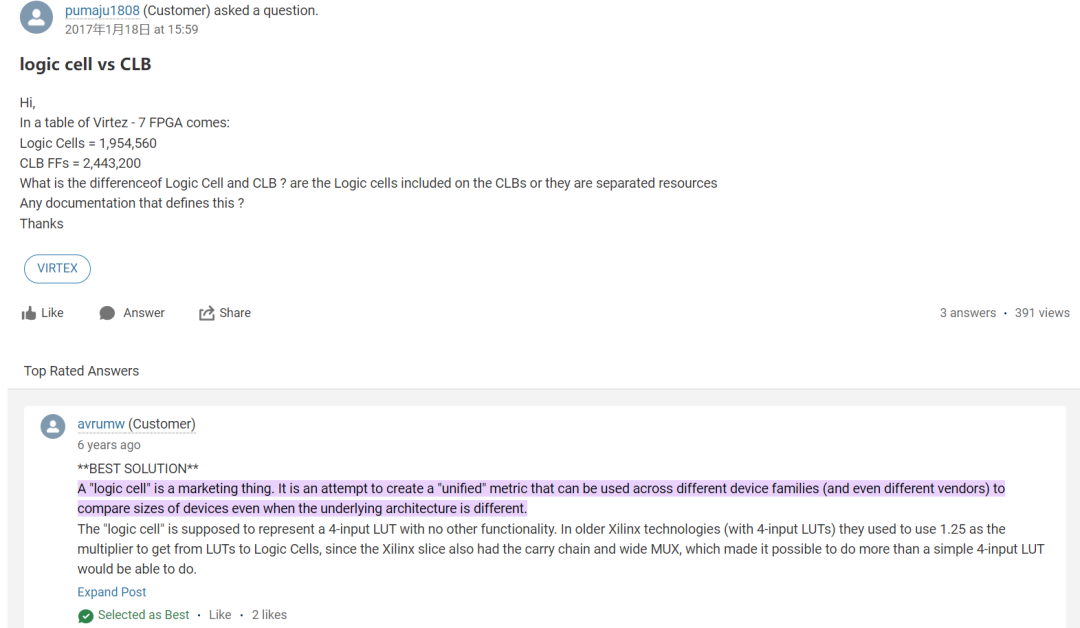

FPGA小白一枚,個人理解的FPGA本質上或者核心就是查找表(LUT),即將所有的函數/方法 轉換為固定的查找表(使用DSP除外)。但是為什么所有的文章提到FPGA全部都注重邏輯門呢?其實FPGA本身內部也沒有多少物理的邏輯門吧?

2019-05-30 10:53:46

產生使用的數據文件(位數據流文件,Bitstream Generation),然后將編程數據下載到FPGA芯片中。其中,芯片編程需要滿足一定的條件,如編程電壓、編程時序和編程算法等方面。邏輯分析儀

2023-12-31 21:15:31

,實際上每一個系列的FPGA都有其相應的內部結構),FPGA芯片主 要由6部分完成,分別為:可編程輸入輸出單元、基本可編程邏輯單元、完整的時鐘管理、嵌入塊式RAM、豐富的布線資源、內嵌的底層功能單元和內嵌

2017-05-09 15:10:02

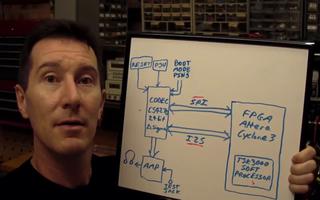

●低成本開發套件●專用參考設計將設計從構思變為產品,更迅速推向市場。采用Cyclone III FPGA,一切皆有可能。(特權同學,版權所有)在過去,衡量一個邏輯器件的資源情況,僅僅看他的邏輯資源便可

2015-04-17 12:05:21

實時時鐘芯片電路設計本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt如圖3.76所示,U2是一顆實時

2015-06-05 12:19:43

邏輯復制與資源共享本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 邏輯復制是一種通過增加面積來改善時序條件

2015-07-05 19:54:33

FPGA開發過程中,離不開時序約束,那么時序約束是什么?簡單點說,FPGA芯片中的邏輯電路,從輸入到輸出所需要的時間,這個時間必須在設定的時鐘周期內完成,更詳細一點,即需要滿足建立和保持時間

2023-11-15 17:41:10

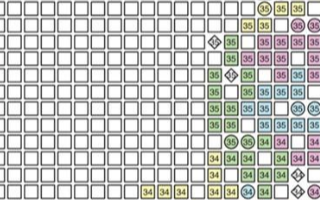

它資源中的過程。 (3)布局與布線:布局是指從映射取出定義的邏輯和輸入輸出塊,并把它們分配到FPGA內部的物理位置,通常基于某種先進的算法,如最小分割、模擬退火和一般的受力方向張弛等來完成;布線是指利用

2018-08-29 09:59:08

的FPGA芯片生產商都提供了內嵌的在線邏輯分析儀(如XilinxISE中的ChipScope、AlteraQuartusII中的SignalTapII以及SignalProb)來解決上述矛盾,它們只需要占用芯片少量的邏輯資源,具有很高的實用價值。

2020-11-30 16:22:59

時序電路)。 在組合邏輯電路中,任何時刻的輸出僅僅取決于該時刻的輸入,與電路原來的狀態無關。這就是組合邏輯電路在邏輯功能上的共同特點。在上一節中,設計的三人表決器就是組合邏輯電路,輸出與輸入一一對應,和其他

2023-02-21 15:35:38

;"小于"這樣的判斷語句, 這樣會明顯增加使用的邏輯單元數量 .看一下報告,資源使用差別很大.例程:always@(posedge clk)begincount1=count1+1

2018-03-24 11:04:41

單元(如邏輯門、觸發器等)和可編程連線資源的集成電路芯片。與傳統的固定功能芯片不同,FPGA具有動態可重構的特性,可以根據用戶需求進行各種不同的配置。

二:FPGA的工作原理

FPGA的核心是由

2023-11-13 15:43:00

組合邏輯:基本邏輯門Wirewire線型的基本描述已在筆記整理(1)中給出了。題目:實現輸入與輸出的連接。答案:module top_module ( input in, output out

2021-09-08 07:32:26

邏輯門及組合邏輯電路實驗實驗目的1. 掌握與非門、或非門、與或非門及異或門的邏輯功能。2. 了解三態門的邏輯功能以及禁止狀態的判別方法。了解三態門的應用。3. 掌握組合邏輯電路的設計和實現方法。4.

2008-09-25 17:28:34

-晶體管邏輯)基于NPN雙極晶體管技術或74Cxxx,74HCxxx,74ACxxx和4000系列邏輯芯片中使用的更快,低功耗CMOS MOSFET晶體管邏輯。下面總結了八個最“標準”的獨立數字邏輯門

2021-01-27 08:00:00

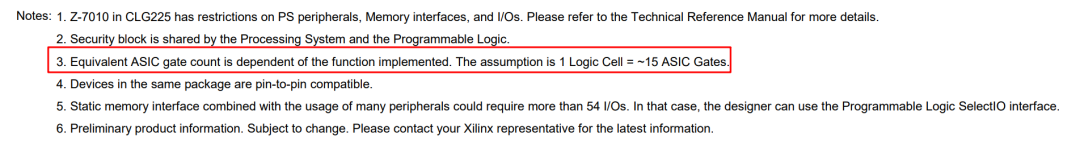

芯片上JESD204B協議對應的引腳(SYSREF、SYNCINB和SERDOUT)與ZYNQ7015芯片中的JESD204 IP核的端口對應相連。

2023-12-15 07:14:52

想找幾款具有推挽式輸出功能的邏輯非門芯片,大家有什么好的推薦么?

2018-04-27 19:52:27

的,芯片系統的總數比人類的數量還多出數十上百倍。芯片大家族里面也分各種不同類型的芯片,從古老的用電子管堆出來的成噸的邏輯門到現在的超

2021-11-01 07:55:44

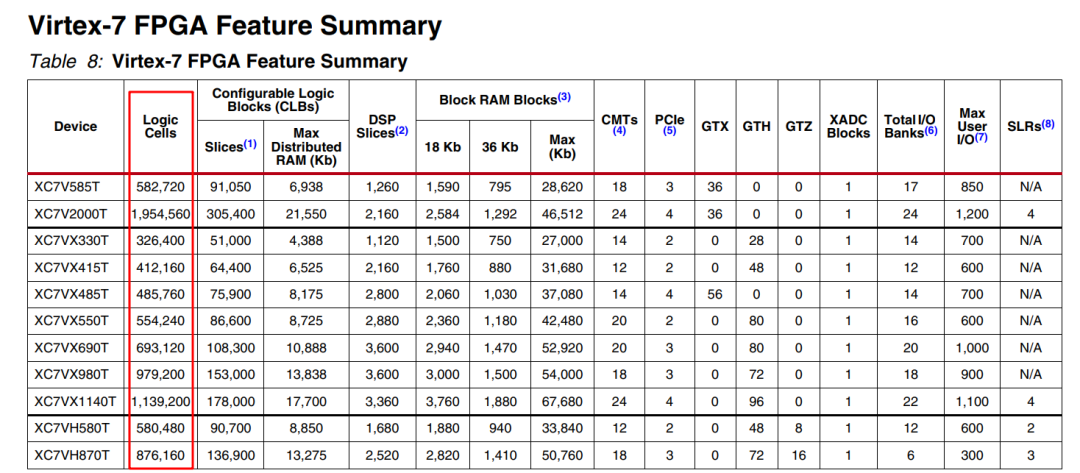

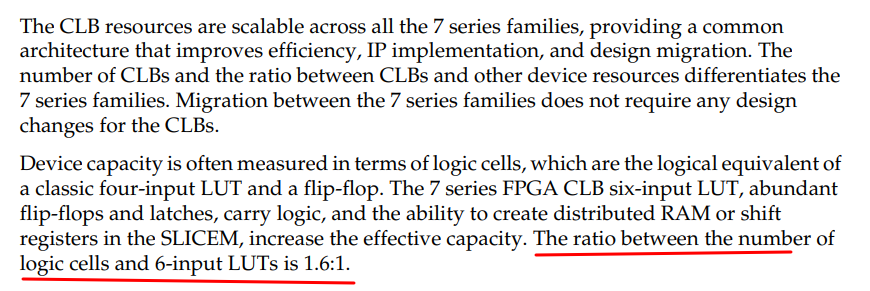

你好。我正在寫一篇技術論文和需要知道LUT和Kintex 7 FPGA芯片中的FF所需的資源。資源可以是晶體管數量,柵極數,芯片面積大小等等。我在一個網站上聽說LUT需要2.5倍的“FPGA門”,但

2019-02-27 13:49:58

芯片設計問題:

1、N300系列的N307-最小配置邏輯門數是多少?

2、另外,N205可否選配DSP-SIMD和FPU模塊?

2023-08-12 06:32:44

TTL邏輯門與普通邏輯門的區別在哪里為什么引入OC門?

2021-03-29 07:23:21

請問大家,pspice的邏輯門模型,比如說與門7408,該怎樣修改其參數?我想修改7408的延遲時間,輸出電平等等,怎么弄?關于右鍵點擊然后edit pspice model的方法,我試過,只是出來

2014-06-24 10:09:17

前言FPGA芯片主 要由6部分完成,分別為:可編程輸入輸出單元(IOB)基本可編程邏輯單元(configurable logic block,CLB) 完整的時鐘管理嵌入塊式RAM豐富的布線資源內嵌

2021-07-26 06:54:01

⑴ 結合Xilinx、Altera 等公司的FPGA 芯片,簡要羅列一下FPGA 內部的資源或專用模塊,并簡要說明這些資源的一些作用或用途。(至少列出5 項,越多越好)⑵ 如果,對內部特定資源,曾有

2012-03-08 11:03:49

邏輯或門是一種數字邏輯電路,僅當其一個或多個輸入為高電平時,其輸出才變為邏輯電平1。“邏輯或門”的輸出Q僅在其所有輸入均為邏輯電平“ 0”時才再次返回“ LOW ”。換句話說,對于邏輯或門,任何“高

2021-01-20 09:00:00

邏輯或門是一種數字邏輯電路,僅當其一個或多個輸入為高電平時,其輸出才變為邏輯電平1。“邏輯或門”的輸出Q僅在其所有輸入均為邏輯電平“ 0”時才再次返回“ LOW ”。換句話說,對于邏輯或門,任何“高

2021-01-21 08:00:00

一.TTLTTL集成電路的主要型式為晶體管-晶體管邏輯門(transistor-transistor logic gate),TTL大部分都采用5V電源.1.輸出高電平Uoh和輸出低電平UolUoh

2016-08-23 21:39:46

FPGA的邏輯電路基礎知識四、邏輯值 邏輯0:表示低電平,對應GND。 邏輯1:表示高電平,對應VCC。 邏輯X:表示未知,可能高電平,可能低電平。 邏輯Z:表示高阻態,外部沒有激勵信號,懸空狀態

2019-12-10 20:32:03

Pango DesignSuite,可支持千萬門級FPGA器件設計開發高云半導體:推出中國首顆55nm嵌入式Flash SRAM非易失性FPGA芯片,實現可編程邏輯器件、嵌入式處理器無縫連接安路

2021-09-10 14:46:09

關于FPGA芯片資源介紹不看肯定后悔

2021-09-18 08:53:05

我用fpga生成的兩路分辨率很高的脈沖,想在fpga外進行邏輯與。對與門參數有什么要求嗎。比如上升沿下降沿的識別能力或者帶寬等等

2019-05-13 10:57:47

邏輯門是數字電路的基礎。各種多姿多彩的邏輯門組合在一起,形成了數字電路的大千世界。實際上,邏輯門反映的是邏輯代數的幾種基本運算,只要你能夠實現這樣的邏輯代數規則,你就能夠用其他設備來實現邏輯門的功能,看!

2019-07-23 07:03:30

可編程邏輯芯片 FPGA 中的CYCLONE IV系列的芯片·主要指標中的速度級數代表什么意思?

2012-09-13 21:29:48

Programmable Gate Array) 。CPLD器件內部含有許多邏輯塊和連線資源,而邏輯塊由與-或陣列和觸發器等構成,邏輯塊的功能由用戶編程決定。邏輯塊之間,邏輯塊與芯片外部可以通過可編程的連線資源

2021-07-13 08:00:00

1、集成邏輯門及其基本應用介紹本實驗涉及到的基本邏輯門有“與門”、“與非門”、“或門”、“或非門”、“異或門”和“同或門”,功能簡單,實驗時使用2個撥動開關模擬邏輯門的輸入信號,通過LED燈的點亮或

2022-07-01 15:18:51

本帖最后由 樂樂leles 于 2019-6-5 11:07 編輯

常用與、或、非邏輯門芯片引腳圖一、或門:74LS32四路二輸入或門74HC27 三路三輸入或非門 二、與門:74LS21二路四輸入與門 74LS11 三輸入與門 三、非門:74LS04

2019-05-24 08:49:59

我發現自己畫的邏輯門遵循我的思路,并希望反映邏輯本身的目的(貼標網)。觀察結果很明顯,這不會導致最佳電路。創建者應用布爾代數來簡化/優化在PSoC芯片中編程的實際邏輯嗎?賈景暉,謝謝。

2019-10-11 07:04:14

在如何使用Arm-2D在小資源Cortex-M處理器芯片中實現圖形界面中,效果器顯示效果和MDK調試代碼怎么關聯?模擬器不是單獨運行在PC環境里的嗎?

2022-08-26 14:40:46

本文使用符合PCI電氣特性的FPGA芯片進行簡化的PCI接口邏輯設計,實現了33MHz、32位數據寬度的PCI從設備模塊的接口功能,節約了系統的邏輯資源,且可以將其它用戶邏輯集成在同一塊芯片,降低了成本,增加了設計的靈活性。

2021-05-08 08:11:59

本文的設計是基于FPGA實現邏輯芯片的功能故障測試。由于FPGA芯片價格的不斷下降和低端芯片的不斷出現,使用FPGA作為主控芯片可以更適合于市場,且有利于對性能進行擴展。實驗表明,該系統設計合理,能對被測芯片進行準確的功能測試。

2021-04-30 06:13:48

于存儲器的不同系統數據,從而實現不同的芯片邏輯功能,可以在很大程度上提高資源利用率。原始配置FPGA的方法是硬件設計者根據需求設計生成配置數據流,然后通過專用配置芯片對FPGA進行配置,例如通過下載

2019-08-07 06:17:30

你好。我是在FPGA上設計系統的初學者。我的fpga是XC7K325T -2 FFG900(knitex - 7系列)我想計算基本15位2輸入加法器的邏輯延遲。如果我能檢查AND門或OR門的延遲等

2020-05-25 07:28:24

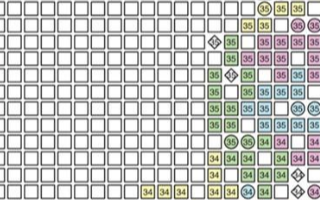

。 解析FPGA的片上資源使用情況 如何分析FPGA芯片上的組合邏輯(LUT)和時序邏輯(REG)的利用率。 一、如何得到LUT與REG的使用比例我們先看一個FPGA工程的編譯結果

2019-06-17 09:03:28

請問怎么將無源器件連接到邏輯門?

2021-04-13 06:48:09

Xilinx 的 CPLD 和 Altera 的 FPGA ,其速度等級的數值越大,反而代表芯片性能越差 溫度等級: 4.價格 在芯片選型時,價格也是特別重要的一個因素,畢竟不同芯片的價格可能相差數倍至數十倍、數百倍。應該在滿足要求的芯片中,挑選性價比最高的一款。

2020-12-23 17:21:03

灌電流是什么?灌電流越大與邏輯門輸出端的低電平有何關系?拉電流是什么?拉電流越大與邏輯門輸出端的高電平有何關系?

2021-10-11 08:53:52

現在我需要一個邏輯門器件,與門和或門。要求是在輸入時間為100ns的脈沖信號(可調),兩個輸入,一個輸出。然后通過這個邏輯門器件之后可以用示波器檢測到。。。新人也不懂 啊,需要什么型號的器件呢?

2018-09-17 16:01:36

描述邏輯門學習套件在這個項目中,您將學習如何構建自己的邏輯門學習套件并了解所有關于不同邏輯門的知識。不是非門用于反轉信號。下面是邏輯門的真值表和繪圖。 和與門用于接收 2 個或更多信號,并且僅在

2022-09-08 07:42:05

用FPGA往SRAM芯片中寫數據重復寫多次才能寫是怎么回事呢?

2023-04-23 11:46:44

芯片上JESD204B協議對應的引腳(SYSREF、SYNCINB和SERDOUT)與ZYNQ7015芯片中的JESD204 IP核的端口對應相連。[/td][td]

2018-09-05 11:45:31

我理解的比較簡單。將代碼燒寫進FPGA,芯片內部的各個邏輯門通過邏輯連線實現邏輯功能,這些邏輯門的輸入是通過查找表獲得的。比如我用到兩個與門和一個或門,對于4輸入的LUT來講,則至少需要兩個LUT。

不知道這樣理解對不對。

還有具體LUT內部是如何實現查找的,請知明人能夠提點提點。

謝謝

2023-04-23 14:12:58

異成門邏輯符號圖/同或門邏輯符號圖

2019-10-23 03:49:43

鐘控傳輸門絕熱邏輯電路和SRAM 的設計本文利用NMOS管的自舉效應設計了一種新的采用二相無交疊功率時鐘的絕熱邏輯電路---鐘控傳輸門絕熱邏輯電路,實現對輸出負載全絕熱方式充放電.依此進一步設計了

2009-08-08 09:48:05

虛擬FPGA邏輯驗證分析儀的設計

隨著FPGA技術的廣泛使用,越來越需要一臺能夠測試驗證FPGA芯片中所下載電路邏輯時序是否正確的儀器。目前,雖然Agilent、Tektronix 等大公司生

2008-10-15 08:56:31 575

575

本文簡要的分析FPGA芯片中豐富的布線資源 。FPGA芯片內部有著豐富的布線資源,根據工藝、長度、寬度和分布位置的不同而劃分為4類不同的類別。

2012-12-17 17:28:41 3491

3491 隨著現場可編程門陣列( FPGA)芯片在商業、軍事、航空航天等領域越來越廣泛的應用,其可靠性和可測試性也顯得尤為重要。本文介紹一種基于SRAM結構FPGA邏輯資源的測試編程方法,并以Xilinx公司的XC4000系列為例,在BC3192V50數模混合集成電路測試系統上,通過從串模式,實現數據的配置和測試。

2017-11-23 14:48:02 4583

4583 布線資源連通FPGA內部的所有單元,而連線的長度和工藝決定著信號在連線上的驅動能力和傳輸速度。FPGA芯片內部有著豐富的布線資源,根據工藝、長度、寬度和分布位置的不同而劃分為4類不同的類別。第一類

2017-12-05 11:48:44 8

8 在使用FPGA過程中,通常需要對資源做出評估,下面簡單談談如何評估FPGA的資源。

2019-02-15 15:09:05 3580

3580 FPGA由邏輯單元、RAM、乘法器等硬件資源組成,通過將這些硬件資源合理組織,可實現乘法器、寄存器、地址發生器等硬件電路。

2019-12-27 07:05:00 1613

1613

人工智能的三大支撐是硬件、算法和數據,其中硬件指的是運行 AI 算法的芯片與相對應的計算平臺。在硬件方面,目前主要是使用 GPU 并行計算神經網絡,同時,還有 FPGA 和 ASIC 也具有未來異軍突起的潛能。

2019-09-03 17:55:23 2421

2421 雖然很多 FPGA 工程師都是寫代碼,但是作為硬件編程工程師,如果不熟悉 FPGA 的底層資源和架構,是很難寫出高質量的代碼——至少很難寫出復雜邏輯的高質量代碼,也很難站在系統的層面去考慮芯片的選型等問題。那熟悉 FPGA 架構,首先最主要的一點,我們先來了解 FPGA 的 IO。

2020-07-16 17:53:02 9031

9031

在本輔導教材中,將重點講解如何將一個設計項目物理地實現于FPGA 芯片中。我們將展示如何用手工的方法選擇器件封裝的引腳,并且把這些引腳用做電路的輸入和輸出信號,此外還將描述如何使用Quartus II 編程器模塊把編譯完的電路傳送到所選擇的FPGA芯片中。

2020-10-27 16:26:00 20

20 在FPGA中block ram是很常見的硬核資源,合理的利用這些硬件資源一定程度上可以優化整個設計,節約資源利用率,充分開發FPGA芯片中的潛在價值,本文結合安路科技FPGA做簡單總結,說明基本原理。

2020-12-24 14:28:09 916

916 本篇咱們接著介紹I/O邏輯資源,先貼上兩張圖。圖1為HPBANK的I/O模塊,圖2為HRBANK的I/O模塊,兩者區別在于后者無ODELAYE模塊。

2020-12-29 17:27:00 3

3 介紹IO口與FPGA管腳對應關系表。

2021-03-18 10:02:26 12

12 FPGA_ASIC-S698MSoC芯片中EDAC模塊的設計與實現(第四屆星載電源技術學術研討會)-該文檔為FPGA_ASIC-S698MSoC芯片中EDAC模塊的設計與實現總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-09-15 11:05:19 6

6 FPGA-SoC芯片中EDAC模塊的設計與實現(深圳市宇衡源電源技術)-該文檔為FPGA-SoC芯片中EDAC模塊的設計與實現簡介文檔,是一份還算不錯的參考文檔,感興趣的可以下載看看,,,,,,,,,,,,,,,,,

2021-09-27 14:32:18 13

13 (06)FPGA資源評估1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA資源評估5)結語1.2 FPGA簡介FPGA(Field Programmable Gate

2021-12-29 19:40:45 6

6 FPGA芯片本身就具有可以反復擦寫的特性,允許FPGA開發者編寫不同的代碼進行重復編程,而FPGA可重構技術正是在這個特性之上,采用分時復用的模式讓不同任務功能的Bitstream文件使用FPGA芯片內部的各種邏輯資源

2022-04-26 10:38:54 2872

2872 而且現在的LUT都是4輸入或者6輸入,可以做成邏輯門的組合,跟普通的邏輯門個數肯定不會是一對一關系。今天我們來看下這個關系如果對應。

2022-11-01 09:11:29 643

643 關于 FPGA 的 IO資源分析共分為三個系列進行具體闡述,分別為: IO資源:分析FPGA IO資源的電氣特性; IO邏輯資源:分析FPGA的輸入輸出數據寄存器、DDR工作方式、可編程輸入延時

2022-12-13 13:20:06 1099

1099 FPGA芯片說明書中,包含了可編程邏輯模塊的數量、固定功能邏輯模塊(如乘法器)的數目及存儲器資源(如嵌入式RAM)的大小。FPGA芯片中還有很多其它的部分,但是以上指標通常是為特定應用選擇和比較FPGA時,最重要的參考指標。

2023-01-09 09:28:46 899

899 FPGA芯片的工作原理主要基于其內部的可配置邏輯單元和連線資源。包括以下工作原理: 首先,FPGA內部包含可配置邏輯模塊(CLB)、輸出輸入模塊(IOB)和內部連線(Interconnect)三個

2024-03-14 17:17:51 117

117 fpga芯片是什么芯片 FPGA芯片(Field Programmable Gate Array)即現場可編程邏輯門陣列,是一種特殊的邏輯芯片。它是在PAL(可編程邏輯陣列)、GAL(通用陣列邏輯

2024-03-14 17:25:24 169

169 FPGA(現場可編程門陣列)芯片中的觸發器是一種重要的存儲元件,它在數字電路設計中起著至關重要的作用。觸發器的主要功能是存儲和同步數字信號,確保電路在正確的時刻捕獲和保持信號狀態。

2024-03-15 15:20:48 116

116

電子發燒友App

電子發燒友App

評論