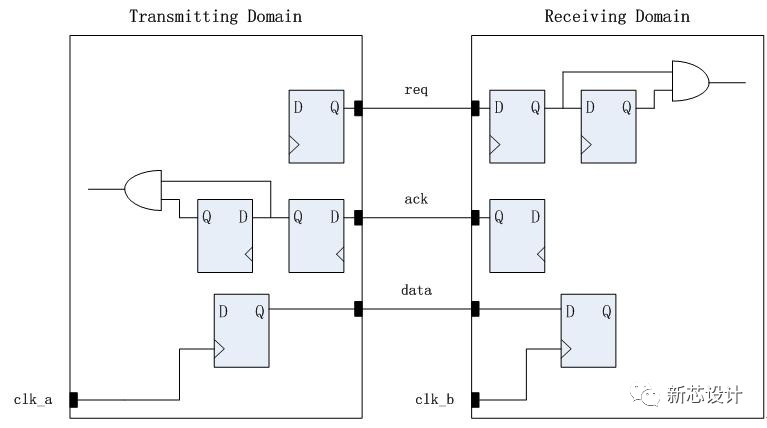

在FPGA 上設計一個高性能、靈活的、面積小的通信體系結構是一項巨大的挑戰。大多數基于FPGA 的片上網絡都是運行在一個單一時鐘下。隨著FPGA 技術的發展,Xilinx 公司推出了Virtex-4 平臺

2011-10-21 16:13:51 1270

1270

針對不同類型的器件,Xilinx公司提供的全局時鐘網絡在數量、性能等方面略有區別,下面以Virtex-4系列芯片為例,簡單介紹FPGA全局時鐘網絡結構。

2013-11-28 18:49:00 12149

12149

時鐘網絡反映了時鐘從時鐘引腳進入FPGA后在FPGA內部的傳播路徑。

2019-09-10 15:12:31 6343

6343

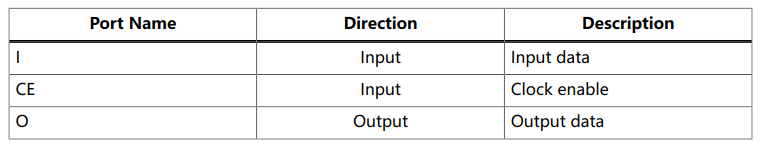

引言:本文我們介紹一下全局時鐘資源。全局時鐘是一個專用的互連網絡,專門設計用于到達FPGA中各種資源的所有時鐘輸入。

2022-07-14 09:15:35 1538

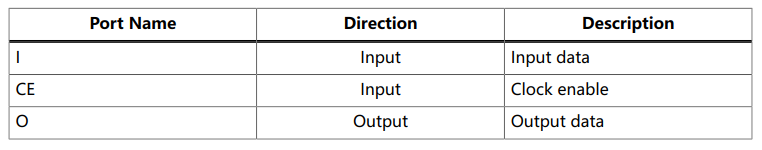

1538 7系列FPGA擁有豐富的時鐘資源。各種緩沖器類型、時鐘輸入管腳和時鐘連接,可以滿足許多不同的應用需求。選擇合適的時鐘資源可以改善布線、性能和一般FPGA資源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 2475

2475 7系列FPGA時鐘資源通過專用的全局和區域I/O和時鐘資源管理符合復雜和簡單的時鐘要求。時鐘管理塊(CMT)提供時鐘頻率合成、減少偏移和抖動過濾等功能。非時鐘資源,如本地布線,不推薦用于時鐘功能。

2022-07-28 09:07:34 1276

1276 “全局時鐘和第二全局時鐘資源”是FPGA同步設計的一個重要概念。合理利用該資源可以改善設計的綜合和實現效果;如果使用不當,不但會影響設計的工作頻率和穩定性等,甚至會導致設計的綜合、實現過程出錯

2023-07-24 11:07:04 655

655

通過上一篇文章“時鐘管理技術”,我們了解Xilinx 7系列FPGA主要有全局時鐘、區域時鐘、時鐘管理塊(CMT)。 通過以上時鐘資源的結合,Xilinx 7系列FPGA可實現高性能和可靠的時鐘分配

2023-08-31 10:44:31 1032

1032

嗨,我使用的是virtex 5 FPGA。我正在運行外部10Mhz時鐘信號來運行二進制計數器。當我嘗試使用DCM時,它表示最低頻率為32MHz。可以將此信號運行到FPGA的i / o輸入并通過全局

2019-02-21 10:32:51

FPGA 時鐘分配網絡設計技術

2012-08-20 17:15:27

FPGA的任意一個管腳都可以作為時鐘輸入端口,但是FPGA專門設計了全局時鐘,全局時鐘總線是一條專用總線,到達片內各部分觸發器的時間最短,所以用全局時鐘芯片工作最可靠,但是如果你設計的時候時鐘太多

2012-02-29 09:46:00

線將會是一個和時鐘一樣多扇出的網絡,如此多的扇出,時鐘信號是采用全局時鐘網絡的,那么復位如何處理?有人提出用全局時鐘網絡來傳遞復位信號,但是在FPGA設計中,這種方法還是有其弊端。一是無法解決復位結束

2019-05-17 08:00:00

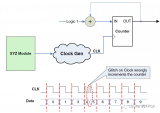

現了,將時鐘的布線成樹形結構,使得到達每一個邏輯單元的時鐘信號同相,這樣就可以實現同步,這就是全局時鐘網絡,GC_CLK。也就是說GC_CLK在FPGA內部是固定的位置,與其對應的引腳也就固定了,這樣

2019-07-09 08:00:00

FPGA的全局時鐘是什么?什么是第二全局時鐘?在FPGA的主配置模式中,CCLK信號是如何產生的?

2021-11-01 07:26:34

,這個時間差過大是很要命的。因此,FPGA器件內部設計了一些稱之為“全局時鐘網絡”的走線池。通過這種專用時鐘網絡走線,同一時鐘到達不同寄存器的時間差可以被控制到很小的范圍內。而我們又如何能保證輸入的時鐘

2019-04-12 01:15:50

,這個時間差過大是很要命的。因此,FPGA器件內部設計了一些稱之為“全局時鐘網絡”的走線池。通過這種專用時鐘網絡走線,同一時鐘到達不同寄存器的時間差可以被控制到很小的范圍內。而我們又如何能保證輸入的時鐘

2015-04-08 10:52:10

,通過這些專用引腳輸入的時鐘信號,在FPGA內部可以很容易的連接到全局時鐘網絡上。所謂的全局時鐘網絡,是FPGA內部專門用于走一些有高扇出、低時延要求的信號,這樣的資源相對有限,但是非常實用。FPGA

2015-04-24 08:17:00

的時鐘源是來自于FPGA的PLL。為什么PLL輸出的時鐘一定要有專門的這樣一對引腳呢?和前面的全局時鐘網絡存在的意義有異曲同工之妙。PLL到這對引腳上的延時相對是比較受控的,目的就是為了得到更低延時、更穩

2015-05-04 11:45:05

FPGA時鐘問題 2010-06-11 15:55:39分類: 嵌入式1.FPGA的全局時鐘是什么?FPGA的全局時鐘應該是從晶振分出來的,最原始的頻率。其他需要的各種頻率都是在這個基礎上利用PLL或者其他分頻手段得到的。

2021-07-29 09:25:57

u_fpga_dut_clk / rg3_bufg.O.34562錯誤:[放置30-660]全局時鐘刺激超額訂閱。以下時鐘網絡需要在SLR 3中使用全局時鐘脊柱18:u_fpga

2018-10-24 15:27:38

全局時鐘資源怎么使用?全局時鐘資源的例化方法有哪幾種?

2021-05-06 07:28:18

FPGA全局時鐘資源一般使用全銅層工藝實現,并設計了專用時鐘緩沖與驅動結構,從而使全局時鐘到達芯片內部的所有可配置單元(CLB)、I/O單元(IOB)和選擇性塊RAM(Block Select

2019-10-22 06:01:34

時鐘信號從普通IO管腳輸入怎么進行處理,時鐘從普通IO管腳進入FPGA后能進入全局時鐘網絡嗎?因為只有全局時鐘管腳后面連接有IBUFG/IBUFGDS緩沖單元,如果差分時鐘信號從普通IO管腳進入后

2012-10-11 09:56:33

畫一個圓形的板子,怎么走線也是大的圓弧,這樣好看一些,如果放置圓弧,不顯示網絡屬性

2018-12-18 13:46:02

轉帖蛇形走線在高速板比較常見的一種走線方式。通過走蛇形線的方式可以比較好的保證兩條等長線的長度相等。今天我們就來介紹下在Altium Desinger中怎么進行蛇形線走線。布線完成后進行蛇形線調整

2017-11-23 11:14:42

下面從直角走線、差分走線、蛇形線三個方面來闡述PCB LAYOUT的走線。

2021-03-17 07:25:46

USB接口和網絡芯片應用,這里面的信號線需要走等長線嗎。如果需要怎么走等長線,使用的是AD18版本。

2023-10-26 07:10:37

`allegro這種情況T形狀走線怎么走合適呢?能不能把直角變成圓弧?或者怎么樣好呢?`

2018-04-17 15:42:27

pcb布局,走線方面,有什么建議嗎,該怎么怎么走,怎么提高效率

2016-10-15 14:51:34

的原理圖 在通常的 FPGA設計中對時鐘偏差的控制主要有以下幾種方法: ⑴ 控制時鐘信號盡量走可編程邏輯器件的的全局時鐘網絡。 在可編程邏輯器件中一般都有專門的時鐘驅動器及全局時鐘網絡,不同種

2012-03-05 14:29:00

兩個電機的小車,怎么走直線,請大佬解答。空stm32給不同的pwm占空比,同時小車上同編碼器測速,用pid算法怎么調節,設定一個固定的值讓兩個電機都去靠近這個值,還是怎么設置一個動態的值,達到比較好的效果,謝謝

2018-03-24 19:41:52

謝謝大家了,另外Altera FPGA從專用時鐘輸入port進來的時鐘信號就自動會走全局時鐘網絡嗎?

2017-07-01 10:12:36

請問各位大俠 用Altera公司的FPGA基于Quartus II和SOPC 和Nios II怎么在GPIO擴展口產生一個時鐘?非常感謝

2011-04-13 20:15:22

源到不同寄存器間的延時也可能存在較大偏差(我們通常稱為時鐘網絡延時),而我們知道,這個時間差過大是很要命的。因此,FPGA器件內部設計了一些稱之為“全局時鐘網絡”的走線池。通過這種專用時鐘網絡走線

2016-07-22 18:44:57

引腳輸入的時鐘信號,在FPGA內部可以很容易的連接到全局時鐘網絡上。所謂的全局時鐘網絡,是FPGA內部專門用于走一些有高扇出、低時延要求的信號,這樣的資源相對有限,但是非常實用。FPGA的時鐘和復位

2016-08-08 17:31:40

入行兩年多了,現在很迷茫不知道以后的職業生涯該怎么走,做硬件的 但是沒有具體偏向如果說偏向的話應該是嵌入式硬件吧,求大神指點迷津

2015-05-26 12:57:06

稱之為“全局時鐘網絡”的走線池。通過這種專用時鐘網絡走線,同一時鐘到達不同寄存器的時間差可以被控制到很小的范圍內。而我們又如何能保證輸入的時鐘信號能夠走“全局時鐘網絡”呢?有多種方式,對于外部輸入的時鐘

2017-10-18 21:42:45

在FPGA 上設計一個高性能、靈活的、面積小的通信體系結構是一項巨大的挑戰。大多數基于FPGA 的片上網絡都是運行在一個單一時鐘下。隨著FPGA 技術的發展,Xilinx 公司推出了Virtex-4

2019-08-21 06:47:43

本個學了51單片機,也有實際項目經驗,.不知道下一步應該怎么走,????想做點觸摸屏.應用.非開發觸摸屏.各位大師有沒有好的見意???謝謝。

2013-09-30 09:46:25

任務的特殊網絡 - 全局設置/重置。配置完成后,該線路被置低,以允許FPGA開始其新編程的功能。假設這是正確的,那么我理解。在我的VHDL中,如果我有一個簡單的頂級模型,其中一個進程對時鐘和復位信號很

2019-05-17 11:24:19

實現頂層設計是不可能的,因為我想生成一個時鐘來驅動FPGA邏輯和使用DCM的OPAD。以下是ERROR消息。錯誤:位置:1206- 此設計包含一個全局緩沖區實例,驅動網絡,驅動以下(前30個)非時鐘

2019-07-03 09:33:36

我寫這篇文章,是我在百度看到很多想接觸單片機或者已經接觸單片機的人,不知道怎么入門,或者不知道第一步怎么走。我也是把我的經驗寫出來,這次的只不過針對的是想接觸單片機的,剛接觸單片機的,一開始都會

2021-11-23 06:36:34

本人新手,使用的是購買的核心板,將FPGA引腳直接接帶寬100MHz的示波器,超過5MHz輸出就看起來不行了,本來想搞個100MHz的輸出當DAC芯片的時鐘的,利用pll搞出來的時鐘直接接引腳,走

2013-08-25 15:12:47

?還是必須接到全局時鐘管腳?我的理解是接到普通IO也可以,但這樣設置管腳我的FPGA程序會編譯出錯,不知什么原因?

2017-12-08 14:52:58

ad割銅命名,走線怎么走圓弧型

2019-09-04 22:53:39

像這種排針與單片機之間怎么走線啊?引腳都不是順序的像這種排針與單片機之間怎么走線啊?引腳都不是順序的

2019-09-05 02:08:03

原子哥:FSMC 被LCD 、NAND、 SRAM 復用,怎么走線,哪些線需要等長?

2019-03-07 04:06:11

HDMI差分對PCB怎么走線?要計算匹配阻抗嗎?差分對走多長有要求嗎?四對差分對要走一樣長嗎?

2019-05-31 05:35:21

一種FPGA時鐘網絡中鎖相環的實現方案:摘 要:本文闡述了用于FPGA 的可優化時鐘分配網絡功耗與面積的時鐘布線結構模型。并在時鐘分配網絡中引入數字延遲鎖相環減少時鐘偏差,探

2009-08-08 09:07:22 25

25 DLL在FPGA時鐘設計中的應用:在ISE集成開發環境中,用硬件描述語言對FPGA 的內部資源DLL等直接例化,實現其消除時鐘的相位偏差、倍頻和分頻的功能。時鐘電路是FPGA開發板設計中的

2009-11-01 15:10:30 33

33 FPGA重要設計思想及工程應用之時序及同

在FPGA設計中最好的時鐘方案 是: 由專用的全局時鐘輸入引腳 動單個 主時鐘去控制設計項目中的每一個觸發 器

2010-02-09 10:29:36 51

51 本文闡述了用于FPGA的可優化時鐘分配網絡功耗與面積的時鐘布線結構模型。并在時鐘分配網絡中引入數字延遲鎖相環減少時鐘偏差,探討了FPGA時鐘網絡中鎖相環的實現方案。

2010-08-06 16:08:45 12

12 FPGA的全局動態可重配置技術主要是指對運行中的FPGA器件的全部邏輯資源實現在系統的功能變換,從而實現硬件的時分復用。提出了一種基于System ACE的全局動態可重配置設計方法,

2011-01-04 17:06:01 54

54 FPGA全局時鐘資源一般使用全銅層工藝實現,并設計了專用時鐘緩沖與驅動結構,從而使全局時鐘到達芯片內部的所有可配置單元(CLB)、I/O單元(IOB)和選擇性塊RAM(Block Select RAM)的

2010-09-10 17:25:27 2175

2175 本文將探討FPGA時鐘分配控制方面的挑戰,協助開發團隊改變他們的設計方法,并針對正在考慮如何通過縮小其時鐘分配網絡的規模來擁有更多的FPGA I/O,或提高時鐘網絡性能的設計者們

2011-03-30 17:16:32 938

938

在FPGA設計中,為了成功地操作,可靠的時鐘是非常關鍵的。設計不良的時鐘在極限的溫度、電壓下將導致錯誤的行為。在設計PLD/FPGA時通常采用如下四種類型時鐘:全局時鐘、門控時鐘

2011-09-21 18:38:58 3472

3472

DLL在_FPGA時鐘設計中的應用,主要說明DLL的原理,在Xilinx FPGA中是怎么實現的。

2015-10-28 14:25:42 1

1 設計非常重要,認識FPGA的時鐘資源很有必要。 FPGA設計是分模塊的,每個模塊都有自己的時鐘域。FPGA有很多的對外外設接口,這些接口很多是源同步的設計,所以按照驅動能力和邏輯規模大體可以分為全局時鐘和局域時鐘。 全局時鐘,顧名思義就是FPGA內部驅動能力強,驅動

2017-02-08 05:33:31 561

561

任何一個邏輯單元,包括CLB、I/O引腳、內嵌RAM、硬核乘法器等,而且時延和抖動都很小。對FPGA設計而言,全局時鐘是最簡單最可預測的時鐘,最好的時鐘方案是:由專用的全局時鐘輸入引腳驅動單個全局時鐘,并用后者去控制設計中的每個觸發器。全局時鐘資源是專用布線資源

2017-02-09 08:43:41 1315

1315 目前,大型設計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發沿設計,對時鐘的周期、占空比、延時和抖動提出了更高的要求。為了滿足同步時序設計的要求,一般在FPGA設計中采用全局時鐘資源驅動設計的主時鐘,以達到最低的時鐘抖動和延遲。

2017-02-11 11:34:11 4223

4223 在Xilinx 的FPGA器件中,全局的復位/置位信號(Global Set/Reset (GSR))(可以通過全局復位管腳引入)是幾乎絕對可靠的,因為它是芯片內部的信號。

2017-02-11 11:46:19 876

876

在 Xilinx 系列 FPGA 產品中,全局時鐘網絡是一種全局布線資源,它可以保證時鐘信號到達各個目標邏輯單元的時延基本相同。其時鐘分配樹結構如圖1所示。 圖1.Xilinx FPGA全局時鐘分配

2017-11-22 07:09:36 8891

8891

目前,大型設計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發沿設計,對時鐘的周期、占空比、延時和抖動提出了更高的要求。為了滿足同步時序設計的要求,一般在FPGA設計中采用全局時鐘資源驅動設計的主時鐘,以達到最低的時鐘抖動和延遲。

2017-11-25 01:43:01 1411

1411 很大。 在設計PLD/FPGA時通常采用幾種時鐘類型。時鐘可分為如下四種類型:全局時鐘、門控時鐘、多級邏輯時鐘和波動式時鐘。多時鐘系統能夠包括上述四種時鐘類型的任意組合。

2017-11-25 09:16:01 3907

3907

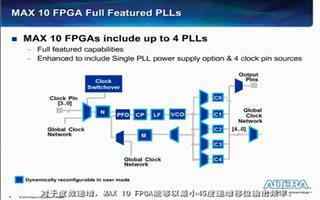

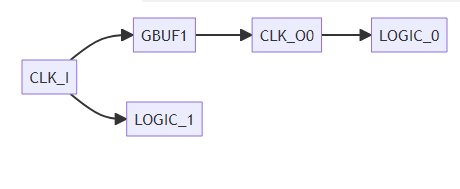

MAX 10 FPGA PLL和時鐘培訓,此次培訓涉及到器件系列的時鐘特性和選項。有20個全局時鐘網絡,全局CLK輸入引腳數量也可以加倍,用作通用IO引腳。并且采用動態用戶控制進行各種選擇和電源控制,構建魯棒的時鐘網絡源。它所有4個PLL都是全功能的。

2018-06-20 08:00:00 2325

2325

了解如何描述Spartan-6 FPGA中的全局和I / O時鐘網絡,描述時鐘緩沖器及其與I / O資源的關系,描述Spartan-6 FPGA中的DCM功能。

2018-11-22 06:10:00 4862

4862 時鐘是FPGA設計中最重要的信號,FPGA系統內大部分器件的動作都是在時鐘的上升沿或者下降沿進行。

2019-09-20 15:10:18 5065

5065

時鐘網絡反映了時鐘從時鐘引腳進入FPGA后在FPGA內部的傳播路徑。 報告時鐘網絡命令可以從以下位置運行: A,VivadoIDE中的Flow Navigator; B,Tcl命令

2020-11-29 09:41:00 2550

2550 時鐘篇 選用全局時鐘緩沖區(BUFG)作為時鐘輸入信號,BUFG是最穩定的時鐘輸入源,可以避免誤差。 只用一個時鐘沿來寄存數據,使用時鐘的兩個沿是不可靠的,如果時鐘沿“漂移”,就會導致時序錯誤

2020-12-11 10:26:44 1482

1482 組合邏輯生成的時鐘,在FPGA設計中應該避免,尤其是該時鐘扇出很大或者時鐘頻率較高,即便是該時鐘通過BUFG進入全局時鐘網絡。

2020-10-10 10:28:32 3639

3639

全局時鐘資源是一種專用互連網絡,它可以降低時鐘歪斜、占空比失真和功耗,提高抖動容限。Xilinx的全局時鐘資源設計了專用時鐘緩沖與驅動結構,從而使全局時鐘到達CLB、IOB和BRAM的延時最小。

2020-12-29 16:59:35 8

8 引言:本文我們介紹區域時鐘資源。區域時鐘網絡是獨立于全局時鐘的時鐘網絡。不像全局時鐘,一個區域時鐘信號(BUFR)的跨度被限制在一個時鐘區域,一個I/O時鐘信號驅動一個單一的Bank。這些網絡對于

2021-03-22 09:47:30 4631

4631

引言:本文我們介紹一下全局時鐘資源。全局時鐘是一個專用的互連網絡,專門設計用于到達FPGA中各種資源的所有時鐘輸入。這些網絡被設計成具有低偏移和低占空比失真、低功耗和改進的抖動容限。它們

2021-03-22 10:09:58 11527

11527

和前幾代FPGA差異,總結7系列FPGA中的時鐘連接。有關7系列FPGA時鐘資源使用的詳細信息,請關注后續文章。 時鐘資源架構概述 7系列FPGA與前一代FPGA時鐘資源差異 時鐘資源連接概述 1.時鐘資源架構概述 1.1 時鐘資源概述 7系列FPGA時鐘資源通過專用的全局和區域I/O和時鐘資源管

2021-03-22 10:25:27 4326

4326 對于一個設計項目來說,全局時鐘(或同步時鐘)是最簡單和最可預測的時鐘。只要可能就應盡量在設計項目中采用全局時鐘。FPGA都具有專門的全局時鐘引腳,它直接連到器件中的每一個寄存器。這種全局時鐘提供器件中最短的時鐘到輸出的延時。

2021-04-24 09:39:07 5827

5827

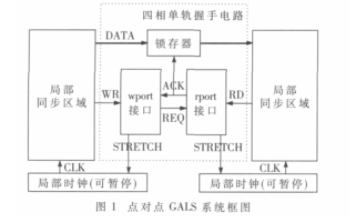

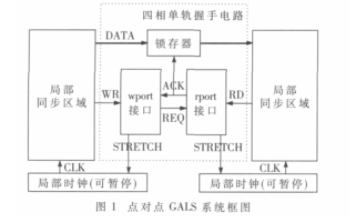

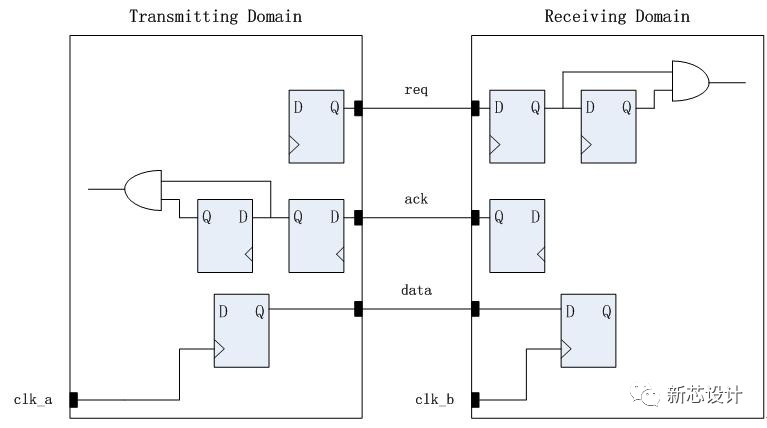

在常規FPGA中設計了基于LUT的異步狀態保持單元,實現了全局異步局部同步系統的接口電路、時鐘暫停電路,進一步完

2021-05-26 18:12:38 3436

3436

HROW:水平時鐘線,從水平方向貫穿每個時鐘區域的中心區域,將時鐘區域分成上下完全一致的兩部分。全局時鐘線進入每個時鐘區域的邏輯資源時,必須經過水平時鐘線。

2022-06-13 10:07:26 1481

1481 如果普通的GPIO怎么走全局時鐘網絡,其實很簡單,打開原主文檔,找到EFX_GBUFCE,該部分提供了verilog和VHDL的用法。

2023-04-06 11:44:26 467

467

什么是全局中斷?全局中斷使能位控制著“所有”中斷,它如果關閉的話會屏蔽其它中斷,有人經常關閉它,防止其它中斷帶來干擾,比如在使用GPIO模擬某個時序時,在GPIO傳輸數據過程中,如果被某個中斷干擾

2023-06-14 18:25:01 1619

1619 ??類似于電源域(電源規劃與時鐘規劃亦是對應的),假如設計中所有的 D 觸發器都使用一個全局網絡 GCLK ,比如 FPGA 的主時鐘輸入,那么我們說這個設計只有一個時鐘域。假如設計有兩個輸入時鐘,分別給不同的接口使用,那么我們說這個設計中有兩個時鐘域,不同的時鐘域,有著不同的時鐘頻率和時鐘相位。

2023-06-21 11:53:22 2002

2002

怎么根據外圍電路配置單片機gpio的時鐘? 根據外圍電路配置單片機GPIO的時鐘是一項重要的任務,它決定了單片機與外部設備的通信速度和穩定性。在本文中,我將詳細介紹如何根據外圍電路配置單片機GPIO

2024-01-31 10:57:10 365

365

電子發燒友App

電子發燒友App

評論