賽靈思在其FPGA中提供了豐富的時鐘資源,大多數設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。本文為您解惑......

2013-07-23 09:25:53 19707

19707

針對不同類型的器件,Xilinx公司提供的全局時鐘網絡在數量、性能等方面略有區別,下面以Virtex-4系列芯片為例,簡單介紹FPGA全局時鐘網絡結構。

2013-11-28 18:49:00 12149

12149

介紹3種跨時鐘域處理的方法,這3種方法可以說是FPGA界最常用也最實用的方法,這三種方法包含了單bit和多bit數據的跨時鐘域處理,學會這3招之后,對于FPGA相關的跨時鐘域數據處理便可以手到擒來。 本文介紹的3種方法跨時鐘域處理方法如下:

2020-11-21 11:13:01 3278

3278

引言:本文我們介紹一下全局時鐘資源。全局時鐘是一個專用的互連網絡,專門設計用于到達FPGA中各種資源的所有時鐘輸入。

2022-07-14 09:15:35 1538

1538 7系列FPGA擁有豐富的時鐘資源。各種緩沖器類型、時鐘輸入管腳和時鐘連接,可以滿足許多不同的應用需求。選擇合適的時鐘資源可以改善布線、性能和一般FPGA資源利用率。BUFGCTRL(最常用作BUFG

2022-07-22 09:40:25 2475

2475 引言:7系列FPGA具有多個時鐘路由資源,以支持各種時鐘方案和要求,包括高扇出、短傳播延遲和極低的偏移。

2022-07-22 09:46:39 682

682 7系列FPGA時鐘資源通過專用的全局和區域I/O和時鐘資源管理符合復雜和簡單的時鐘要求。時鐘管理塊(CMT)提供時鐘頻率合成、減少偏移和抖動過濾等功能。非時鐘資源,如本地布線,不推薦用于時鐘功能。

2022-07-28 09:07:34 1276

1276 EFX_GBUFCE既可以讓GPIO走全局時鐘網絡也可以用于為時鐘添加使能控制,當并不是隨時需要該時鐘時可以把時鐘禁止以節省功耗。

2023-05-12 09:53:38 562

562

“全局時鐘和第二全局時鐘資源”是FPGA同步設計的一個重要概念。合理利用該資源可以改善設計的綜合和實現效果;如果使用不當,不但會影響設計的工作頻率和穩定性等,甚至會導致設計的綜合、實現過程出錯

2023-07-24 11:07:04 655

655

通過上一篇文章“時鐘管理技術”,我們了解Xilinx 7系列FPGA主要有全局時鐘、區域時鐘、時鐘管理塊(CMT)。 通過以上時鐘資源的結合,Xilinx 7系列FPGA可實現高性能和可靠的時鐘分配

2023-08-31 10:44:31 1032

1032

FPGA的任意一個管腳都可以作為時鐘輸入端口,但是FPGA專門設計了全局時鐘,全局時鐘總線是一條專用總線,到達片內各部分觸發器的時間最短,所以用全局時鐘芯片工作最可靠,但是如果你設計的時候時鐘太多

2012-02-29 09:46:00

隨著FPGA設計越來越復雜,芯片內部的時鐘域也越來越多,使全局復位已不能夠適應FPGA設計的需求,更多的設計趨向于使用局部的復位。本節將會從FPGA內部復位“樹”的結構來分析復位的結構。我們的復位

2019-05-17 08:00:00

用于xilinx ML507的Xilinx頂點XC5VFX70TFFG1136 FPGA如何將xilinx LUT作為移位寄存器?什么是xilinx ML507的Xilinx頂點XC5VFX70TFFG1136 FPGA的CLB結構。這個FPGA上有哪些額外的原語?

2020-06-16 16:48:59

現了,將時鐘的布線成樹形結構,使得到達每一個邏輯單元的時鐘信號同相,這樣就可以實現同步,這就是全局時鐘網絡,GC_CLK。也就是說GC_CLK在FPGA內部是固定的位置,與其對應的引腳也就固定了,這樣

2019-07-09 08:00:00

FPGA的全局時鐘是什么?什么是第二全局時鐘?在FPGA的主配置模式中,CCLK信號是如何產生的?

2021-11-01 07:26:34

(30)FPGA原語設計(單端時鐘轉差分時鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設計(單端時鐘轉差分時鐘)5)結語1.2 FPGA簡介FPGA

2022-02-23 06:32:02

(29)FPGA原語設計(差分時鐘轉單端時鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設計(差分時鐘轉單端時鐘)5)結語1.2 FPGA簡介FPGA

2022-02-23 07:27:45

求FPGA內部資源{:soso_e100:}相關資料,發lishenghhuc@126.com,謝謝

2012-09-27 16:55:44

1.1 FPGA設計思想與技巧1.1.1 本節目錄1)本節目錄;2)本節引言;3)FPGA簡介;4)FPGA雙沿采樣之IDDR原語實現;5)結束語。1.1.2 本節引言“不積跬步,無以至千里;不積

2021-07-26 06:37:06

,這個時間差過大是很要命的。因此,FPGA器件內部設計了一些稱之為“全局時鐘網絡”的走線池。通過這種專用時鐘網絡走線,同一時鐘到達不同寄存器的時間差可以被控制到很小的范圍內。而我們又如何能保證輸入的時鐘

2019-04-12 01:15:50

,通過這些專用引腳輸入的時鐘信號,在FPGA內部可以很容易的連接到全局時鐘網絡上。所謂的全局時鐘網絡,是FPGA內部專門用于走一些有高扇出、低時延要求的信號,這樣的資源相對有限,但是非常實用。FPGA

2015-04-24 08:17:00

FPGA時鐘問題 2010-06-11 15:55:39分類: 嵌入式1.FPGA的全局時鐘是什么?FPGA的全局時鐘應該是從晶振分出來的,最原始的頻率。其他需要的各種頻率都是在這個基礎上利用PLL或者其他分頻手段得到的。

2021-07-29 09:25:57

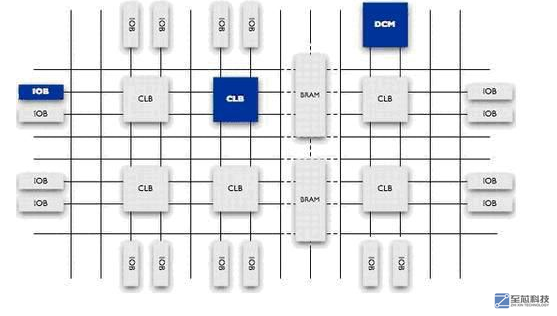

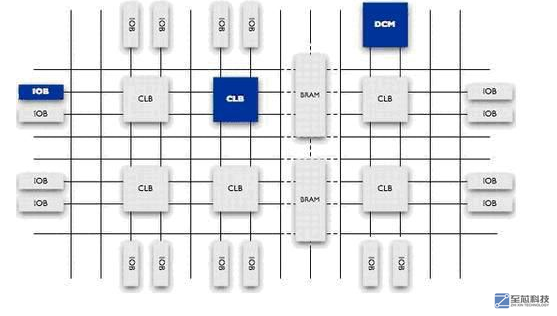

存儲結構。 4.豐富的布線資源 布線資源連通FPGA內部所有單元,連線的長度和工藝決定著信號在連線上的驅動能力和傳輸速度。布線資源的劃分: 1)全局性的專用布線資源:以完成器件內部的全局時鐘

2019-09-24 11:54:53

存儲結構。 4.豐富的布線資源 布線資源連通FPGA內部所有單元,連線的長度和工藝決定著信號在連線上的驅動能力和傳輸速度。布線資源的劃分: 1)全局性的專用布線資源:以完成器件內部的全局時鐘

2016-08-23 10:33:54

存儲結構。 4.豐富的布線資源 布線資源連通FPGA內部所有單元,連線的長度和工藝決定著信號在連線上的驅動能力和傳輸速度。布線資源的劃分: 1)全局性的專用布線資源:以完成器件內部的全局時鐘

2016-09-18 11:15:11

存儲結構。 4.豐富的布線資源 布線資源連通FPGA內部所有單元,連線的長度和工藝決定著信號在連線上的驅動能力和傳輸速度。布線資源的劃分: 1)全局性的專用布線資源:以完成器件內部的全局時鐘

2016-10-08 14:43:50

存儲結構。 4.豐富的布線資源 布線資源連通FPGA內部所有單元,連線的長度和工藝決定著信號在連線上的驅動能力和傳輸速度。布線資源的劃分: 1)全局性的專用布線資源:以完成器件內部的全局時鐘和全局

2016-07-16 15:32:39

MMCM 和 PLL在內部,FPGA本身被分成幾個時鐘區域,其中包含 CLB、BRAM、DSP、GT、I/O 和其他功能。每個區域還包含多個時鐘資源,包括支持以下內容的功能:12個全局時鐘2個跨區

2022-10-08 15:28:35

和 ODELAY 來消除信號之間的小延遲。抽頭之間的分辨率取決于FPGA的時鐘頻率和速度等級,7 系列 AC/DC 數據表如下所示:當我們提供 200 MHz 參考時鐘時,每個抽頭增量都會將延遲增加

2022-10-12 14:19:39

全局時鐘資源怎么使用?全局時鐘資源的例化方法有哪幾種?

2021-05-06 07:28:18

個數字時鐘管理模塊(DCM)。與全局時鐘資源相關的原語常用的與全局時鐘資源相關的Xilinx器件原語包括:IBUFG、IBUFGDS、BUFG、BUFGP、BUFGCE、BUFGMUX、BUFGDLL和DCM等。

2019-10-22 06:01:34

30-495]全局時鐘脊17由2個時鐘緩沖區共享。這可能會對QOR產生負面影響,因為這些時鐘的負載必須限制在特定的SLR上。以下緩沖區正在使用此主干:u_fpga

2018-10-24 15:27:38

延遲鎖相環(DLL)的數目不斷增加,最新的Virtex II器件最多可以提供16個全局時鐘輸入端口和8個數字時鐘管理模塊(DCM)。與全局時鐘資源相關的原語常用的與全局時鐘資源相關的Xilinx器件

2015-03-09 19:48:54

Gowin FPGA原語使用指南

2022-09-30 06:59:55

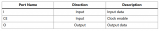

本文檔介紹了時鐘資源的功能、原語定義及使用方法。

2022-09-28 08:08:02

目前,大型設計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發沿設計,對時鐘的周期、占空比、延時和抖動提出了更高的要求。為了滿足同步時序設計的要求,一般在FPGA設計中采用全局時鐘資源驅動設計的主

2021-07-23 06:05:41

我看到別人寫的項目 程序中用了很多原語,比如輸入時鐘要設置一個IBUFG,有一些輸出信號接一個OBUFG,那么原語的好處是什么?如何知道什么時候要使用原語!

2017-07-13 19:59:37

有著豐富的布線資源,根據工藝、長度、寬度和分布位置的不同而劃分為4類不同的類別。第一類是全局布線資源,用于芯片內部全局時鐘和全局復位/置位的布線;第二類是長線資源,用以完成芯片Bank 間的高速信號

2012-03-08 11:03:49

把握DCM、PLL、PMCD和MMCM知識是穩健可靠的時鐘設計策略的基礎。賽靈思在其FPGA中提供了豐富的時鐘資源,大多數設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說

2020-04-25 07:00:00

引腳輸入的時鐘信號,在FPGA內部可以很容易的連接到全局時鐘網絡上。所謂的全局時鐘網絡,是FPGA內部專門用于走一些有高扇出、低時延要求的信號,這樣的資源相對有限,但是非常實用。FPGA的時鐘和復位

2016-08-08 17:31:40

= VC1/N:15;VC3源:VC2;VC3除法器:100。的VC3作為timer8時鐘;但為了使用UART模塊,我必須得到19200的波特率,我必須設置全局資源如下:SYSCLK:24mhz;VC3來源

2019-03-21 15:39:43

把握DCM、PLL、PMCD和MMCM知識是穩健可靠的時鐘設計策略的基礎。賽靈思在其FPGA中提供了豐富的時鐘資源,大多數設計人員在他們的FPGA設計中或多或少都會用到。不過對FPGA設計新手來說,什么時候用DCM、PLL、PMCD和MMCM四大類型中的哪一種,讓他們頗為困惑。

2019-09-18 08:26:21

大家好 我在設計中使用virtex -4 FPGA做了一個項目。從外部到我的FPGA只有單端時鐘。但是,連接到FPGA的AD需要幾個差分時鐘。如何實現這個功能? 據我所知,DCM原語確實提供了兩種

2019-01-21 08:52:16

資源只有這20個全局時鐘網絡,任何走全局線的信號都是用的這20個GCLKs中的某一個,不是只有全局時鐘才用全局時鐘資源。全局資源可以連接到chip中任意一個LE,相當于這個小區都是用的這個管道

2014-08-13 16:07:34

小弟最近在研究FPGA時鐘資源的手冊,遇到一個問題想請教各位大神。在Virtex6系列FPGA中,Bank分為top層和bottom層,請問我怎么查看一個Bank到底是在top層還是在bottom層

2015-02-10 10:30:25

DLL在FPGA時鐘設計中的應用:在ISE集成開發環境中,用硬件描述語言對FPGA 的內部資源DLL等直接例化,實現其消除時鐘的相位偏差、倍頻和分頻的功能。時鐘電路是FPGA開發板設計中的

2009-11-01 15:10:30 33

33 目前,大型設計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發沿設計,對時鐘的周期

2010-11-03 16:24:44 121

121 FPGA的全局動態可重配置技術主要是指對運行中的FPGA器件的全部邏輯資源實現在系統的功能變換,從而實現硬件的時分復用。提出了一種基于System ACE的全局動態可重配置設計方法,

2011-01-04 17:06:01 54

54 為了滿足同步時序設計的要求,一般在FPGA設計中采用全局時鐘資源驅動設計的主時鐘,以達到最低的時鐘抖動和延遲。 FPGA全局時鐘資源一般使用全銅層工藝實現,并設計了專用時

2011-01-04 11:26:35 1991

1991 在FPGA設計中,為了成功地操作,可靠的時鐘是非常關鍵的。設計不良的時鐘在極限的溫度、電壓下將導致錯誤的行為。在設計PLD/FPGA時通常采用如下四種類型時鐘:全局時鐘、門控時鐘

2011-09-21 18:38:58 3472

3472

電子專業單片機相關知識學習教材資料——FPGA片內資源設計指導

2016-08-23 15:55:35 0

0 如何正確使用FPGA的時鐘資源

2017-01-18 20:39:13 22

22 設計非常重要,認識FPGA的時鐘資源很有必要。 FPGA設計是分模塊的,每個模塊都有自己的時鐘域。FPGA有很多的對外外設接口,這些接口很多是源同步的設計,所以按照驅動能力和邏輯規模大體可以分為全局時鐘和局域時鐘。 全局時鐘,顧名思義就是FPGA內部驅動能力強,驅動

2017-02-08 05:33:31 561

561

時鐘設施提供了一系列的低電容、低抖動的互聯線,這些互聯線非常適合于傳輸高頻信號、最大量減小時鐘抖動。這些連線資源可以和DCM、PLL等實現連接。 每一種Spartan-6芯片提供16個高速、低抖動的全局時鐘資源用于優化性能。

2018-07-14 07:07:00 6504

6504

任何一個邏輯單元,包括CLB、I/O引腳、內嵌RAM、硬核乘法器等,而且時延和抖動都很小。對FPGA設計而言,全局時鐘是最簡單最可預測的時鐘,最好的時鐘方案是:由專用的全局時鐘輸入引腳驅動單個全局時鐘,并用后者去控制設計中的每個觸發器。全局時鐘資源是專用布線資源

2017-02-09 08:43:41 1315

1315 目前,大型設計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發沿設計,對時鐘的周期、占空比、延時和抖動提出了更高的要求。為了滿足同步時序設計的要求,一般在FPGA設計中采用全局時鐘資源驅動設計的主時鐘,以達到最低的時鐘抖動和延遲。

2017-02-11 11:34:11 4223

4223 在Xilinx 的FPGA器件中,全局的復位/置位信號(Global Set/Reset (GSR))(可以通過全局復位管腳引入)是幾乎絕對可靠的,因為它是芯片內部的信號。

2017-02-11 11:46:19 876

876

IBUFGDS輸入全局時鐘及DCM分頻使用

2017-02-11 16:16:11 4629

4629 xilinx原語使用方法

2017-10-19 08:50:39 15

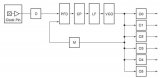

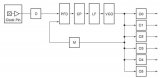

15 在 Xilinx 系列 FPGA 產品中,全局時鐘網絡是一種全局布線資源,它可以保證時鐘信號到達各個目標邏輯單元的時延基本相同。其時鐘分配樹結構如圖1所示。 圖1.Xilinx FPGA全局時鐘分配

2017-11-22 07:09:36 8891

8891

目前,大型設計一般推薦使用同步時序電路。同步時序電路基于時鐘觸發沿設計,對時鐘的周期、占空比、延時和抖動提出了更高的要求。為了滿足同步時序設計的要求,一般在FPGA設計中采用全局時鐘資源驅動設計的主時鐘,以達到最低的時鐘抖動和延遲。

2017-11-25 01:43:01 1411

1411 是全局布線資源,用于芯片內部全局時鐘和全局復位/置位的布線;第二類是長線資源,用以完成芯片Bank間的高速信號和第二全局時鐘信號的布線;第三類是短線資源,用于完成基本邏輯單元之間的邏輯互連和布線;第四類是分布式的布線資源,用于

2017-12-05 11:48:44 8

8 大家好,到了每日學習的時間了。今天我們來聊一聊FPGA的片內資源相關知識。 主流的FPGA仍是基于查找表技術的,已經遠遠超出了先前版本的基本性能,并且整合了常用功能(如RAM、DCM和DSP)的硬核

2018-05-25 14:11:47 8558

8558

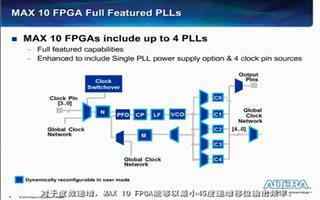

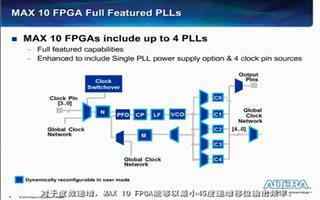

MAX 10 FPGA PLL和時鐘培訓,此次培訓涉及到器件系列的時鐘特性和選項。有20個全局時鐘網絡,全局CLK輸入引腳數量也可以加倍,用作通用IO引腳。并且采用動態用戶控制進行各種選擇和電源控制,構建魯棒的時鐘網絡源。它所有4個PLL都是全功能的。

2018-06-20 08:00:00 2325

2325

了解如何描述Spartan-6 FPGA中的全局和I / O時鐘網絡,描述時鐘緩沖器及其與I / O資源的關系,描述Spartan-6 FPGA中的DCM功能。

2018-11-22 06:10:00 4862

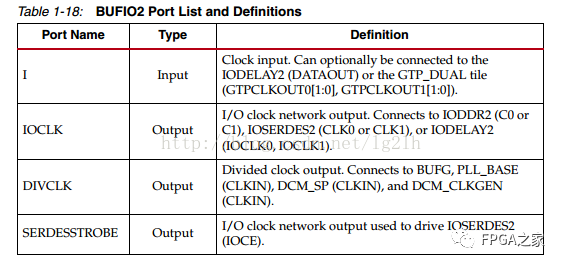

4862 項目中主要用到的原語與IO端口有關,所以基本在Input/Output Functions 和IO兩類中。下面著重介紹實際中所用到的幾個原語,芯片A7系列。

2019-01-06 11:23:11 15706

15706

在使用FPGA過程中,通常需要對資源做出評估,下面簡單談談如何評估FPGA的資源。

2019-02-15 15:09:05 3580

3580 本文檔的主要內容詳細介紹的是spartan-6 FPGA的時鐘資源的用戶指南資料免費下載。

2019-02-15 16:39:07 27

27 管腳是FPGA重要的資源之一,FPGA的管腳分別包括,電源管腳,普通I/O,配置管腳,時鐘專用輸入管腳GCLK等。

2019-06-28 14:34:07 3703

3703 時鐘篇 選用全局時鐘緩沖區(BUFG)作為時鐘輸入信號,BUFG是最穩定的時鐘輸入源,可以避免誤差。 只用一個時鐘沿來寄存數據,使用時鐘的兩個沿是不可靠的,如果時鐘沿“漂移”,就會導致時序錯誤

2020-12-11 10:26:44 1482

1482 區域(Region):每個FPGA器件被分為多個區域,不同的型號的器件區域數量不同。

FPGA時鐘資源主要有三大類:時鐘管理模、時鐘IO、時鐘布線資源。

時鐘管理模塊:不同廠家及型號的FPGA

2020-12-09 14:49:03 20

20 FPGA時鐘資源主要有三大類 時鐘管理模、時鐘 IO 、時鐘布線資源。

2020-12-09 18:14:00 13

13 本章介紹了高云半導體FPGA 產品的時鐘資源,包括專用的時鐘輸入、緩沖區和布線資源。時鐘的基礎設施提供了一系列低電容、低偏移互連線,非常適合承載高頻信號,最大限度地減少時鐘偏差和提高性能,可應用于所有的時鐘信號。

2020-12-10 14:20:13 9

9 本文檔的主要內容詳細介紹的是FPGA硬件基礎之理解FPGA時鐘資源的工程文件免費下載。

2020-12-10 14:20:11 6

6 本文檔的主要內容詳細介紹的是FPGA硬件基礎之FPGA時鐘資源的工程文件免費下載。

2020-12-10 15:00:29 15

15 全局時鐘資源是一種專用互連網絡,它可以降低時鐘歪斜、占空比失真和功耗,提高抖動容限。Xilinx的全局時鐘資源設計了專用時鐘緩沖與驅動結構,從而使全局時鐘到達CLB、IOB和BRAM的延時最小。

2020-12-29 16:59:35 8

8 DDR3。 2.FPGA架構設計問題 我們知道,FPGA片上分布著各種資源,如時鐘,serdes,RAM,LUT,IO等。在進行FPGA規劃時候,應當需要知道項目設計需求,以及需求各模塊之間的數據交織情況,這樣可以避免

2021-01-07 10:15:31 4645

4645

只能發生在FPGA的IOB上面,這里有特定的硬件結構可以實驗上面單沿變雙沿的方法,也就是使用原語進行一些列的操作。

2021-01-25 07:07:04 12

12 引言:本文我們介紹區域時鐘資源。區域時鐘網絡是獨立于全局時鐘的時鐘網絡。不像全局時鐘,一個區域時鐘信號(BUFR)的跨度被限制在一個時鐘區域,一個I/O時鐘信號驅動一個單一的Bank。這些網絡對于

2021-03-22 09:47:30 4631

4631

引言:本文我們介紹一下全局時鐘資源。全局時鐘是一個專用的互連網絡,專門設計用于到達FPGA中各種資源的所有時鐘輸入。這些網絡被設計成具有低偏移和低占空比失真、低功耗和改進的抖動容限。它們

2021-03-22 10:09:58 11527

11527

引言:7系列FPGA具有多個時鐘路由資源,以支持各種時鐘方案和要求,包括高扇出、短傳播延遲和極低的偏移。為了最好地利用時鐘路由資源,必須了解如何從PCB到FPGA獲取用戶時鐘,確定哪些時鐘路由資源

2021-03-22 10:16:18 4353

4353

和前幾代FPGA差異,總結7系列FPGA中的時鐘連接。有關7系列FPGA時鐘資源使用的詳細信息,請關注后續文章。 時鐘資源架構概述 7系列FPGA與前一代FPGA時鐘資源差異 時鐘資源連接概述 1.時鐘資源架構概述 1.1 時鐘資源概述 7系列FPGA時鐘資源通過專用的全局和區域I/O和時鐘資源管

2021-03-22 10:25:27 4326

4326 對于一個設計項目來說,全局時鐘(或同步時鐘)是最簡單和最可預測的時鐘。只要可能就應盡量在設計項目中采用全局時鐘。FPGA都具有專門的全局時鐘引腳,它直接連到器件中的每一個寄存器。這種全局時鐘提供器件中最短的時鐘到輸出的延時。

2021-04-24 09:39:07 5827

5827

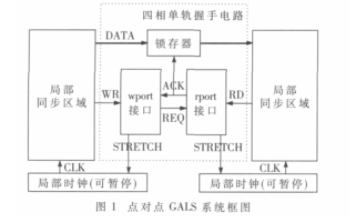

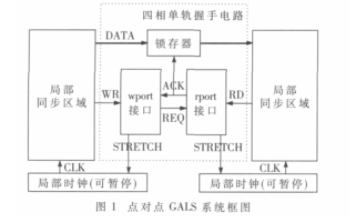

在常規FPGA中設計了基于LUT的異步狀態保持單元,實現了全局異步局部同步系統的接口電路、時鐘暫停電路,進一步完

2021-05-26 18:12:38 3436

3436

知識。 不正確的設計或次優的時鐘方案可能會導致在最好情況下較差的設計性能,或者在最壞情況下的隨機和難以查找的錯誤。FPGA時鐘資源指目標FPGA中大量與時鐘有關的不同資源,如時鐘類型(局部的和全局的)、頻率限制和不同時鐘管理

2021-06-17 16:34:51 1528

1528

(29)FPGA原語設計(差分時鐘轉單端時鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設計(差分時鐘轉單端時鐘)5)結語1.2 FPGA簡介FPGA

2021-12-29 19:41:38 5

5 (30)FPGA原語設計(單端時鐘轉差分時鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設計(單端時鐘轉差分時鐘)5)結語1.2 FPGA簡介FPGA

2021-12-29 19:41:48 10

10 HROW:水平時鐘線,從水平方向貫穿每個時鐘區域的中心區域,將時鐘區域分成上下完全一致的兩部分。全局時鐘線進入每個時鐘區域的邏輯資源時,必須經過水平時鐘線。

2022-06-13 10:07:26 1481

1481 電子發燒友網站提供《Logos系列FPGA時鐘資源(Clock)用戶指南.pdf》資料免費下載

2022-09-26 10:15:21 1

1 如果SoC設計規模小,在單個FPGA內可以容納,那么只要系統中的FPGA具有所SoC所設計需要時鐘的數量

2023-04-07 09:42:57 594

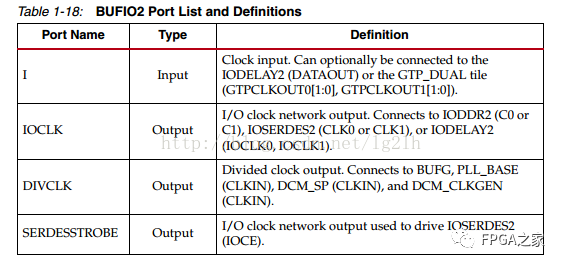

594 BUFIO是用來驅動I/O列內的專用時鐘網絡,這個專用的時鐘網絡獨立于全局時鐘資源,適合采集源同步數據。BUFIO只能由位于同一時鐘區域的Clock-Capable I/O驅動。一個時鐘區域

2023-05-11 16:16:36 1530

1530

如果SoC設計規模小,在單個FPGA內可以容納,那么只要系統中的FPGA具有所SoC所設計需要時鐘的數量

2023-05-23 15:46:24 481

481

如果FPGA沒有外部時鐘源輸入,可以通過調用STARTUP原語,來使用FPGA芯片內部的時鐘和復位信號,Spartan-6系列內部時鐘源是50MHz,Artix-7、Kintex-7等7系列FPGA是65MHz。

2023-10-27 11:26:56 973

973

把握DCM、PLL、PMCD和MMCM知識是穩健可靠的時鐘設計策略的基礎。賽靈思在其FPGA中提供了豐富的時鐘資源,大多數設計人員在他們的FPGA設計中或多或少都會用到。

2023-10-30 11:47:55 523

523

電子發燒友App

電子發燒友App

評論