時鐘網絡反映了時鐘從時鐘引腳進入FPGA后在FPGA內部的傳播路徑。

2019-09-10 15:12:31 6343

6343

跨時鐘域處理是FPGA設計中經常遇到的問題,而如何處理好跨時鐘域間的數據,可以說是每個FPGA初學者的必修課。如果是還是在校的學生,跨時鐘域處理也是面試中經常常被問到的一個問題。 在本篇文章中,主要

2020-11-21 11:13:01 3278

3278

01、如何決定FPGA中需要什么樣的時鐘速率 設計中最快的時鐘將確定 FPGA 必須能處理的時鐘速率。最快時鐘速率由設計中兩個觸發器之間一個信號的傳輸時間 P 來決定,如果 P 大于時鐘周期

2020-11-23 13:08:24 3565

3565

當我剛開始我的FPGA設計生涯時,我對明顯更小、更不靈活的 FPGA(想想 XC4000XL / Clcyone3/4和 Spartan)和工具的非常簡單的時鐘規則之一是盡可能只使用單個時鐘。當然,這并不總是可能的,但即便如此,時鐘的數量仍然有限。

2022-09-30 08:49:26 1326

1326 “全局時鐘和第二全局時鐘資源”是FPGA同步設計的一個重要概念。合理利用該資源可以改善設計的綜合和實現效果;如果使用不當,不但會影響設計的工作頻率和穩定性等,甚至會導致設計的綜合、實現過程出錯

2023-07-24 11:07:04 655

655

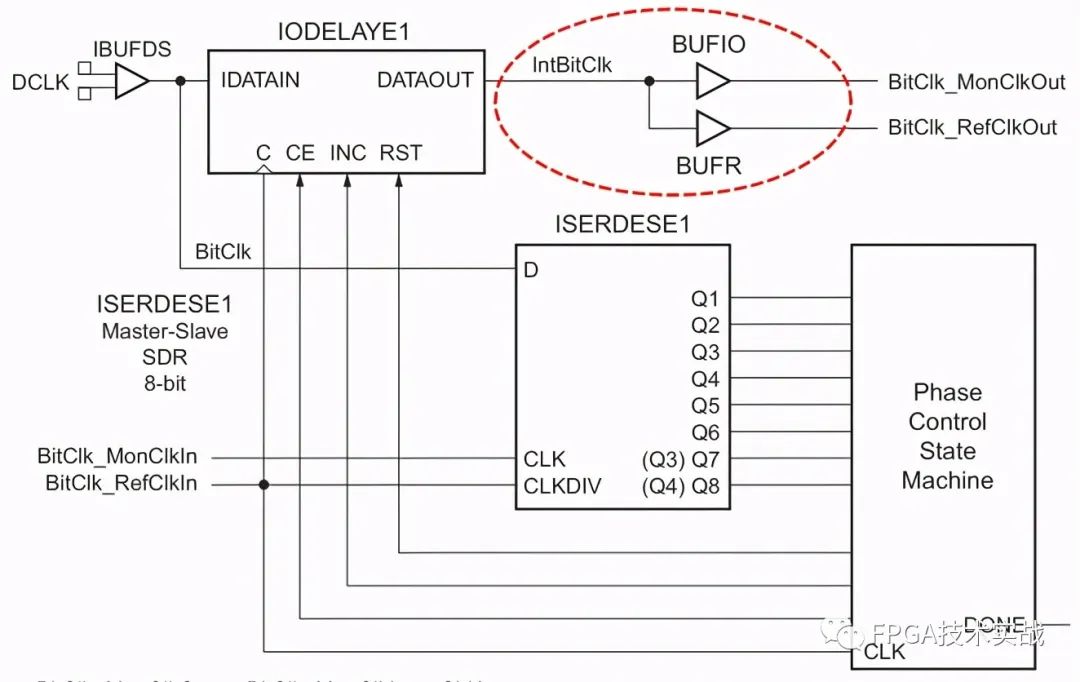

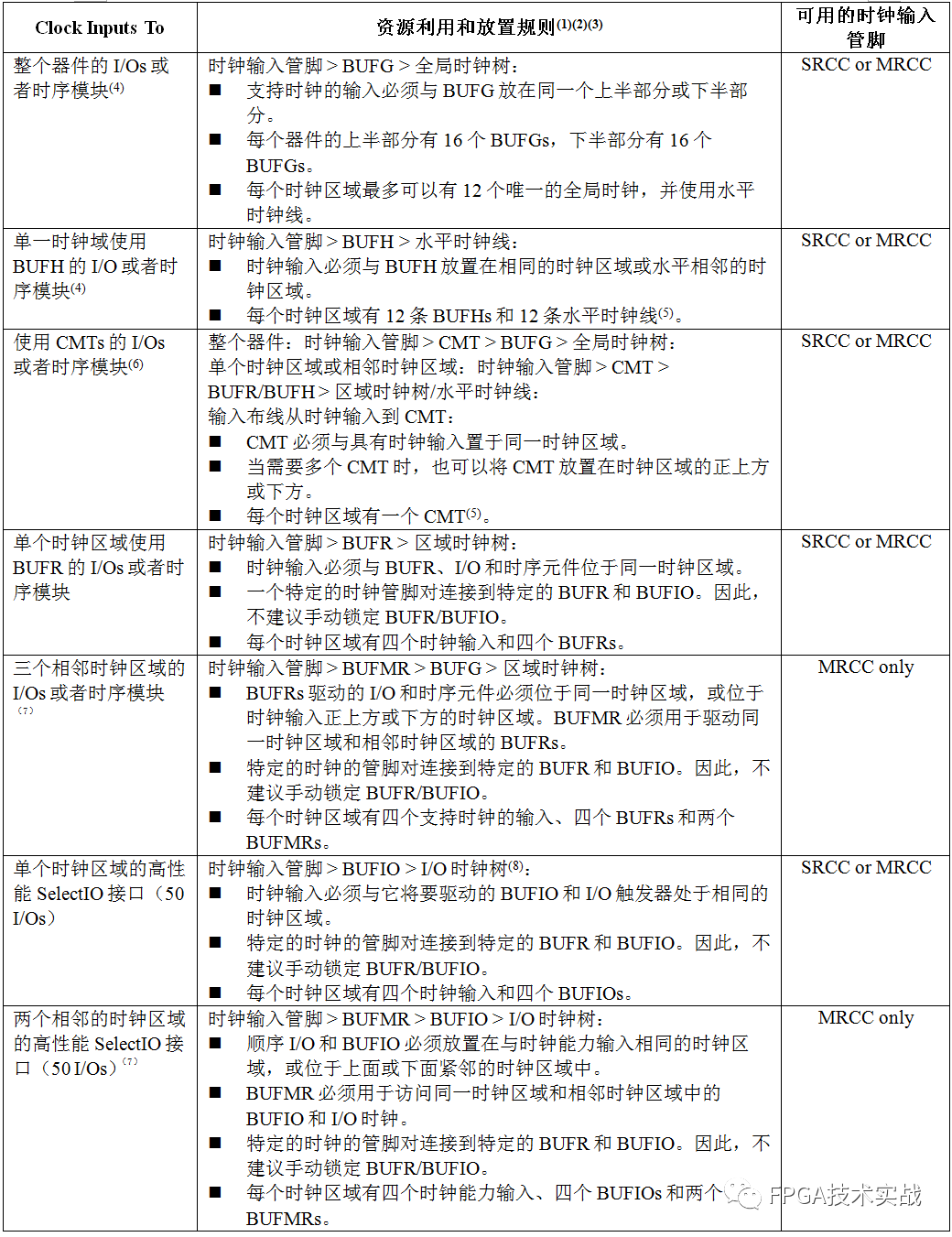

通過上一篇文章“時鐘管理技術”,我們了解Xilinx 7系列FPGA主要有全局時鐘、區域時鐘、時鐘管理塊(CMT)。 通過以上時鐘資源的結合,Xilinx 7系列FPGA可實現高性能和可靠的時鐘分配

2023-08-31 10:44:31 1032

1032

本文主要介紹Xilinx FPGA的GTx的參考時鐘。下面就從參考時鐘的模式、參考時鐘的選擇等方面進行介紹。

2023-09-15 09:14:26 1956

1956

生成時鐘包括自動生成時鐘(又稱為自動衍生時鐘)和用戶生成時鐘。自動生成時鐘通常由PLL或MMCM生成,也可以由具有分頻功能的時鐘緩沖器生成如7系列FPGA中的BUFR、UltraScale系列

2024-01-11 09:50:09 400

400

設計流程緊密集成,在項目的任何階段均可訪問。原理圖、PCB Layout 和FPGA 數據庫始終保持同步,以便用戶控制項目的設計數據流。另外,原理圖用戶可決定何時將 FPGA 數據(新數據或更新數據

2018-09-20 11:11:16

畢業后,從一個嵌入式硬件狗轉做FPGA工程師,從中兜兜轉轉繞了不少彎路,為了給后人避坑,所以今天開始寫有關FPGA從入門到精通的教程吧,這也算是給我國集成電路的發展做出微薄的貢獻吧。 本門課程主要

2020-06-23 23:52:00

①、②兩步加載時間可以忽略不計。圖2 基于CPLD 的FPGA 從并加載框之]數據寫入到CPLD 后,再通過接口④ ——CPLD 與FPGA 之間的從并接口,將數據加載到FPGA,從并接口是同步總線,加載

2019-07-12 07:00:09

本帖最后由 eehome 于 2013-1-5 10:04 編輯

FPGA與VHDL快速工程實踐從入門到提高

2012-08-14 13:14:37

本人菜鳥一枚,請問FPGA中(使用verilog)ChipScope顯示輸入時鐘信號(clk50M),報錯誤,如果通過pll獲取其他頻率比如clk40M,為什么ChipScope顯示的時鐘頻率一直為

2017-05-09 20:31:19

使用的時鐘信號往往不只是供給單個寄存器使用,因為在實際應用中,成百上千甚至更多的寄存器很可能共用一個時鐘源,那么從時鐘源到不同寄存器間的延時也可能存在較大偏差(我們通常稱為時鐘網絡延時),而我們知道

2019-04-12 01:15:50

1MHz 時鐘,總共多達40 個時鐘。本設計中最快時鐘是 34.368MHz E3 時鐘。FPGA 的最大時鐘速率的確定很重要,因為設計的差異將影響到該最大值。然而,在芯片商的資料手冊中常常可以看到“全局

2012-10-26 17:26:43

Tc2t;時鐘到達目的寄存器,即ADV7123芯片的引腳輸入端,其路徑延時為Tc2r,這個延時包括了時鐘從PLL輸出到FPGA引腳的延時以及時鐘從FPGA的引腳到ADV7123引腳的延時,后者的延時

2015-07-30 22:07:42

FPGA時鐘問題 2010-06-11 15:55:39分類: 嵌入式1.FPGA的全局時鐘是什么?FPGA的全局時鐘應該是從晶振分出來的,最原始的頻率。其他需要的各種頻率都是在這個基礎上利用PLL或者其他分頻手段得到的。

2021-07-29 09:25:57

我試圖弄清楚在應用程序映像損壞并且fpga從黃金映像啟動時fpga準備好之前需要多長時間。我測量了它,但它比應用程序+ 1x黃金映像啟動的3倍嘗試更長。我使用相同的時鐘頻率為黃金,因為用戶圖像是正確的?

2020-08-13 09:39:56

那個商業行為背后的動機,只是想以此為契機從技術的角度,略略討論下這次收購背后的關鍵因素——FPGA和ASIC的在AI計算中銜接關系。因為并不是專家,所以如有錯誤理解請指出。 從FPGA到ASIC

2023-03-28 11:14:04

請問各位大俠 用Altera公司的FPGA基于Quartus II和SOPC 和Nios II怎么在GPIO擴展口產生一個時鐘?非常感謝

2011-04-13 20:15:22

本來剛開始從原理圖畫起,到pcb都正常,但是在pcb中,我重新標注了幾次,原理圖也重新標注了,現在問題是,兩邊的元件對不上了,updata不起作用,反標也不行,該怎么做才能讓原理圖和pcb元件能對應上呢

2011-03-04 21:40:20

從ASIC到FPGA的轉換系統時鐘設計方案

2011-03-02 09:37:37

從MCU到FPGA

2021-02-02 07:36:46

包含.bit文件,而不包括VHDL源代碼。有沒有辦法獲得最簡單的源代碼,這將允許我從FPGA獲取數據流到PC上的COM端口。我只需要來自FPGA-> PC的3.2Kbps數據。

2019-09-11 12:18:49

嗨, 我正在開發一種設計,我們的主板有1個virtex5 fpga和9個從屬卡,每個都有1個V5 fpga。我想同步所有9個從卡的操作。我還希望主卡和從卡之間的數據傳輸速率為300-400Mbps

2019-01-30 06:52:36

在設計中想用上AD9254作為ADC,在設計過程中發現datasheet內部提供了多種時鐘設計方案,由于設計的限制,想要省去所有方案中均推薦使用的AD951x芯片,請問是否有曾經使用過該款AD的同仁,使用直接從FPGA差分時鐘引腳引出的時鐘信號,是否能夠滿足設計的要求?

2018-11-02 09:14:32

橋接器和一些簡單的UART VHDL代碼通過HyperTerm從FPGA到PC獲取數據?我在ML605上看到,Xilinx表示需要實現UART IP,例如XPS UART Lite或UART16550

2019-09-09 06:23:26

本帖最后由 lpc2292 于 2013-2-27 20:24 編輯

“部分 I: 用 Spartan-3 系列 FPGA 進行設計”第 1 章 “概述”第 2 章 “使用全局時鐘資源”第 3

2013-02-27 20:20:10

視頻信號(包括數據與時鐘,其中數據位寬16位,時鐘1位,最高工作頻率148.5MHZ).2.遇到的問題時鐘相對于數據的延時,也就是信號的建立與保持時間在經過FPGA后出現偏移。造成后端的DA不能正確的采集到數據。

2014-02-10 16:08:02

發燒友注冊,即可免費領取《PCB從設計到生產》系列全套課程+課件PPT資料。限額前100名用戶領取,名額有限,先到先得哦~【PCB系列課程部分截圖】我們會持續更新最新PCB分享資料,歡迎大家鼓勵支持,多

2019-09-19 16:59:55

必須適當地與所有數據位的到達保持同步。如果接收器使用發射時鐘,可能會要求延遲從發送端到接收端的時鐘信號。 有時設計可能需要一個更高的時鐘頻率來運行FPGA上的邏輯。但是,只有低頻率輸出的時鐘源可以用

2020-04-25 07:00:00

1、Audio codec時鐘源從BCLK1獲取 Platform: RK3399 OS: Android 7.1 Kernel: v4.4.83 需求: 默認codec的clock

2022-11-15 17:36:45

的問題是,我可以在FPGA內部使用這個時鐘作為FPGA和電路板的主時鐘嗎?我有一個應用程序,我想在板上盡可能少的部件,我不關心主時鐘頻率是什么,只要它是1-50MHz時鐘。要使用CCLK我必須有一個PCB

2019-05-07 13:40:54

,這意味著大部分設計不會受到時鐘的限制。對于區域時鐘,這些全局時鐘中的12個被局部化到該器件的四分之一區域。那么,FPGA設計師應該如何處理跨越用戶設計區域和IP模塊的公共全局時鐘呢?通常,客戶必須

2012-02-27 15:18:09

數字信號處理[3]已經成為FPGA的一個重要課題,高速的采樣頻率帶來的是大容量的存儲數據。在存儲芯片領域,DDR3以較低的功耗,較快的存儲速度,較高的存儲容量和較低的價格迅速占領市場;同時在繪制PCB板圖

2018-08-30 09:59:01

一部追蹤器,這又是怎么回事呢?由于目前安卓手機大都自帶GPS定位功能,很多移動廣告公司為了做到更精準的廣告投放,在軟件里就惡意插入獲取用戶位置信息的代碼。記者在暗訪一家名為“贏告無限”的廣告公司時,一位

2012-12-01 17:36:51

大家好,設備:xc7vx485tffg1761-2我需要從FPGA提供外部時鐘。所以我使用了OBUFDS,輸入時鐘來自clock_wizard。我想知道OBUFDS是否是正確的選擇,還是有任何提供輸出差分時鐘的方法。謝謝,Musthafa V.

2020-04-15 08:30:14

嗨,有誰知道如何從fpga(斯巴達3)中讀出用戶代碼?干杯約翰以上來自于谷歌翻譯以下為原文Hi, Anybody knows how to readout the usercode from within the fpga (spartan3)? cheers John

2019-07-26 10:53:31

嗨,我正在嘗試從FPGA向另一個設備輸出一個時鐘信號(10MHz)來驅動一個50歐姆的端接負載。我試著用DDR來輸出這個時鐘。我從主振蕩器時鐘輸入(50MHz)到virtex板生成此信號。我使用DCM以5來獲得10Mhz。然后我把它運行到DDR。到目前為止,我沒有運氣。有人可以給我指點嗎?謝謝。

2020-06-15 08:40:22

先生/女士, 我們如何從virtex 5(XC5VLX110T)獲取時鐘信號?我們已經參考了用戶手冊并嘗試從d手冊中提到的幾個引腳獲取信號。針腳:AH17,AG18。通過AH17引腳的輸出是17

2019-03-04 10:10:13

我知道在接入點模式下我們可以設置用戶和密碼,但我看到另一種方式(如我附上的圖表)ESP8266 可以從路由器獲取用戶和密碼,這怎么可能?

2023-05-16 08:49:35

“Drago,William @NARDAEAST”寫道:>全部,>>任何人都可以告訴我如何在VEE 6.xx中獲取用戶名(System.Environment.UserName

2019-08-29 11:03:45

定義存儲器的信號關系,并在PCB到FPGA的設計中傳遞這種關系。圖4 QDR存儲器讀取時序圖-MT54W1MH18J 從圖4可以看出在FPGA的管腳上,PCB傳播延遲與時鐘(CQ_FPGA)和數

2009-04-14 17:03:52

我想知道如何通過 wifi 從 C329 相機獲取圖像到用戶的屏幕,是直接 wifi 鏈接,還是通過互聯網?

IMAGE 命令要求是:“圖像文件應使用文件管理器上傳到設備”,因此不是動態的。

是否有

2023-05-10 09:44:29

我想在我的設計中使用kc705上的用戶可編程時鐘。我已閱讀有關Si570編程的用戶指南,但我想知道在調整時鐘后是否會對電路板進行編程會重置用戶可編程時鐘嗎?另外,我不確定如何從寄存器中提取的值。先謝謝你。

2020-03-27 10:36:03

我們正在使用St 分發源代碼,我們在buildroot工具中編譯源代碼。但是我們無法獲取用戶登錄頁面。我怎樣才能得到用戶登錄頁面。

2022-12-26 10:41:39

周期嗎?3.FPGA做加減法之類的運算時間要耗費多少時鐘周期?比如我定義輸入變量A、B、C、D都是8位,輸出變量E是16位,使E的前八位存入A+B,后八位存入C+D,那么從輸入到輸出需要多少個時鐘周期?謝謝!

2015-05-11 19:17:21

考慮的是在SDRAM端口的時鐘延時,也就是說還沒有考慮SDRAM時鐘從PLL輸出,經過FPGA內部走線,和外部PCB的延時,我們想一下,是不是有一個這樣的關系 就是,PLL的時鐘偏移 + 時鐘從PLL

2015-03-31 10:35:18

的值,由于我們的時鐘是總PLL發出的,時鐘從FPGA管腳輸出后再送給SDRAM,因此這個值一定是負值,而且也是時鐘在PCB上的走線延時,這個值我們估算為-0.1ns好了,因為真的沒法算我覺得。 然后

2015-03-31 10:20:00

具有DCO輸出,可將DAC輸入時鐘轉發至FPGA。我在想,這與ADC情況非常相似。但現在我意識到,對DCO信號的引用并沒有給我帶來任何好處。首先,DCO信號經歷從DAC到FPGA的傳播延遲,然后數據

2020-03-12 11:12:21

影響FPGA設計中時鐘因素的探討:時鐘是整個電路最重要、最特殊的信號,系統內大部分器件的動作都是在時鐘的跳變沿上進行, 這就要求時鐘信號時延差要非常小, 否則就可能造成時

2009-11-01 14:58:33 26

26 DLL在FPGA時鐘設計中的應用:在ISE集成開發環境中,用硬件描述語言對FPGA 的內部資源DLL等直接例化,實現其消除時鐘的相位偏差、倍頻和分頻的功能。時鐘電路是FPGA開發板設計中的

2009-11-01 15:10:30 33

33 本文闡述了用于FPGA的可優化時鐘分配網絡功耗與面積的時鐘布線結構模型。并在時鐘分配網絡中引入數字延遲鎖相環減少時鐘偏差,探討了FPGA時鐘網絡中鎖相環的實現方案。

2010-08-06 16:08:45 12

12 提出了一種基于FPGA的時鐘跟蹤環路的設計方案,該方案簡化了時鐘跟蹤環路的結構,降低了時鐘調整電路的復雜度。實際電路測試結果表明,該方案能夠使接收機時鐘快速準確地跟蹤發

2010-11-19 14:46:54 31

31 Printf:讀取用戶輸入

前面的程序很好,但要是如果能從用戶那里讀入值5和7而不是使用固定的值的話,那就更好了。可以改為下面的程序: #include

2009-07-29 10:42:21 1771

1771 PCB板完整電磁信息的獲取及應用

調試PCB的傳統工具包括:時域的示波器

2009-12-26 14:44:40 560

560 大型設計中FPGA的多時鐘設計策略

利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率

2009-12-27 13:28:04 645

645

在FPGA設計中,為了成功地操作,可靠的時鐘是非常關鍵的。設計不良的時鐘在極限的溫度、電壓下將導致錯誤的行為。在設計PLD/FPGA時通常采用如下四種類型時鐘:全局時鐘、門控時鐘

2011-09-21 18:38:58 3472

3472

在Quartus Ⅱ開發環境下,用Verilog HDL硬件描述語言設計了一個可以在FPGA芯片上實現的數字時鐘. 通過將設計代碼下載到FPGA的開發平臺Altera DE2開發板上進行了功能驗證. 由于數字時鐘的通用

2011-11-29 16:51:43 178

178 FPGA 異步時鐘設計中如何避免亞穩態的產生是一個必須考慮的問題。本文介紹了FPGA 異步時鐘設計中容易產生的亞穩態現象及其可能造成的危害,同時根據實踐經驗給出了解決這些問題的

2011-12-20 17:08:35 63

63 利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數、異步時鐘設計和時鐘/數

2012-05-21 11:26:10 1100

1100

DLL在_FPGA時鐘設計中的應用,主要說明DLL的原理,在Xilinx FPGA中是怎么實現的。

2015-10-28 14:25:42 1

1 基于FPGA的數字時鐘設計,可實現鬧鐘的功能,可校時。

2016-06-23 17:15:59 64

64 如何正確使用FPGA的時鐘資源

2017-01-18 20:39:13 22

22 Cadence OrCADFPGA System Planner為FPGA和PCB之間的協同設計提供了一種全面的、可擴展的解決方案,它能使用戶創建一個正確的、最優的引腳分配。FPGA的引腳分配是根據

2017-11-17 20:36:09 5453

5453

本文檔的主要內容詳細介紹的是spartan-6 FPGA的時鐘資源的用戶指南資料免費下載。

2019-02-15 16:39:07 27

27 跨時鐘域問題(CDC,Clock Domain Crossing )是多時鐘設計中的常見現象。在FPGA領域,互動的異步時鐘域的數量急劇增加。通常不止數百個,而是超過一千個時鐘域。

2019-08-19 14:52:58 2854

2854 時鐘是FPGA設計中最重要的信號,FPGA系統內大部分器件的動作都是在時鐘的上升沿或者下降沿進行。

2019-09-20 15:10:18 5065

5065

時鐘網絡反映了時鐘從時鐘引腳進入FPGA后在FPGA內部的傳播路徑。 報告時鐘網絡命令可以從以下位置運行: A,VivadoIDE中的Flow Navigator; B,Tcl命令

2020-11-29 09:41:00 2550

2550 對于 FPGA 來說,要盡可能避免異步設計,盡可能采用同步設計。 同步設計的第一個關鍵,也是關鍵中的關鍵,就是時鐘樹。 一個糟糕的時鐘樹,對 FPGA 設計來說,是一場無法彌補的災難,是一個沒有打好地基的樓,崩潰是必然的。

2020-11-11 09:45:54 3656

3656 區域(Region):每個FPGA器件被分為多個區域,不同的型號的器件區域數量不同。

FPGA時鐘資源主要有三大類:時鐘管理模、時鐘IO、時鐘布線資源。

時鐘管理模塊:不同廠家及型號的FPGA

2020-12-09 14:49:03 20

20 FPGA時鐘資源主要有三大類 時鐘管理模、時鐘 IO 、時鐘布線資源。

2020-12-09 18:14:00 13

13 本文檔的主要內容詳細介紹的是FPGA硬件基礎之FPGA時鐘資源的工程文件免費下載。

2020-12-10 15:00:29 15

15 前些時候,共享充電寶漲價問題引起了消費者熱議,現在,新的問題又來了。根據有關媒體的消息,共享充電寶存在著一個安全隱患問題,那就是竊取用戶的個人隱私。

2020-12-15 15:33:09 3615

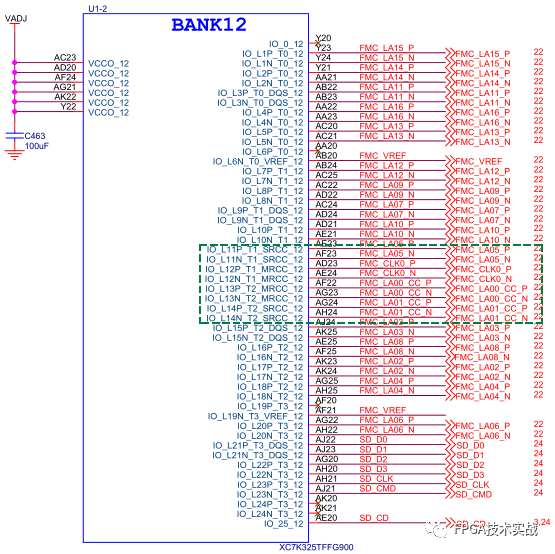

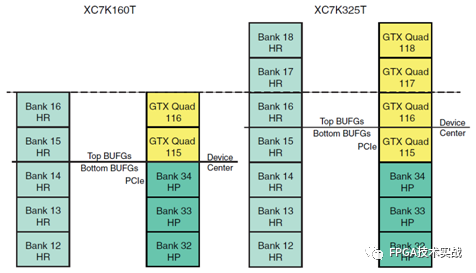

3615 引言:7系列FPGA具有多個時鐘路由資源,以支持各種時鐘方案和要求,包括高扇出、短傳播延遲和極低的偏移。為了最好地利用時鐘路由資源,必須了解如何從PCB到FPGA獲取用戶時鐘,確定哪些時鐘路由資源

2021-03-22 10:16:18 4353

4353

引言:從本文開始,我們陸續介紹Xilinx 7系列FPGA的時鐘資源架構,熟練掌握時鐘資源對于FPGA硬件設計工程師及軟件設計工程師都非常重要。本章概述7系列FPGA時鐘,比較了7系列FPGA時鐘

2021-03-22 10:25:27 4326

4326 (10)FPGA跨時鐘域處理1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA跨時鐘域處理5)結語1.2 FPGA簡介FPGA(Field Programmable

2021-12-29 19:40:35 7

7 (08)FPGA時鐘概念1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA時鐘概念5)結語1.2 FPGA簡介FPGA(Field Programmable Gate

2021-12-29 19:41:17 2

2 (12)FPGA時鐘設計原則1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA時鐘設計原則5)結語1.2 FPGA簡介FPGA(Field Programmable

2021-12-29 19:41:27 17

17 (29)FPGA原語設計(差分時鐘轉單端時鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設計(差分時鐘轉單端時鐘)5)結語1.2 FPGA簡介FPGA

2021-12-29 19:41:38 5

5 (30)FPGA原語設計(單端時鐘轉差分時鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設計(單端時鐘轉差分時鐘)5)結語1.2 FPGA簡介FPGA

2021-12-29 19:41:48 10

10 ?xilinx 的 FPGA 時鐘結構,7 系列 FPGA 的時鐘結構和前面幾個系列的時鐘結構有了很大的區別,7系列的時鐘結構如下圖所示。

2022-07-03 17:13:48 2592

2592 電子發燒友網站提供《Logos系列FPGA時鐘資源(Clock)用戶指南.pdf》資料免費下載

2022-09-26 10:15:21 1

1 ASIC 和FPGA芯片的內核之間最大的不同莫過于時鐘結構。ASIC設計需要采用諸如時鐘樹綜合、時鐘延遲匹配等方式對整個時鐘結構進行處理,但是 FPGA設計則完全不必。

2022-11-23 16:50:49 686

686

跨時鐘域是FPGA設計中最容易出錯的設計模塊,而且一旦跨時鐘域出現問題,定位排查會非常困難,因為跨時鐘域問題一般是偶現的,而且除非是構造特殊用例一般的仿真是發現不了這類問題的。

2023-05-25 15:06:00 1150

1150

FPGA多bit跨時鐘域適合將計數器信號轉換為格雷碼。

2023-05-25 15:21:31 1953

1953

之前在玩FPGA時,對于一個系統工程,當邏輯電路設計完成之后,一般會先拿給Vivado/Quartus先去跑一般綜合,然后去獲取所有的跨時鐘路徑,在ASIC里,基本也是拿EDA工具去分析獲取。今兒個搞個小demo,看在SpinalHDL當設計做完后,如何一鍵提取整個工程里所有的跨時鐘路徑。

2023-09-15 14:06:56 356

356 fpga跨時鐘域通信時,慢時鐘如何讀取快時鐘發送過來的數據? 在FPGA設計中,通常需要跨時鐘域進行數據通信。跨時鐘域通信就是在不同的時鐘域之間傳輸數據。 當從一個時鐘域傳輸數據到另一個時鐘

2023-10-18 15:23:51 578

578 FPGA為什么有時候還需要一個時鐘配置芯片提供時鐘呢? FPGA(Field Programmable Gate Array)是一種可編程邏輯器件,可以根據不同需要編程,實現不同的功能。在FPGA

2023-10-25 15:14:20 1045

1045 在編程中,我們經常需要獲取用戶在界面上的輸入值,其中一個常見的控件是QLineEdit。QLineEdit是Qt框架中的一個文本輸入框,允許用戶輸入文本信息。 要獲取QLineEdit中的輸入

2023-11-30 16:13:41 733

733

電子發燒友App

電子發燒友App

評論