Ian Beavers

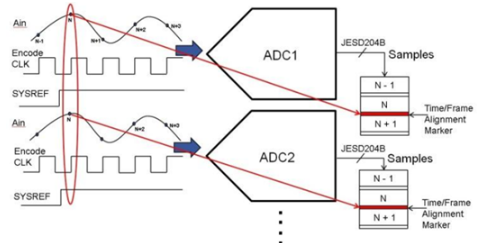

對于需要一系列同步模數轉換器(ADC)的高速信號采樣和處理應用,校正和匹配轉換器之間的延遲變化的能力至關重要。圍繞此功能的系統設計至關重要,因為從模擬采樣點到處理模塊的任何延遲不匹配都會降低性能。交錯處理也需要樣本對齊,其中一個轉換器樣本領先另一個轉換器樣本幾分之一時鐘周期。

JESD204B第三代高速串行轉換器接口的主要特性之一是能夠為系統中的每個轉換器建立確定性延遲。正確理解和使用此功能后,它可以在單個系統中的多個ADC之間創建同步或交錯采樣系統。

由于確定性延遲是一種相對較新的轉換器接口特性,系統設計人員通常會對如何建立它、感興趣的信號以及如何實現同步或交錯處理有幾個問題。以下是設計具有確定性延遲的系統的一些常見問題和答案,該系統與FPGA一起采樣的多個JESD204B轉換器。

什么是確定性延遲,JESD204B如何定義它?

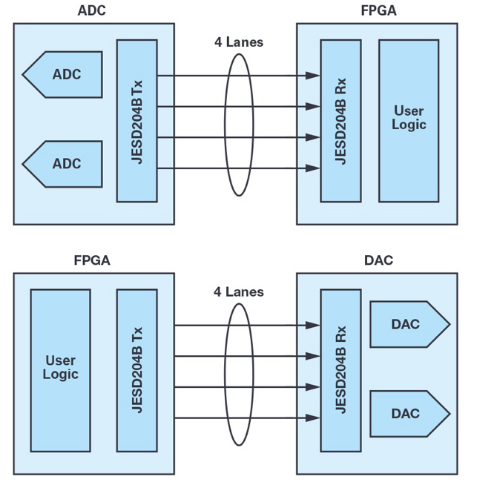

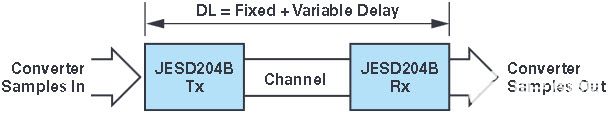

JESD204B鏈路上的確定性延遲由串行數據從發射器(ADC或源FPGA)的并行成幀數據輸入傳播到接收器(數模轉換器或DAC或接收器FPGA)的并行成幀數據輸出所需的時間來定義。這個時間通常是 以分辨率的幀時鐘周期或設備時鐘測量。

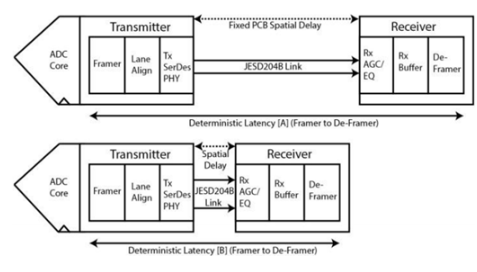

JESD204B的確定性延遲規范未考慮ADC的模擬前端內核或DAC的后端模擬內核。它僅基于進出JESD204B數字成幀的數據。在此延遲計算中,不僅兩個有源設備是一個函數,而且連接兩者的空間信號路由也是如此。這意味著在多轉換器系統中,每個鏈路的確定性延遲可能更大或更小,具體取決于JESD204B通道路由的空間長度及其各自的延遲。接收器上的緩沖延遲有助于解決路由引起的延遲差異(圖 1)。

圖1.JESD204B在兩個器件之間的確定性延遲將基于三個分量:從發射器成幀器到輸出的延遲、空間路由延遲以及從輸入到解碼器的接收器延遲。來自同一系統中兩個不同ADC的數據可能各自具有自己獨特的確定性延遲。

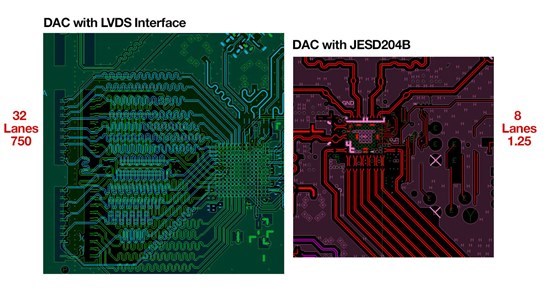

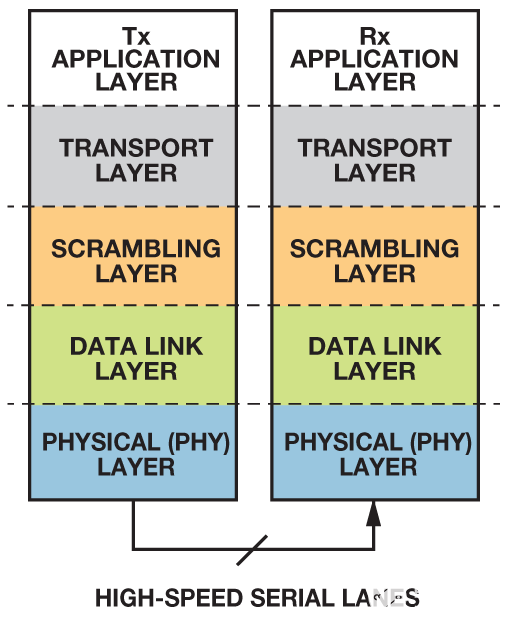

與低壓差分信號(LVDS)等簡單的串行鏈路配置不同,JESD204B接口將數據樣本打包到定義的幀中。在來自發射器的鏈路握手或初始通道對齊序列 (ILAS) 期間,一對或幾個樣本的每個幀邊界由一個特殊的控制字符標記。在 ILAS 期間,一個較大的已定義幀組(稱為多幀)也用相應的控制字符進行標記。但是,在此序列完成后,不需要控制字符,并且可以獲取鏈路的全部帶寬。幀和多幀邊界分別與幀時鐘和多幀時鐘重合。

JESD204子類與確定性延遲的關系是什么意思?

JESD204B協議有三個子類來定義鏈路的確定性延遲。子類 0 向后兼容 JESD204 和 JESD204A,不支持確定性延遲。子類 1 通過使用稱為 SYSREF 的系統參考信號來支持確定性延遲。子類 2 通過雙重用途使用 ~SYNC 信號來支持確定性延遲,這也允許接收器啟動握手 ILAS 例程。相對于時鐘在時間上準確放置 SYSREF 與 ~SYNC 的能力將決定感興趣的系統需要哪個子類。

如何使用確定性延遲來調整多個轉換器之間的采樣?

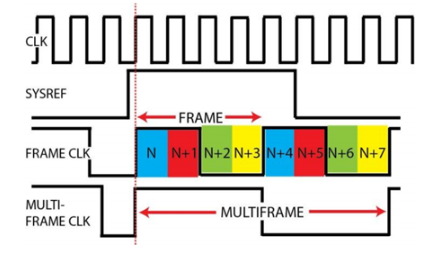

對于子類1轉換器實現,幀時鐘和多幀時鐘在每個器件上通過系統參考邊沿SYSREF的出現而內部對齊。當檢測到 SYSREF 邊沿時,這兩個時鐘都與該時間點對齊。由于這些時鐘保留在每個設備內部,因此它們在發射器內的邊界通過使用控制字符通過串行鏈路進行通信。

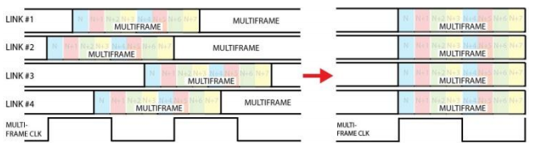

每個接收器都可以隱式解碼發射器幀和多幀時鐘相對于其自己的同名時鐘以及相對于所有發射設備的時間位置。這使得接收器能夠使用緩沖延遲在相對較早的數據到達時對樣本進行糾偏,以將鏈路與最新到達的數據相匹配(圖 2)。

圖2.在JESD204B發送器中,時鐘鎖存系統參考(SYSREF)邊沿后,樣本與幀和多幀時鐘對齊。出于視覺目的,此處將多幀定義為僅包含八個樣本。

對于同步采樣,這些數據鏈路可以在FPGA內及時對齊。對于交錯采樣,每個鏈路都可以通過其相應的相對相位延遲來抵消。通過測量從接收器的多幀時鐘邊沿到每個鏈路的多幀控制特性的時間延遲,可以識別每個鏈路的確定性延遲。需要注意的是,每個鏈路的確定性延遲必須短于多幀時鐘周期的持續時間(圖 3)。

圖3.來自四個JESD204B發送器的多幀樣本通過使用緩沖延遲與接收器內的多幀時鐘對齊。

確定性延遲是否與轉換器總延遲相同?

ADC的總延遲是模擬采樣從器件進行計時、處理和數字輸出所需的時間。類似地,DAC的總延遲是從數字采樣數據時鐘輸入器件到相應采樣從模擬輸出時鐘出來的時間。通常,它們都是在分辨率的采樣時鐘周期中測量的,因為它們與頻率有關。它部分取決于單個轉換器組件中的模擬處理架構。從根本上說,這與JESD204B鏈路實現所描述的確定性延遲的定義不同,后者是三個組件的函數。

對齊多個轉換器的最大糾偏預算是多少?

在ILAS過程中,發射器發送多幀控制字符以標記多幀時鐘邊界。接收器識別這些字符以創建自己的內部本地多幀時鐘,該時鐘與上游鏈路中的每個發射器對齊。對于使用多個接收器的大型陣列系統,多幀時鐘也在所有這些器件上對齊。因此,任何轉換器鏈路的確定性延遲都不能超過單個多幀時鐘周期的時間。這是跨鏈接的總糾偏時間預算。

多幀時鐘的持續時間通常為數十個采樣時鐘周期。甚至可以通過在鏈路握手期間傳達的設置參數變量將其調整為更長或更短。

此功能是否與ADC或DAC上的同一模擬采樣點正確對齊,還是需要更多?

確定性延遲提供了一種根據提供給JESD204B成幀器的相同時間點對齊樣本的方法。除了這段時間之外,ADC在JESD204B成幀器之前處理前端的模擬樣本所需的時鐘周期更多。轉換器供應商必須在時鐘持續時間上提前成幀器指定此時間段。相反,DAC在解幀器之后需要額外的時鐘周期,以模擬形式將樣本處理到輸出。

在獲得有效的模擬樣品數據之前,對準過程需要多長時間?

發送到轉換器和FPGA的SYSREF邊沿會導致對齊過程開始。在此事件之后,除了ILAS序列外,還需要完成幾個多幀時鐘周期,然后才能獲得有效的樣本數據。這相當于許多采樣時鐘周期的相對時間。具體持續時間可能取決于轉換器中JESD204B內核的獨特確定性延遲,該值需要由供應商傳達。在此期間,鏈接將被關閉,有效數據將不會傳輸。在絕對時間內,持續時間將是采樣時鐘頻率的函數。

實現同步采樣最具挑戰性的系統設計方面是什么?

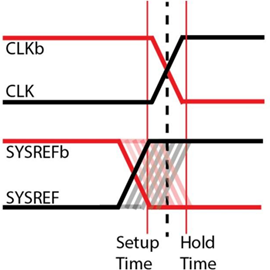

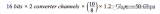

在子類 1 中實現同步或交錯處理直至采樣電平的最具挑戰性的方面之一是能夠在多個轉換器之間及時對齊 SYSREF 的使能邊沿。此外,每個SYSREF邊沿都需要滿足設置要求,并將時間保持到各自的采樣時鐘。這將消耗一些可用的時序裕量。主動和獨立地偏斜SYSREF和時鐘之間的精細相位的能力將有助于實現轉換器之間的時序收斂。

SYSREF 是否需要是單個事件,還是可以重復發生?關于每個案例,我需要了解什么?

SYSREF 對準邊沿可以是單脈沖、周期性、間隙周期性或重復非周期性。這將取決于系統的需求以及時鐘和源頭SYSREF之間相位偏差的時序靈活性。對于 SYSREF 的重復情況,幀和多幀 時鐘將在每個事件上重新對齊。但是,由于目標是保持一組對齊的時鐘,因此周期周期性 SYSREF 的使能沿應落在多幀時鐘邊界上。由于時鐘應該已經在第一個 SYSREF 邊沿之后對齊,這將防止不必要的重新對齊。

周期性SYSREF信號的不利影響之一是它有可能耦合到目標模擬信號上。這就是為什么并不總是建議使用周期性信號,并且只應在絕對必要時使用。如果使用周期性SYSREF,則必須注意將其與ADC的模擬前端正確隔離。

有哪些方法可以將 SYSREF 偏斜調整為在單個時鐘周期內?

理想情況下,每個轉換器和FPGA的SYSREF和時鐘可以精確布線,時序裕量可滿足所有組件的嚴格設置和保持時間。但是,隨著高性能轉換器采樣速度的不斷提高,僅靠精確的印刷電路板(PCB)布線并不總是能滿足時序收斂。器件之間的引腳間差異,加上電源和溫度漂移,會在一系列高速轉換器上產生相對較大的時序偏差。可能需要高級時序調整功能來提供有源 SYSREF 相位偏斜。

例如,來自ADC的信息性警報可以識別SYSREF邊沿是否在設置內鎖定,并保持時序窗口。如果發生這種情況,則時鐘邊沿用于時序參考、時鐘[N]或時鐘[N+1]將存在歧義。根據檢測到 SYSREF 邊沿的位置,采樣 CLK 邊沿相對于 SYSREF 的相位可能會在時鐘源處延遲,以保持滿足建立和保持時間的有效時序條件。

另一種選擇是使用采樣時鐘的下一個下降沿而不是上升沿來獲得半個相位裕量周期。系統中的每個轉換器都可以通過這種方式進行調諧,前提是時鐘源對各自的 SYSREF 和 CLK 具有獨立的相位調整(圖 4)。

圖4.為了在高速下實現低至樣品電平的對齊,滿足SYSREF相對于輸入時鐘的建立和保持時間可能具有挑戰性。能夠在相位早期偏斜每個SYSREF輸入,以防止相對于其CLK的設置時間違規,有助于滿足系統中多個轉換器之間的時序收斂要求。

是否需要支持子類 1 或子類 2 的轉換器才能使用確定性延遲功能?

子類1和子類2是唯一支持確定性延遲的子類,如JESD204B規范中所述。在子類 1 中,SYSREF 信號定義了確定性延遲。在子類 2 中,~SYNC 是定義此延遲的信號。一些轉換器供應商創建了一個子類 0 實現,用于支持對齊樣本的同步方案。在這種情況下,不使用轉換器和FPGA之間多幀時鐘的對齊過程

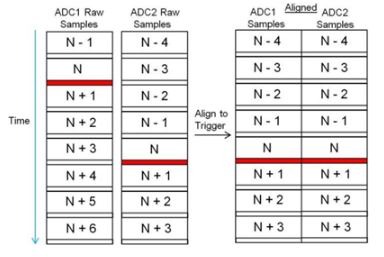

樣本級別的時間戳機制可用于使用附加的輔助信息(稱為控制位)來標記 SYSREF 的發生。與 SYSREF 邊沿重合的每個樣本都標有唯一的控制位。在 FPGA 中, 具有此時間戳的每個鏈路都可以延遲到等于最長路徑,然后彼此對齊,與轉換器之間的延遲差異無關(圖 5 和圖 6)。

圖5.通過使用SYSREF控制位時間戳,可以在FGPA處理模塊內實現子類0中的采樣對齊,而不管從模擬輸入到JESD204B輸出的多個ADC之間是否存在任何實際延遲差異。

圖6.通過使用附加的控制位作為與前端模擬輸入重合的觸發(紅色),FPGA可以對齊來自不同延遲的信號鏈的樣本。

總結

雖然確定性延遲是JESD204B的一個有點復雜的選項,但如果使用得當,它可以成為高性能信號處理系統設計的強大功能。來自ADC陣列的樣本可以通過緩沖延遲在FPGA內對齊和糾偏,以實現同步或交錯采樣。JESD204B子類識別對于了解系統的時序對齊功能非常重要。系統ADC兩端SYSREF和CLK輸入引腳的時序收斂對于實現時間對齊采樣至關重要。

審核編輯:郭婷

電子發燒友App

電子發燒友App

評論