本文介時鐘頻率概念及其對系統性能的影響,并在電路板級、芯片級和單元模塊級分別提供了減小相位噪聲和抖動的有效方法。

2012-03-10 09:55:23 4544

4544

Analog Devices, Inc.(ADI),最近發布了一款提供領先相位噪聲性能的PLL頻率合成器ADF4153A。

2012-11-01 09:09:20 1497

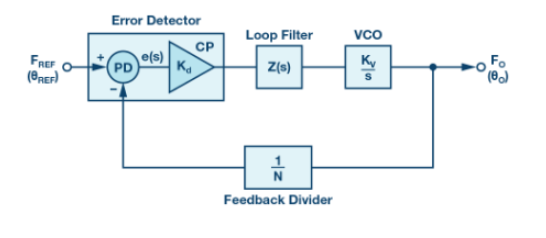

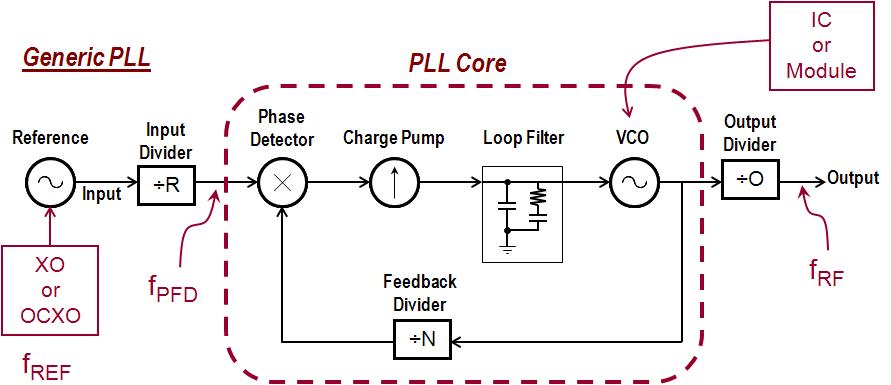

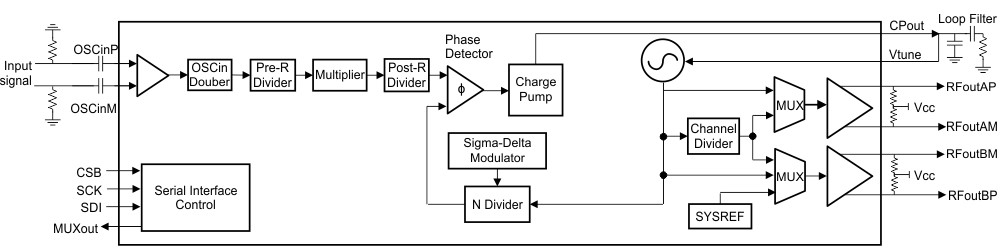

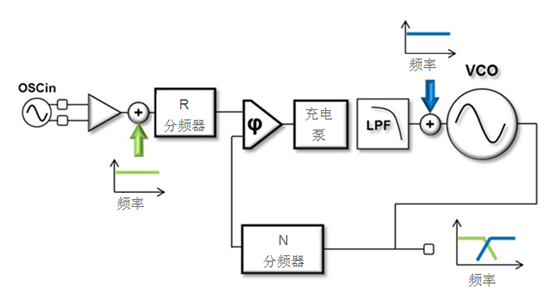

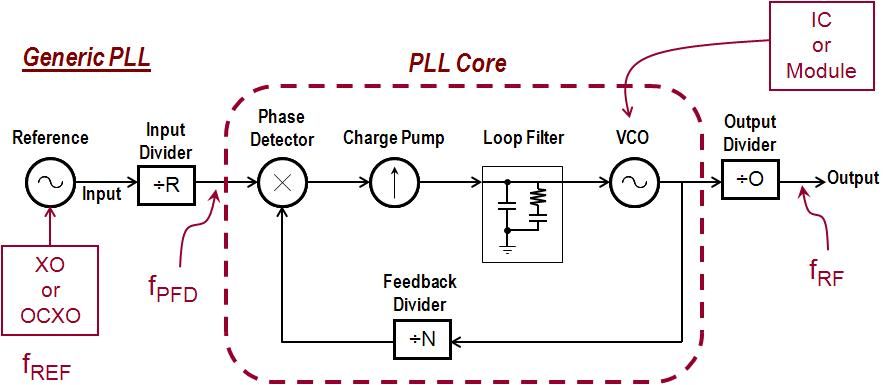

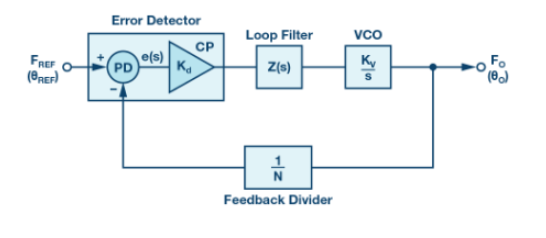

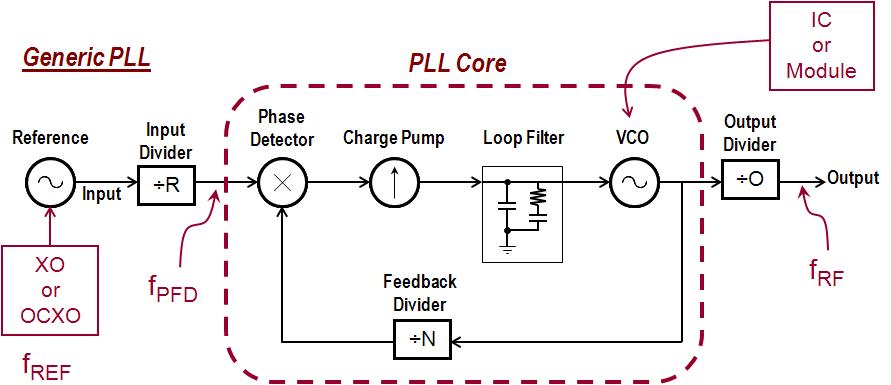

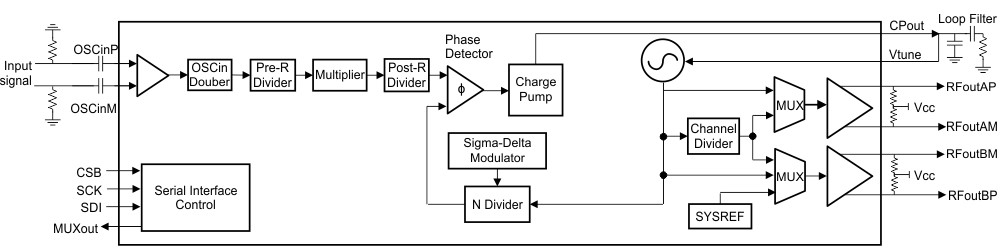

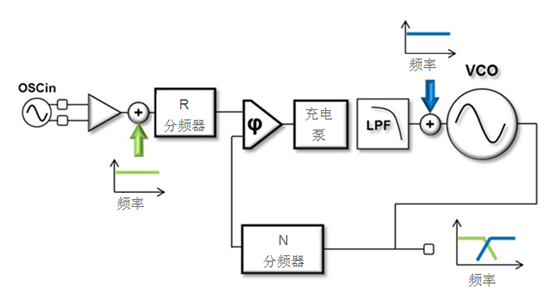

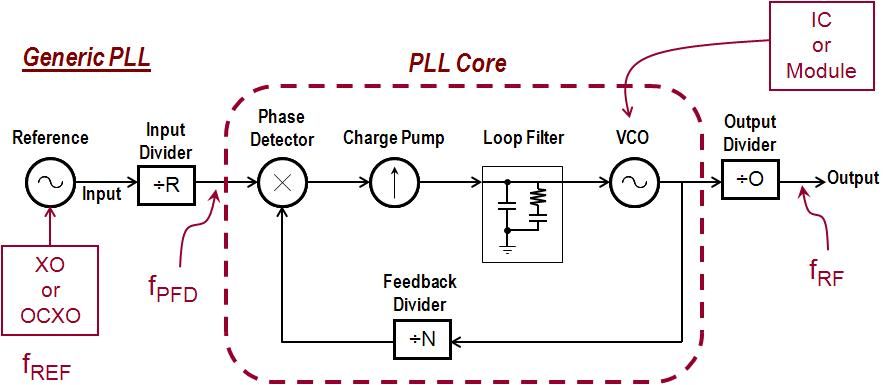

1497 。當比較結果處于穩態,即輸出頻率和相位與誤差檢測器的輸入頻率和相位匹配時,我們說PLL被鎖定。就本文而言,我們僅考慮ADI ADF4xxx系列PLL所實現的經典數字PLL架構。 該電路的第一個基本元件是鑒頻鑒相器(PFD)。PFD將輸入到REFIN的頻率和相位與反饋到RFIN的頻率和相位進

2021-03-02 16:34:02 3806

3806

已經有段時間了。但是,在要求快速切換速度、低相位噪聲或低雜散信號電平的場合,有必要使用更為復雜的架構。通過正確的設計方法,結合使用現代低成本高集成度的PLL和直接數字合成器(DDS)集成電路(IC)可以極大地促進高性能架構的實現。

2022-10-14 10:30:36 2025

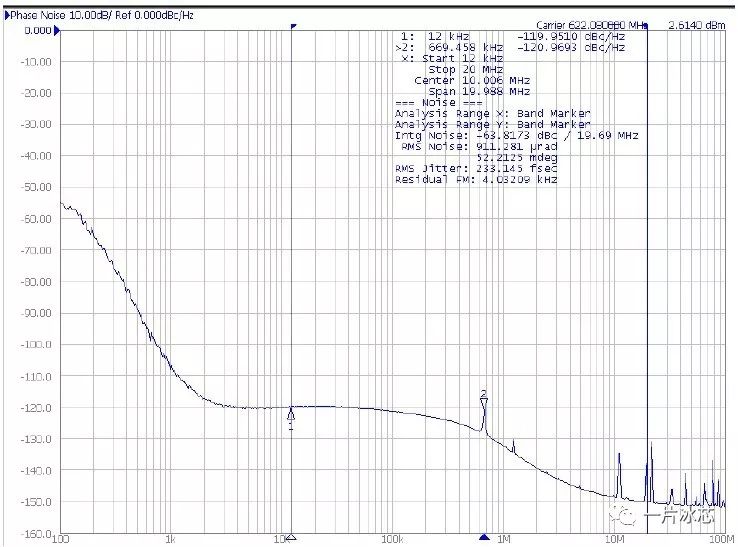

2025 本篇文章是關于相位鎖定環(PLL)頻率合成器的設計和分析,重點討論了相位噪聲和頻率噪聲的測量、建模和仿真方法。文章以設計一個假想的PLL頻率合成器為例,詳細介紹了設計過程和步驟。從規格選擇、電路配置

2023-10-26 15:30:51 483

483

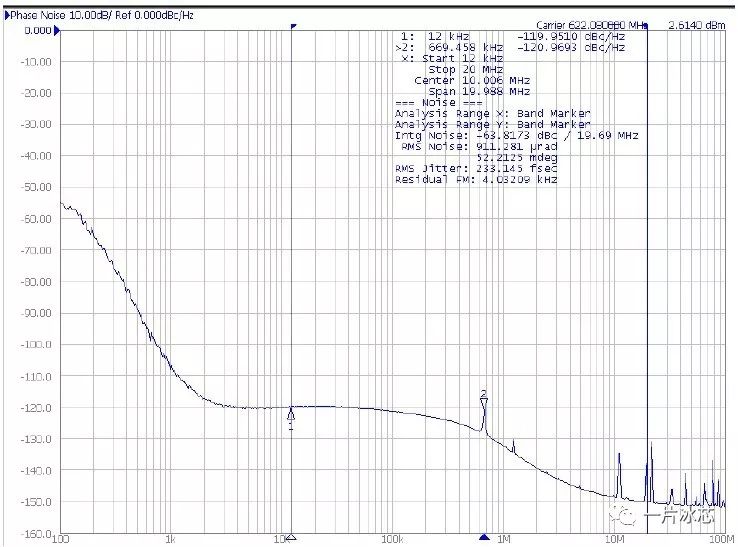

相位噪聲轉換到抖動的基本思想就是對相位噪聲曲線進行積分。

2023-10-30 16:06:01 1025

1025

)如何影響PLL相位噪聲的示例。例如,文獻中對ADP3334和ADP150 LDO為ADF4350供電時的性能進行了比較。ADP3334調節器的集成均方根噪聲為27 μV(40多年來,從10 Hz至100

2018-12-21 09:05:27

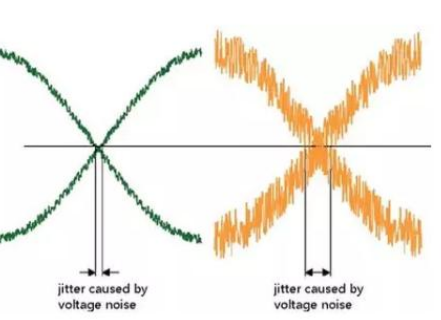

測量抖動性能的設備內,這種機理也表現得很明顯。 時鐘性能測量 工程師常常會評估無意義的實驗室結果;而時鐘性能測量的問題尤其嚴重。例如,你可使用示波器和相位噪聲分析儀(PNA)測量隨機抖動。不過,結果

2018-09-19 11:47:50

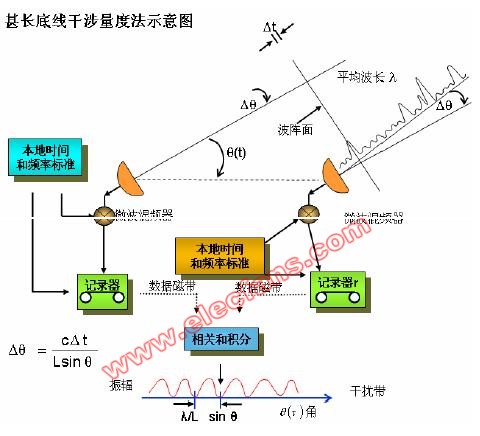

、相位噪聲的意義 頻率源的相位噪聲是一項非常重要的性能指標,它對電子設備和電子系統的性能影響 很大,從頻域看它分布在載波信號兩旁按冪律譜分布。用這種信號不論做發射激勵信 號,還是接收機本振信號以及各種頻率

2017-10-09 10:44:20

我正在使用E5052B信號源分析儀來獲取相位噪聲數據,載波頻率為20.460802MHz,頻率范圍為1Hz至5MHz。我試圖將導出為.csv文件的相位噪聲數據轉換為RMS抖動(弧度),但是我在整個

2018-10-10 17:50:29

新興的PLL + VCO (集成電壓控制振蕩器的鎖相環)技術能夠針對蜂窩/4G、微波無線電防務等應用快速開發低相位噪聲頻率合成器,ADI集成頻綜產品的頻率覆蓋為25 MHz到13.6 GHz。

2019-08-01 07:23:09

~156.25MHz范圍的低抖動時鐘源。在理想的供電條件下,小數分頻PLL可在1 0kHz~20MHz頻段內提供低于lps RMS的抖動性能。相反,在有電源噪聲的環境中,振蕩器很難滿足其數據手冊中標明的相位抖動參數

2018-09-26 14:33:58

`這些高性能系統中的系統設計人員將選擇超低相位噪聲振蕩器,并且從噪聲角度來講,信號鏈的目標就是使振蕩器相位噪聲曲線的惡化最小。這就要求對信號鏈上的各種元器件做殘余或加性的相位噪聲測量。 最近發布

2019-03-19 22:09:54

和高相位檢測器頻率可實現非常低的帶內噪聲和集成抖動。高速 N 分頻器沒有預分頻器,從而顯著減少了雜散的振幅和數量。還有一個可減輕整數邊界雜散的可編程輸入乘法器。LMX2594 允許用戶同步多個器件

2021-03-24 15:59:47

”架構,其輸出頻率是鑒相器頻率的整數倍。為提供較小的頻率步進,整數倍增因子必須非常大。大量本振相位噪聲源于參考路徑,并被PLL頻率倍增因子所放大,這將導致PLL輸出端產生很高的帶內噪聲。小數N分頻

2018-08-21 09:21:18

,REFIN的高相位噪聲(圖6)由低通濾波器濾除。由PLL的參考和PFD電路貢獻的所有帶內噪聲都被低通濾波器濾除,只在環路帶寬外(圖8)留下低得多的VCXO噪聲(圖7)。當輸出頻率等于輸入頻率時,PLL配置最簡單。這種PLL稱為時鐘凈化PLL。對于此類時鐘凈化應用,建議使用窄帶寬(

2019-10-02 08:30:00

。圖2中有一個在頻域中工作的負反饋控制環路。當比較結果處于穩態,即輸出頻率和相位與誤差檢測器的輸入頻率和相位匹配時,我們說PLL被鎖定。就本文而言,我們僅考慮ADI公司ADF4xxx系列PLL所實現

2019-01-28 16:02:54

特征?單個3.3V電源?高性能時鐘發生器,包括集成頻率合成器的晶體振蕩器電路?低輸出抖動,低至380 fs(rms集成在10 kHz–20 MHz之間)?高頻下的低相位噪聲;在708 MHz時,在

2020-09-10 17:45:08

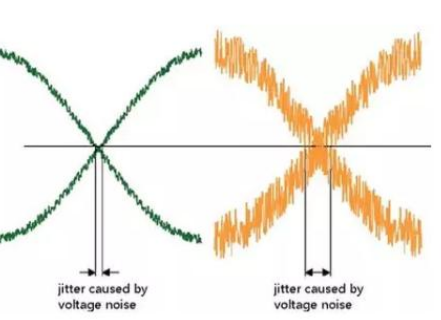

一、什么是相位噪聲? 相位噪聲表示在波形的頻域中,由相位(頻率)的快速,短期,隨機波動組成。這是由時域不穩定性(抖動)引起的。 確保不要將相位噪聲與抖動混淆。抖動 是一種描述晶振在時域

2021-03-15 14:13:57

ADIsimPLL中建模。從所示的ADIsimPLL曲線中可以看出,REFIN的高相位噪聲(圖6)由低通濾波器濾除。由PLL的參考和PFD電路貢獻的所有帶內噪聲都被低通濾波器濾除,只在環路帶寬外(圖8)留下

2018-10-25 10:25:31

。相位噪聲通常定義為一個振蕩器在某一偏移頻率fm處1Hz寬帶內的單邊信號功率和信號的總功率比值,單位是dBc/Hz.通常表示為dBc/Hz@fm。相位噪聲的形成因素主要三方面:· A區主要是晶體Q值來

2020-06-10 17:38:08

變化的敏感; A型我電荷泵的PLL頻率合成器是在這項工作中提出。閉環系統的穩定是實現使用一個離散時間環路濾波器。 I型系統架構導致開關速度快。離散時間環路濾波器的相位/頻率檢測器和VCO調諧節點之間的隔離。因此性能可以達到一個良好的刺激。PLL博士論文_全集成頻率綜合器[hide][/hide]

2011-12-15 11:17:56

十分重要。

相位噪聲

相位噪聲(Phase Noise)是抖動在測量儀器上的表現,通常定義為一個振蕩器在某一偏移頻率fm處1Hz寬帶內的單邊信號功率和信號總功率比值,單位是dBc/Hz,通常表示為

2023-12-14 09:19:08

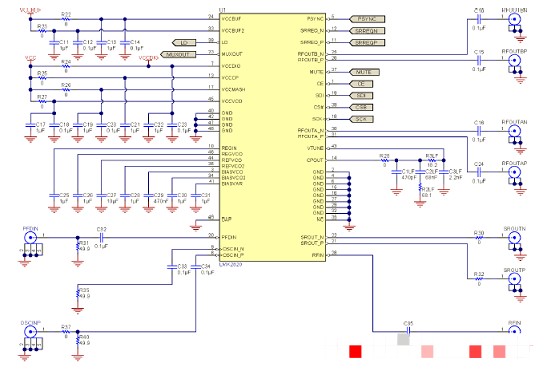

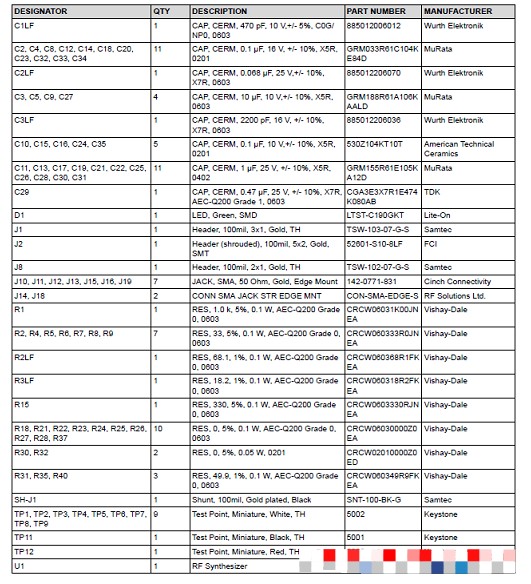

DC1795A,用于LTC6950的演示板,具有時鐘分配的1.4GHz低相位噪聲,低抖動PLL。演示電路1795A采用具有時鐘分配的LTC6950,1.4 GHz低相位噪聲,低抖動PLL。為了便于

2019-02-25 09:55:24

時鐘頻率的不斷提高使相位噪聲和抖動在系統時序上占據日益重要的位置。本文介其概念及其對系統性能的影響,并在電路板級、芯片級和單元模塊級分別提供了減小相位噪聲和抖動的有效方法。

2019-06-05 07:13:30

隨著數據轉換器的速度和分辨率不斷提升,對具有更低相位噪 聲的更高頻率采樣時鐘源的需求也在不斷增長。時鐘輸入面臨 的積分相位噪聲(抖動)是設計師在設計蜂窩基站、軍用雷達 系統和要求高速和高性能時鐘信號

2019-10-31 08:00:00

于相位噪聲、鎖定時間或雜散卻并非如此。表1給出了環路帶寬對這些性能指標的影響的大致參考。 性能指標最優帶寬備注抖動BWJIT最優值一般為BWJIT。在低集成限制更高的一些情況下,有時較窄的環路帶寬實際上效果更好。鎖定時間無限VCO鎖定時間隨著環路帶寬的增加而提高,但有時會受到VCO校準時間…

2022-11-16 07:56:45

本文針對全方位的信號路徑系統中的高速全差分運放及高頻寬14位模擬/數字轉換器的隨機及固定時鐘抖動,具體分析、研究了超低噪聲兼時鐘抖動濾除技術。研究選用雙級聯PLLatinum架構,配置高性能壓控振蕩器(VCXO),很好地實現了降噪和時鐘抖動濾除的作用。

2019-07-05 07:47:46

的時鐘源。隨著集成電路加工中功能器件的尺寸縮小,器件電源電壓也呈下降趨勢,包括PLL和其它混合信號功能所用的電源。然而,PLL的關鍵元件——“壓控振蕩器”(VCO)的實用技術要求并未隨之大幅降低。許多高性能

2019-06-26 06:39:37

概述:LTC6945是一款高性能、低噪聲、6GHz 鎖相環 (PLL),包括一個基準分頻器、具鎖相指示器的相位-頻率檢測器 (PFD)、充電泵、整數反饋分頻器和 VCO 輸出分頻器。

2021-04-09 06:34:49

什么是抖動和相位噪聲?如何區分抖動和相位噪聲?

2021-03-11 07:03:13

的方法。請注意環路帶寬上方總相位噪聲與VCO的跟蹤調諧以及環路帶寬下方總相位噪聲與PLL的跟蹤調諧。

圖2:LMX2592預估相位噪聲曲線圖(帶100-MHz相位檢測器頻率的6-GHz輸出),借助

2018-08-31 09:46:39

頻率為250MHz時,壓控增益線性區頻率覆蓋范圍是60~480MHz,在偏離中心頻率600 kHz處的相位噪聲為-108 dBc/Hz,較文獻中傳統的反相器延遲單元的環形VCO性能有明顯的改善。說明

2021-02-25 07:39:43

、相位噪聲、抖動、鎖定時間和其他表示頻率合成電路總體性能的特性。轉換環路是基于PLL概念的另一類頻率合成器,但采用不同的方法實現。如圖1b所示,其反饋環路中使用的是集成下變頻混頻級,而不是N分頻器,環路

2022-03-14 16:17:39

非常有用。VPOS_PLL 具有最差電源抑制性能,因此,是最靈敏的電源節點。該電源引腳驅動PLL 電路,包括參考輸入頻率、相位頻率檢測器和電荷泵。這些靈敏的功能模塊決定著LO 信號的精度和相位性能,因此

2019-10-17 09:06:34

高信噪比=低ADC孔徑抖動嗎?在設計中,為了避免降低ADC的性能,工程師一般會采用抖動極低的采樣時鐘。然而,用于產生采樣時鐘的振蕩器常常用相位噪聲而非時間抖動來描述特性。那么,有木有方法將振蕩器相位噪聲轉換為時間抖動呢?

2019-08-13 06:27:54

MHz這個頻帶范圍內,某振蕩器的相位噪聲情況。圖中,L(f)以功率譜密度函數的形式給出了邊帶噪聲的分布,單位為dBc。中心頻率的功率并不重要,因為抖動只反映了相位噪聲(即調制)與“純”中心頻率處

2009-10-13 17:23:19

在本文中,我們將討論抖動傳遞及其性能,以及相位噪聲測量技術的局限性。 時鐘抖動和邊沿速率 圖1顯示了由一個通用公式表述的三種波形。該公式包括相位噪聲項“φ(t)”和幅度噪聲項“λ(t)。對評估的三個

2022-11-23 07:59:49

系統設計師通常側重于為應用選擇最合適的數據轉換器,在向數據轉換器提供輸入的時鐘發生器件的選擇上往往少有考慮。然而,如果不慎重考慮時鐘發生器的相位噪聲和抖動性能,數據轉換器動態范圍和線性度性能可能受到嚴重的影響。

2019-07-30 07:57:42

易失性存儲器并控制 PLL。因此,通過板載 MCU-IC 組合可以實現系統時鐘頻率的動態更新。開發人員可以使用可編程微控制器,為高性能時鐘 IC 提供控制邏輯。這可以減少對板載 IC 和走線數量的需求

2018-08-27 09:46:58

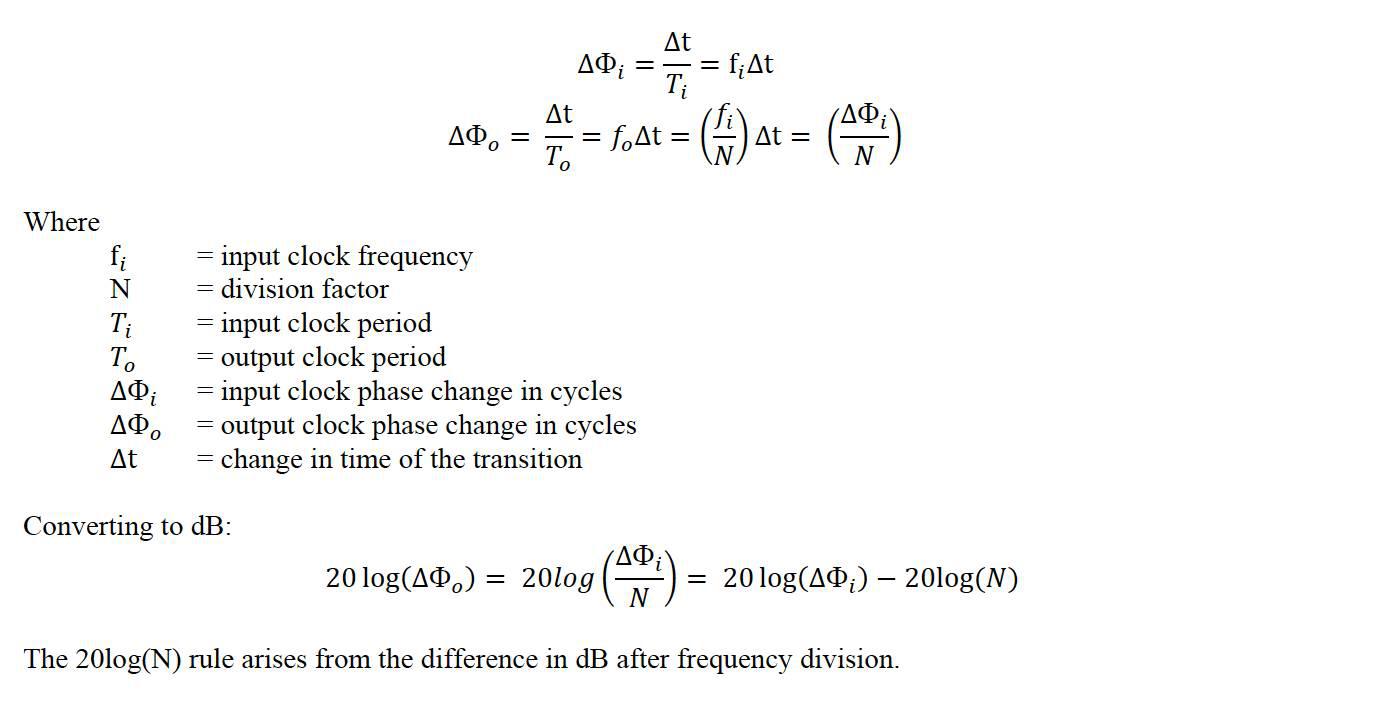

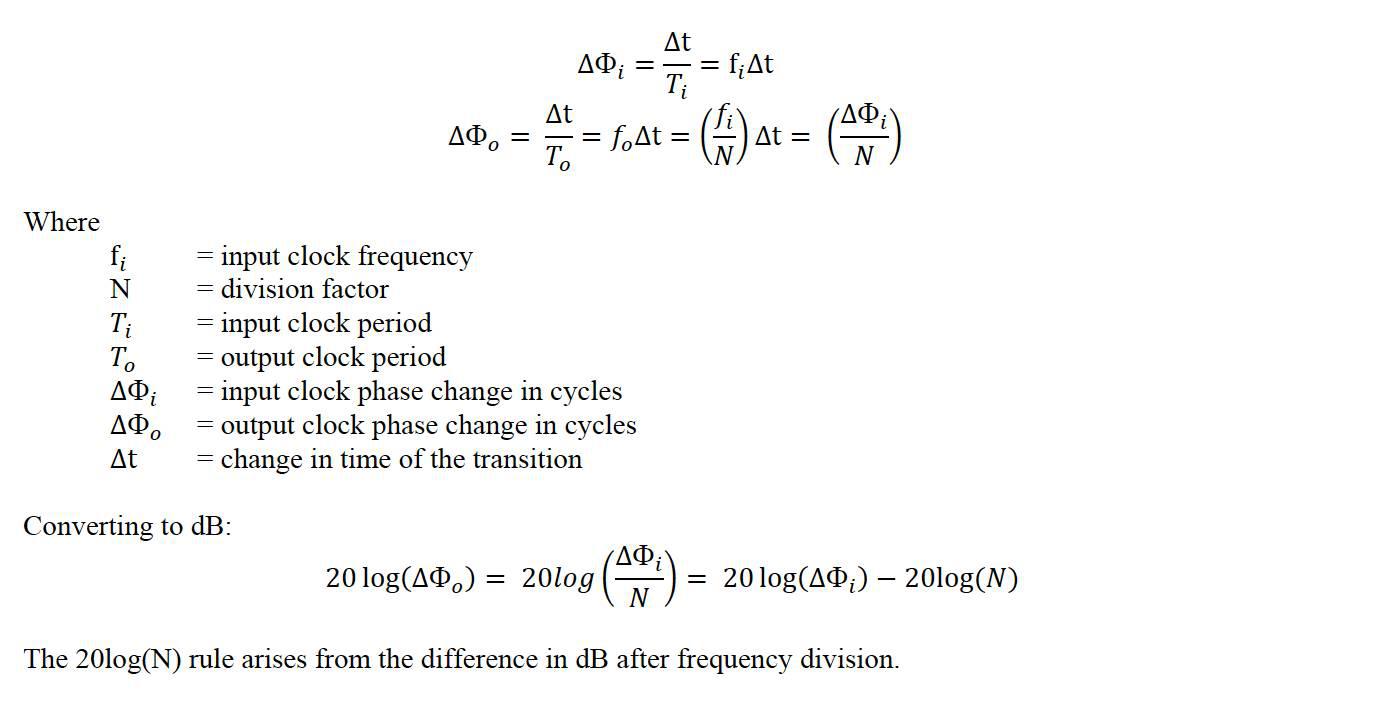

本期我將討論在測量較低時鐘頻率的相位噪聲和相位抖動時出現的一個非常常見的問題。在所有條件相同的情況下,我們通常期望分頻的低頻時鐘產生比高頻時鐘更低的相位噪聲。在數量上,你可能會記得這是20log(N

2021-06-24 07:30:00

高性能SiGe PLL與低相位噪聲GaAs VCO配對,用于微波無線電

2019-09-26 11:03:44

PLL,5 kHz偏移的帶內噪聲(根據ADIsimPLL計算)為-95 dBc / Hz。RFMD VCO 915-191U檢測適合應用的VCO,5 kHz偏移時的開環VCO相位噪聲為-101 dBc

2018-10-26 11:48:38

詳細介紹了具有外部VCO的完整12GHz,超低相位噪聲分數N鎖相環(PLL)的設計。它由高性能小數N分頻PLL(MAX2880),基于運算放大器的有源環路濾波器(MAX9632)和12GHz VCO

2018-12-10 09:50:52

)可以極大地促進高性能架構的實現。大部分高頻系統都使用傳統的基于整數分頻器的設計(圖1)或基于分數N分頻器的設計。不管是使用哪種設計,聯合使用單個通用頻率合成器IC和一個外部壓控振蕩器(VCO)通常都可以

2019-07-08 06:10:06

的范圍在100fs至300fs之間。這個12kHz-20MHz的標準相位噪聲集成范圍包括鎖相環 (PLL) 頻帶內和頻帶外 (VCO) 噪聲的影響。基準時鐘發生器的相位噪聲性能需要在PLL環路帶寬內

2018-09-05 16:07:30

而言是最優的,但對于相位噪聲、鎖定時間或雜散卻并非如此。表1給出了環路帶寬對這些性能指標的影響的大致參考。 性能指標最優帶寬備注抖動BWJIT最優值一般為BWJIT。在低集成限制更高的一些情況下,有時

2018-08-29 16:02:55

概述:LTC6946是一款全集成型 VCO 的高性能、低噪聲、6.39GHz 鎖相環 (PLL),它包括一個基準分頻器、具鎖相指示器的相位-頻率檢測器 (PFD)、超低噪聲充電泵、整數反饋分頻器和 VCO 輸出...

2021-04-13 06:31:10

頻率檢測器 (PFD) 頻率的優點,可實現超低帶內噪聲和集成的抖動。ADF4377 的基本 VCO 和輸出分頻器可產生 800 MHz 至 12.8 GHz 的頻率

2023-02-10 14:18:47

摘要:本文提出了一種對銷相環頻率合成器(PLL-FS)行為級建模后仿真,進行噪聲和抖動性能分析的方法。新方法借鑒了最新的理論成果,結合工程實踐,處于Top-Down 設計流

2009-12-14 11:32:35 9

9 PLL頻率合成器的噪聲基底測量

在無線應用中,相位噪聲是頻率合成器的關鍵性能參數。像PHS、GSM和IS-54等相位調制蜂窩系統的RF系統設計均需要低噪聲本地振蕩(L

2010-04-07 15:25:21 22

22 (MxFE)時鐘 應用。高性能PLL具有?239 dBc/Hz:歸一化 帶內相位噪聲本底,超低1/f噪聲,高 可實現超低的相位/頻率檢測器(PFD)頻率 帶內噪聲和集成抖

2024-01-04 19:31:37

1/f噪聲和高相位頻率檢測器(PFD)頻率,可以實現超低的帶內噪聲和集成抖動。ADF4377的基本VCO和輸出分頻器產生的頻率從800 MHz到12.8 GHz。

2024-02-26 09:29:37

鎖相環(PLL)和相移鍵控(PSK)系統的相位噪聲振蕩器的相位噪聲有可能導致相位變換的錯誤檢測,即在用相位鍵控法進行數字調制時產生誤碼。例如,

2008-11-24 12:40:59 1796

1796

摘要:這是一篇關于時鐘(CLK)信號質量的應用筆記,介紹如何測量抖動和相位噪聲,包括周期抖動、逐周期抖動和累加抖動。本文還描述了周期抖動和相位噪聲譜之間的關系,并介紹

2009-04-22 10:16:50 3736

3736

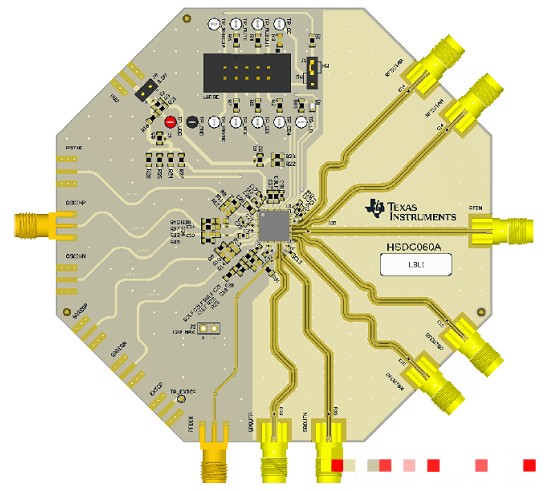

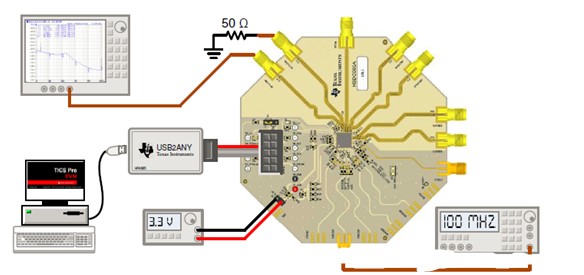

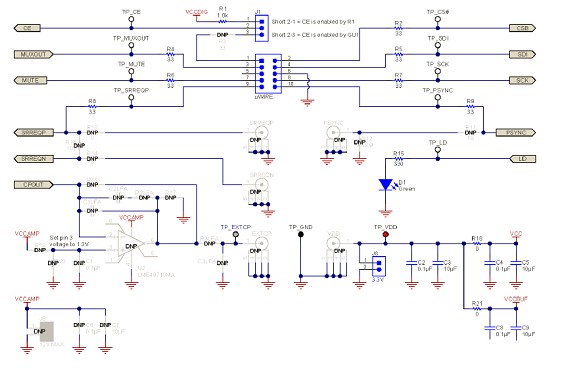

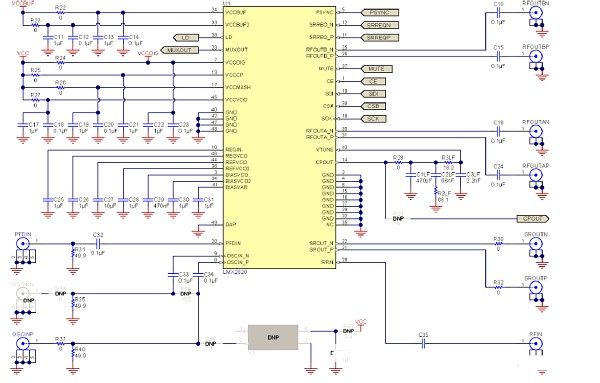

評估低抖動PLL時鐘發生器的電源噪聲抑制性能

本文介紹了電源噪聲對基于PLL的時鐘發生器的干擾,并討論了幾種用于評估確定性抖動(DJ)的技術方案。推導出的關系式提

2009-09-18 08:46:32 1461

1461

相位噪聲和抖動的概念及其估算方法

時鐘頻率的不斷提高使相位噪聲和抖動在系統時序上占據日益重要的位置。本文介其概念及其對系統性能的影

2009-12-27 13:30:21 2173

2173

模數和數模轉換器采樣時鐘內的抖動會對可實現的最大信噪比造成限制(參見參考文獻部分van de Plassche著《集成模數和數模轉換器》)。本應用筆記闡述了相位噪聲和抖動的定義,繪制

2011-11-24 14:31:55 75

75 ADF4350/1系列是什么? ADF4350和ADF4351由一系列產品組成,這些產品將高性能整數N分頻或小數N分頻PLL與超低相位噪聲VCO集成在一個小型LFCSP封裝中。 ADF4350/1均為頻率合成器(PLL+VCO),集領先

2012-06-08 18:06:49 185

185 采樣時鐘抖動可對高性能ADCs信噪比性能的災難。雖然信噪比和抖動之間的關系是眾所周知的,但是大多數振蕩器都是根據相位噪聲來指定的。

2017-08-03 10:57:33 13

13 該應用報告提出了在TI儀器上的CDCE72010抖動清理器和同步器PLL器件上獲取的相位噪聲數據。CDCE72010的相位噪聲性能取決于基準時鐘、VCXO時鐘和CDCE72010本身的相位噪聲。該應用報告顯示了幾個最流行的CDMA頻率的相位噪聲性能。此數據有助于用戶為特定應用選擇正確的時鐘解決方案。

2018-05-15 10:58:53 7

7 合成器,整合了 PLL 內核與一個業界領先的低相位噪聲 VCO。此外,PLLWizard 設計工具還可簡化合成器的設計、準確地對其性能進行仿真、并使系統迅速啟動和運行。

LTC6945 和 LTC6946 頻率合成

2018-06-05 13:45:00 3207

3207

如果一個時鐘的載波頻率下降了N倍,那么我們預計相位噪聲會減少20log(N)。例如,每個除以因子2的除法應該導致相位噪聲減少20log(2)或大約6dB。這里的主要假設是無噪聲的傳統數字分頻器。

2018-09-28 08:14:00 10038

10038

在產生高頻,高線性度信號源時,低相位噪聲至關重要。相位噪聲是信號的不期望的變化或相位變化的量度。它在頻域中測量并且等于時域中的抖動。使用PLL合成器時,總相位噪聲由各種電路模塊和元件的匯編組成,每個

2019-04-16 08:40:00 3411

3411

如果在給定的偏移頻率下有一個相位噪聲規范,那么應該將VCO和參考相位噪聲信息提供給工具,例如ADIsimCLK,并使用它來優化閉環帶寬實現預期目標。該過程實質上是調整閉環帶寬以折衷參考和VCO相位噪聲。

2019-04-10 10:32:46 6537

6537

本視頻對ADI公司的高性能RF PLL和PLL VCO進行了簡要介紹,展示我們在頻率范圍、帶寬、低相位噪音和低功率雜散方面的技術進步,涵蓋所有市場和應用領域。

2019-08-02 06:18:00 4763

4763 通過演示簡要介紹鎖相環(PLL)中可實現的領先相位噪聲和雜散性能。

2019-05-21 06:23:00 5321

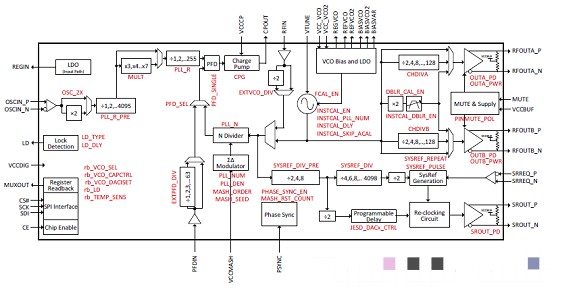

5321 LMX2594是一款高性能寬帶合成器,可在不使用內部加倍器的情況下生成 10MHz 至 15GHz 范圍內的任何頻率,因而無需使用分諧波濾波器。品質因數為 -236dBc/Hz 的高性能 PLL 和高相位檢測器頻率可實現非常低的帶內噪聲和集成抖動。

2019-05-10 16:05:59 14029

14029

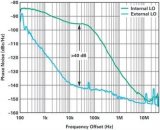

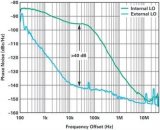

通過分析ADRV9009收發器的測量結果,其噪聲性能結果卻決于所選架構,不同架構結果差異較大。使用內部LO功能時,相位噪聲由IC內部的鎖相環(PLL)和壓控振蕩器(VCO)決定。內部LO

2021-01-04 16:23:37 3607

3607

ADF4196:低相位噪聲、快速建立、6 GHz PLL頻率合成器數據表

2021-04-23 17:13:01 1

1 ADF4193:低相位噪聲、快速建立PLL頻率合成器數據表

2021-04-27 21:07:31 3

3 (LO)或高速時鐘時,相位噪聲性能對滿足系統要求起到了重要作用。最初從數據表中推斷出該規格時似乎就像一個獨立的項目。下面我來講解一下如何通過讀取PLL的相位噪聲規格來對您的無線電或高速應用可達到的性能

2021-11-24 15:40:06 2266

2266

每當介紹相位噪聲測試方案時,都會提到時間抖動,經常提到二者都是表征信號短期頻率穩定度的參數,而且是頻域和時域相對應的參數。正如題目所示,相位噪聲與時間抖動有著一定的關系,那么相噪是與哪種類型的抖動相對應,彼此之間又有著怎樣的數學關系,這些疑問都將在文中找到答案。

2022-04-19 15:27:05 2450

2450 時鐘抖動使隨機抖動和相位噪聲不再神秘

2022-11-07 08:07:29 4

4 在產生高頻、高線性度信號源時,低相位噪聲至關重要。相位噪聲是信號相位不希望的變化或變化的量度。它是在頻域中測量的,相當于時域中的抖動。使用PLL頻率合成器時,總相位噪聲由各種電路模塊和組件的匯編

2023-01-09 16:23:38 3613

3613

采用PLL的時鐘發生器廣泛用于網絡設備中,用于生成高精度和低抖動參考時鐘或保持同步網絡操作。大多數時鐘振蕩器使用理想、干凈的電源給出其抖動或相位噪聲規格。然而,在實際的系統環境中,電源可能會因板載開關電源或嘈雜的數字ASIC而受到干擾。為了在系統設計中實現最佳性能,了解這種干擾的影響非常重要。

2023-03-08 15:33:00 896

896

相位噪聲與時間抖動貌似毫不相干,但卻是形影不離的,都是描述信號頻率穩定性的參數,只是切入的角度不同。

2023-04-12 09:19:36 859

859 相噪是與哪種類型的抖動相對應?如何理解相位噪聲與時間抖動的關系? 相位噪聲與時間抖動是兩個在信號處理領域中經常涉及的概念。在討論相位噪聲時,我們常常聽到相位噪聲和時間抖動的聯系。因此,本文將探討相位

2023-10-20 15:08:11 561

561 本應用筆記詳細介紹了具有外部VCO的完整12GHz、超低相位噪聲小數N分頻鎖相環(PLL)的設計。它由高性能小數N分頻PLL (MAX2880)、基于運算放大器的有源環路濾波器(MAX9632

2023-10-28 14:45:41 6895

6895 為何測出的相位噪聲性能低于ADIsimPLL仿真預期值? 相位鎖定環(PLL)是一種重要的電路,可用于在不同領域中應用,如無線通信、數據傳輸、數字信號處理等。PLL將信號同步到參考時鐘的頻率和相位

2023-10-30 10:51:13 168

168 相位噪聲和抖動是對時鐘頻譜純度的兩種表述形式,一個是頻域一個是時域,從原理上來說,它們是等效的。

2023-10-30 16:02:46 687

687

、電源管理等領域得到廣泛應用。PLL可以實現鎖定輸入信號的相位或頻率,同時可以將輸出信號的頻率分頻或倍頻實現同步。但是,PLL的性能與相位噪聲直接相關,因此通過讀取PLL的相位噪聲規格可以對其性能進行初步評估。 相位噪聲指的是輸出信號相位隨時間變化的不穩

2023-10-31 10:33:23 217

217 如何評估分布式PLL系統的相位噪聲? 要評估分布式PLL系統的相位噪聲,我們需要先了解什么是PLL系統和相位噪聲。PLL(Phase Locked Loop)是一種電子電路,可以將輸入信號的相位鎖定

2023-11-06 10:26:29 218

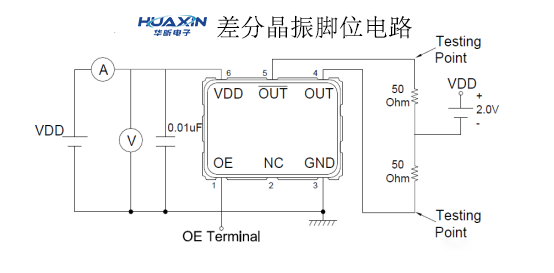

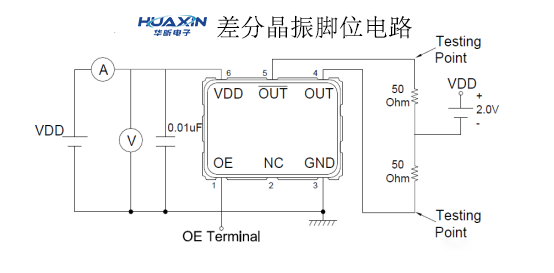

218 華昕 H-YF6 系列差分晶振是一款為滿足高性能時鐘信號需求而設計的產品。其低相位早上和低抖動使其成為通訊信息、測量和GPS定位等領域的理想選擇

2023-11-15 16:41:49 297

297

,包括電路穩定性不良、時鐘補償誤差、溫度變化、電磁干擾等。相位噪聲對信號有著廣泛的影響,包括降低信號的頻譜純度、引起功率泄露、產生頻率副瓣、導致系統誤碼率的提高等。 抖動是指信號的周期性變化,通常表現為時間軸上信號

2024-01-29 13:54:34 230

230 。本文將詳細介紹相位噪聲和時間抖動的定義、關系和測試方法。 首先,我們來了解相位噪聲的概念。相位噪聲是指信號的相位隨時間變化的不穩定性或擾動性。在理想情況下,一個信號的頻率應該是恒定的,但由于外部干擾或系統本

2024-01-31 09:29:00 138

138 。LDO的設計和特性直接影響到PLL的性能,尤其是相位噪聲。在本文中,我們將深入探討LDO如何影響PLL的相位噪聲。 首先,我們需要了解PLL的基本結構和工作原理。PLL由振蕩器、分頻器、鎖相環過濾器以及參考頻率源組成。其工作原理是通過反饋控制機制來將輸入信號

2024-01-31 16:43:11 172

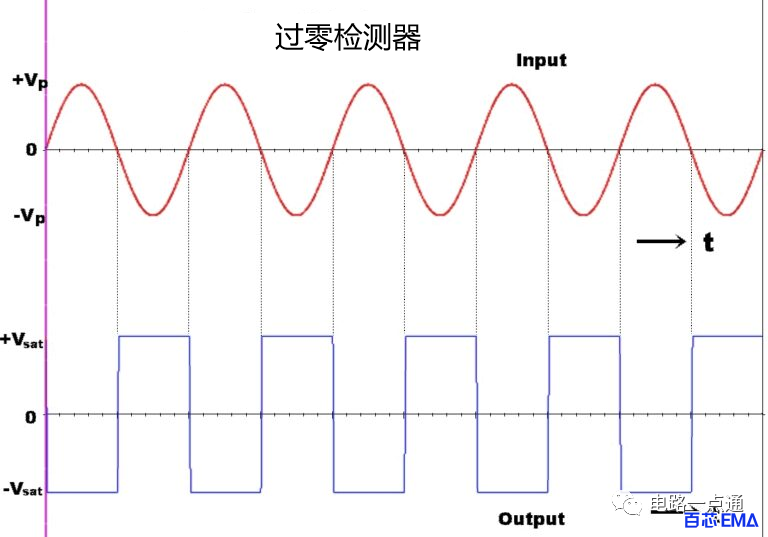

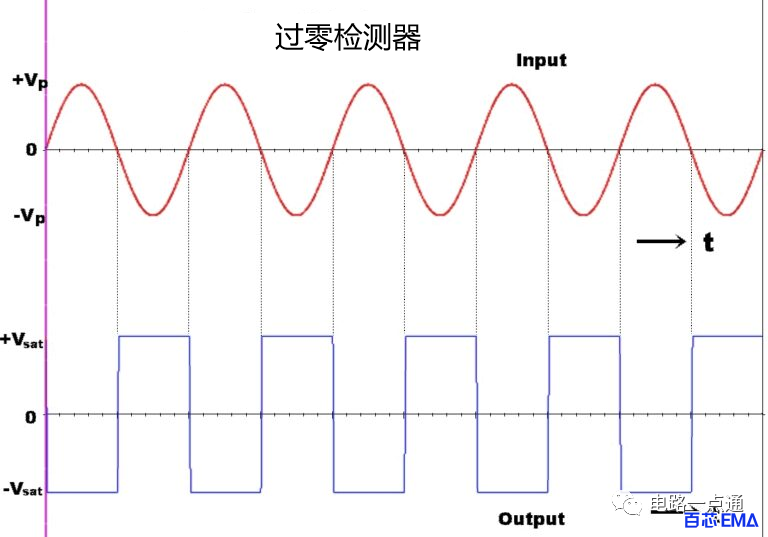

172 過零檢測器(Zero Crossing Detector,ZCD)是一種用于檢測信號波形過零點的電子設備。在許多應用中,如同步、相位鎖定環路(PLL)和頻率檢測等,過零檢測器都發

2024-02-01 14:12:06 295

295

電子發燒友App

電子發燒友App

評論