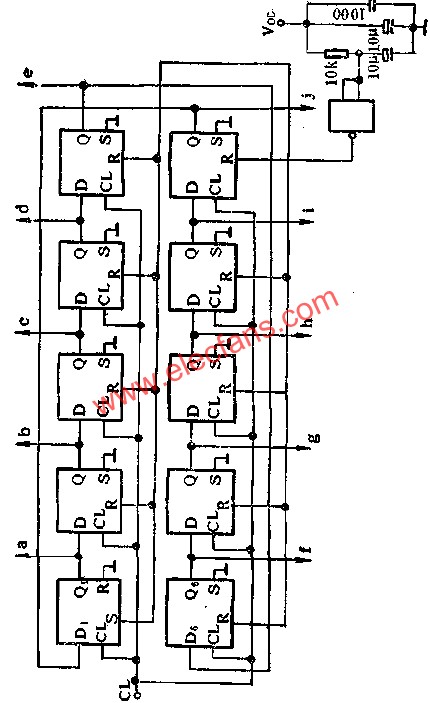

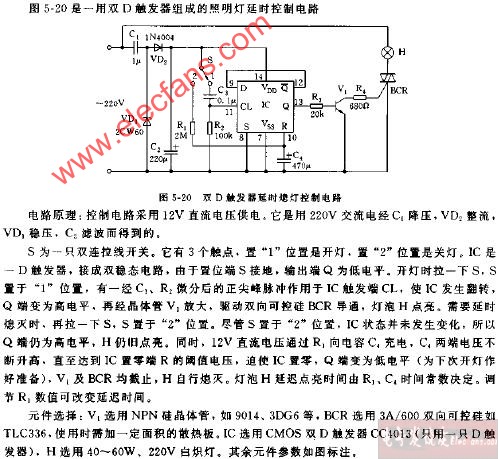

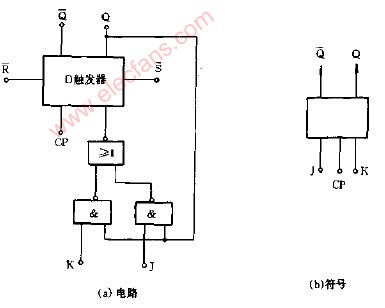

4D觸發器組成鎖存器電路圖

- 鎖存器(40691)

相關推薦

D觸發器與Latch鎖存器電路設計

D觸發器,是時序邏輯電路中必備的一個基本單元,學好 D 觸發器,是學好時序邏輯電路的前提條件,其重要性不亞于加法器,二者共同構成數字電路組合、時序邏輯的基礎。

2023-10-09 17:26:57 234

234

234

234

rs觸發器和rs鎖存器的區別是什么

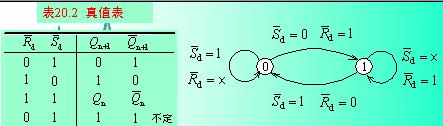

在傳統的異步 RS 觸發器中,當輸入的 R 和 S 同時為 1 時,會引發互鎖問題,輸出結果是不確定的。為了避免這個問題,常常使用帶有使能控制的同步觸發器,如帶有時鐘信號的 D 觸發器或 JK 觸發器。這些觸發器在時鐘邊沿上才會響應輸入信號,解決了異步 RS 觸發器的互鎖問題。

2023-08-28 15:44:35 641

641

641

641什么是D觸發器,D觸發器如何工作的?

鎖存器和觸發器有時組合在一起,因為它們都可以在其輸出上存儲一位(1或0)。與鎖存器相比,觸發器是需要時鐘信號(Clk)的同步電路。D 觸發器僅在時鐘從

2023-06-29 11:50:18 5258

5258

5258

5258

鎖存器、觸發器、寄存器和緩沖器的區別

的緩沖器(5)數據傳輸和處理中不同裝置間溫度和時間不同時,加一級緩沖器進行彌補等等。鎖存器與觸發器的區別鎖存器和觸發器是具有記憶功能的二進制存貯器件,是組成各種時序邏輯電路的基本器件之一。區別

2011-10-09 16:19:46

鎖存器和觸發器的定義和比較

鎖存器(latch)---對脈沖電平敏感,在時鐘脈沖的電平作用下改變狀態,當Gate輸入為高電平時,輸入D透明傳輸到輸出Q;當Gate從高變低或者保持低電平時,輸出Q被鎖存保持不變。鎖存器是電平觸發的存儲器。

2023-03-23 14:48:54 1357

1357

1357

1357

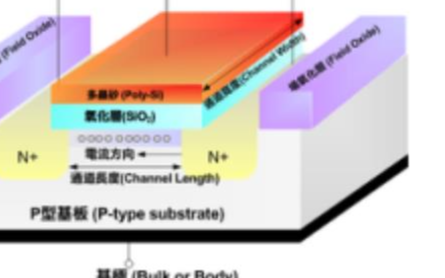

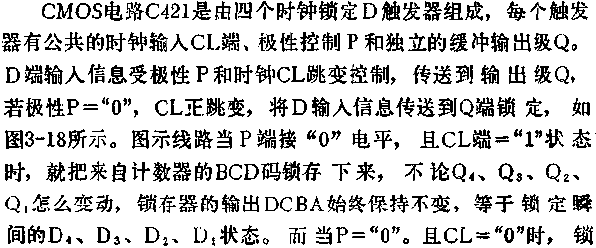

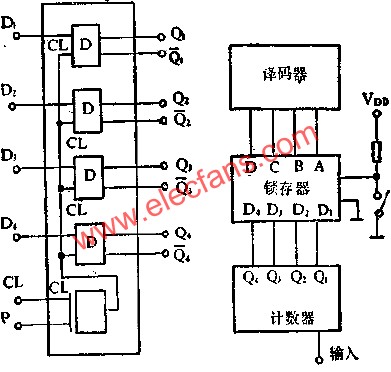

解讀從CMOS到觸發器 鎖存器常見結構與鎖存器應用

主要內容: ·雙穩態器件 ·鎖存器常見結構 ·鎖存器的應用 ·觸發器 ·觸發器的建立時間和保持時間 1、雙穩態器件 ** 雙穩態器件**是指穩定狀態有兩種,一種是0,一種是1的器件;雙穩態器件

2023-01-28 09:28:00 2426

2426

2426

2426

D觸發器不同應用下的電路圖詳解

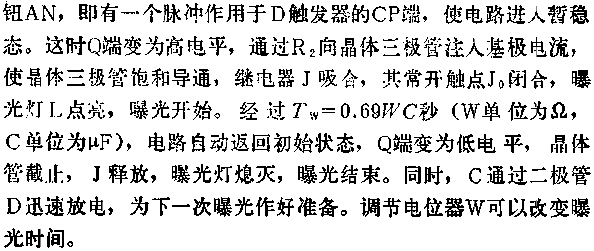

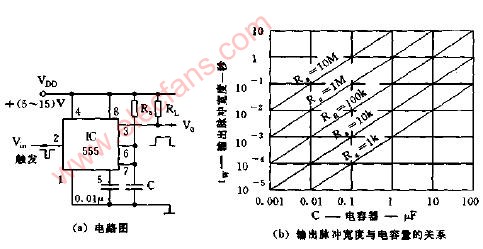

D 觸發器或數據觸發器是一種觸發器,它只有一個數據輸入“D”和一個時鐘脈沖輸入, 這種觸發器也稱為延遲觸發器,經常用于許多時序電路,如寄存器、計數器等。下面一起來了解一下D觸發器不同應用下的電路圖。

2023-01-06 14:19:46 1874

1874

1874

1874鎖存器、觸發器、寄存器的關聯與區別及其相應的verilog描述

1:鎖存器、觸發器、寄存器的關聯與區別 首先應該明確鎖存器和觸發器是由與非門之類的東西構成。尤其是鎖存器,雖說數字電路定義含有鎖存器或觸發器的電路叫時序電路,但鎖存器有很多組合邏輯電路的特性。 鎖存

2022-12-19 12:25:01 3721

3721

3721

3721淺談四種入門觸發器

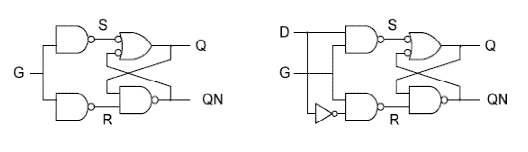

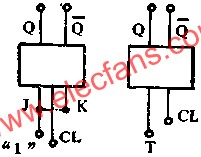

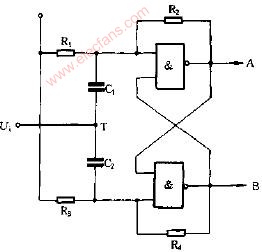

來源:羅姆半導體社區 觸發器的電路圖由邏輯門組合而成,其結構均由R-S鎖存器派生而來(廣義的觸發器包括鎖存器)。觸發器可以處理輸入、輸出信號和時鐘頻率之間的相互影響。 在R-S鎖存器的前面加一個由

2022-11-29 17:35:40 1584

1584

1584

1584rs觸發器電路圖與rs觸發器內部電路圖

rs觸發器電路圖與rs觸發器內部電路圖 rs觸發器電路圖 主從RS觸發器電路圖: 主從觸發器由兩級觸發器構成,其中一級接收輸入信號,其狀態直接由輸入信號決定,稱為主觸發器,還有一級的輸入與主觸發器

2022-10-19 19:16:03 16964

16964

16964

16964

帶有時鐘使能和同步清零的D觸發器

每個 Slice 有 8 個 FF 。四個可以配置為 D 型觸發器或電平敏感鎖存器,另外四個只能配置為 D 型觸發器,但是需要記得是:當原來的四個 FF 配置為鎖存器時,不能使用這四個 FF 。

2022-07-22 10:05:01 2518

2518

2518

25188位CPU設計(1) 門電路和鎖存器、觸發器

這是一個系列文章,從最簡單的門電路介紹,從基礎的鎖存器、觸發器、編碼器、譯碼器等一系列數字邏輯電路開始,最終構造一個簡易版的CPU實物

2021-11-06 09:20:58 16

16

16

16鎖存器與觸發器的區別

,鎖存器有兩個輸入,一個是有效信號EN,一個是輸入數據信號DATA_IN,有一個輸出Q,它的功能就是在EN有效的時候把DATA_IN的值傳給Q,也就是鎖存的過程。 2)觸發器 觸發器(Flip-Flop,簡寫為FF)也叫雙穩態門,又稱雙穩態觸發器,是一種可以在兩種

2020-11-29 11:02:11 20662

20662

20662

20662如何操作基本類型的鎖存器和觸發器

鎖存器(有時也稱為S/R鎖存器)是最小的存儲器塊。它們可以使用兩個NOR邏輯門(S和R為高電平有效)或兩個NAND門(輸入為低電平有效)構建,并用于構建更復雜的鎖存器和觸發器。

2019-07-30 11:23:28 5658

5658

5658

5658

d觸發器邏輯電路及符號

CP=1時,門。。打開,門。。被封鎖,從觸發器保持原來狀態不變,D信號進入主觸發器。但是要特別注意,這時主觸發器只跟隨而不鎖存,即。。跟隨D變化,D怎么變。。也隨之怎么變。

2019-07-15 08:57:32 42337

42337

42337

42337

D型觸發器電路真值表和計數器數的據鎖存器摘要

D型觸發器是一個改進的置位復位觸發器,增加了一個反相器,由此可見以防止S和R輸入處于相同的邏輯電平,此狀態將強制兩個輸出都處于邏輯“1”,超越反饋鎖存動作,無論哪個輸入先進入邏輯電平“1”都將失去控制,而另一個仍處于邏輯“0”的輸入控制鎖存器的結果狀態。

2019-06-26 15:36:28 14537

14537

14537

14537

鎖存器Latch和觸發器Flip-flop有何區別

本文首先介紹了鎖存器Latch結構和鎖存器latch的優缺點,其次介紹了觸發器Flip-flop的結構與優缺點,最后介紹了鎖存器Latch和觸發器Flip-flop兩者之間的區別。

2018-04-18 14:10:10 128942

128942

128942

128942

d鎖存器與sr鎖存器的區別

鎖存器就是把單片機的輸出的數據先存起來,可以讓單片機繼續做其它事。它的LE為高的時候,數據就可以通過它。當為低時,它的輸出端就會被鎖定RS觸發器是構成其它各種功能觸發器的基本組成部分。又稱為基本RS觸發器。

2018-01-31 14:48:13 28618

28618

28618

28618

鎖存器和觸發器的區別

鎖存器(latch)---對脈沖電平敏感,在時鐘脈沖的電平作用下改變狀態 鎖存器是電平觸發的存儲單元,數據存儲的動作取決于輸入時鐘(或者使能)信號的電平值,僅當鎖存器處于使能狀態時,輸出才會隨著數據輸入發生變化。

2017-11-02 09:24:41 92855

92855

92855

92855

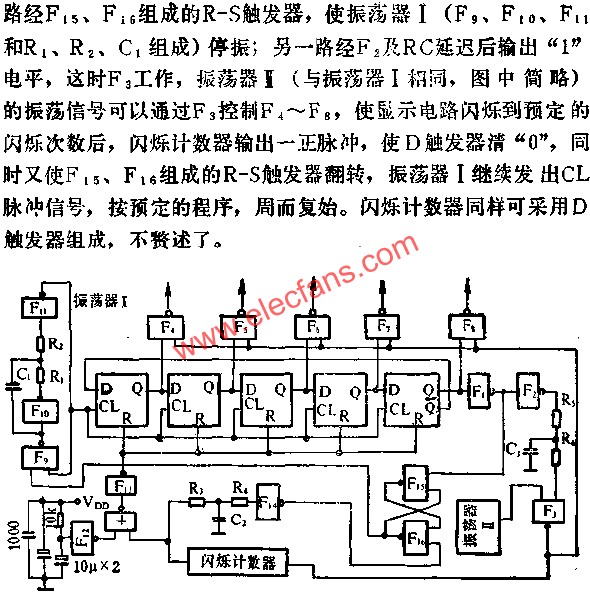

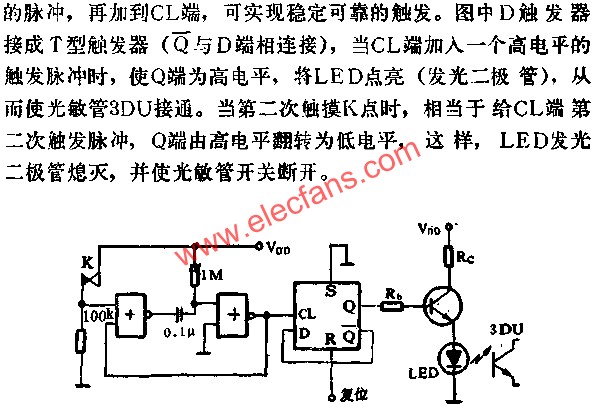

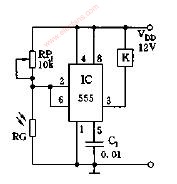

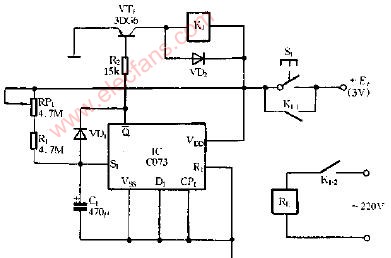

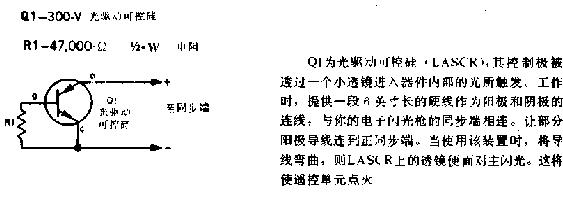

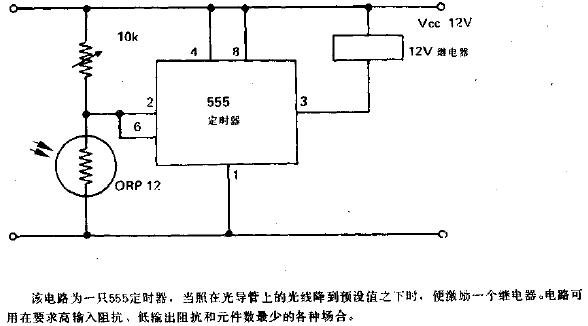

鎖控防盜報警電路圖

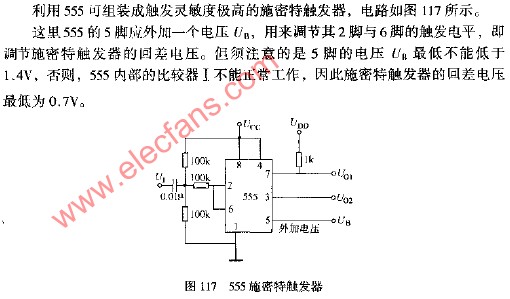

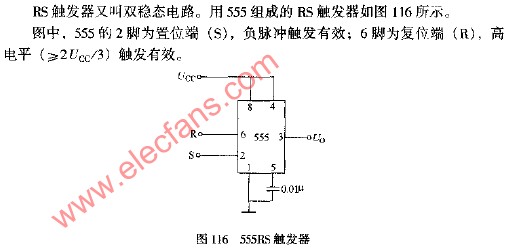

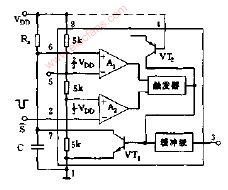

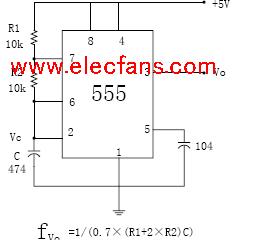

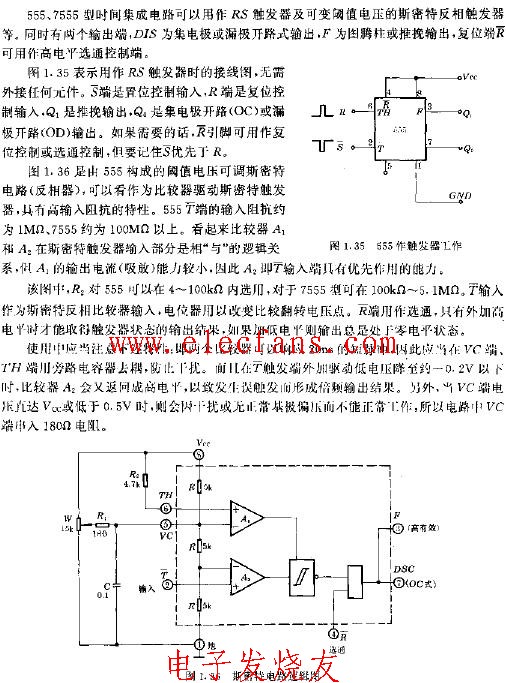

鎖控防盜報警電路圖,該電路由RS觸發器、選通振蕩器、報警電路等組成。其中RS觸發器由與非門F2、F3組成,選通振蕩器由集成電路TWH8751和R、C組成。

2012-03-28 14:30:02 3464

3464

3464

3464

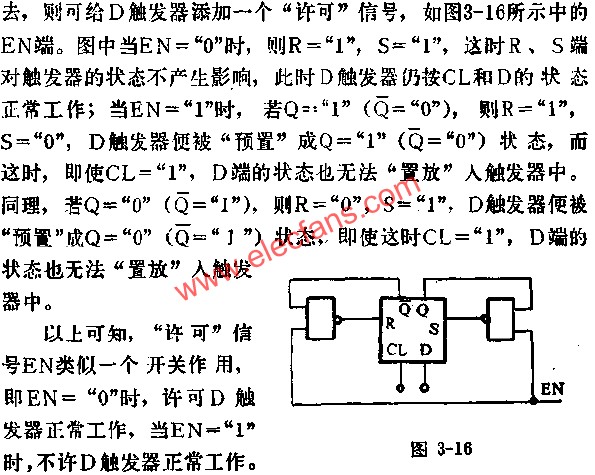

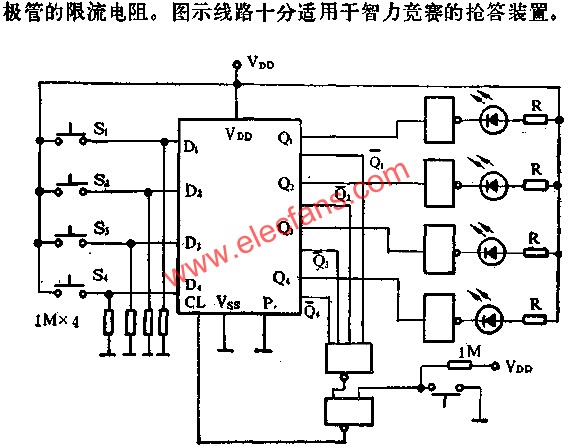

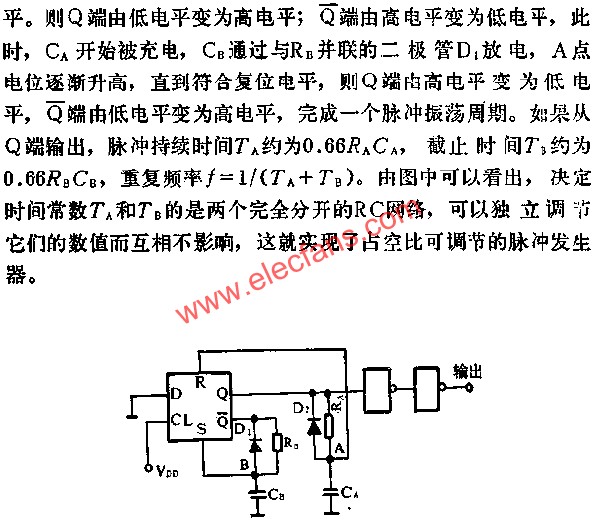

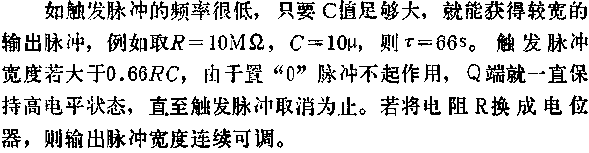

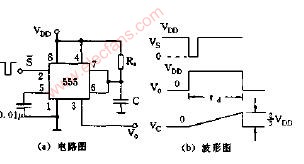

D觸發器加“許可”信號電路圖

從D觸發器的真值表可知,當時鐘脈沖CL="1"時,數據輸入端D的狀態會被“置放”入觸發器中去,而與觸發器原狀無關。如果當時鐘沖CL="1",D端狀態不旋轉放入

2010-09-21 01:27:59 577

577

577

577

鎖存器和觸發器原理

1、掌握鎖存器、觸發器的電路結構和工作原理;

2、熟練掌握SR觸發器、JK觸發器、D觸發器及T 觸發器的邏輯功能;

3、正確理解鎖存器、觸發器的動態特性

2010-08-18 16:39:35 233

233

233

233 電子發燒友App

電子發燒友App

評論