一、鎖存器

鎖存器(latch)---對脈沖電平敏感,在時鐘脈沖的電平作用下改變狀態 鎖存器是電平觸發的存儲單元,數據存儲的動作取決于輸入時鐘(或者使能)信號的電平值,僅當鎖存器處于使能狀態時,輸出才會隨著數據輸入發生變化。 鎖存器不同于觸發器,它不在鎖存數據時,輸出端的信號隨輸入信號變化,就像信號通過一個緩沖器一樣;一旦鎖存信號起鎖存作用,則數據被鎖住,輸入信號不起作用。鎖存器也稱為透明鎖存器,指的是不鎖存時輸出對于輸入是透明的。

鎖存器(latch):我聽過的最多的就是它是電平觸發的,呵呵。鎖存器是電平觸發的存儲單元,數據存儲的動作取決于輸入時鐘(或者使能)信號的電平值,當鎖存器處于使能狀態時,輸出才會隨著數據輸入發生變化。(簡單地說,它有兩個輸入,分別是一個有效信號EN,一個輸入數據信號DATA_IN,它有一個輸出Q,它的功能就是在EN有效的時候把DATA_IN的值傳給Q,也就是鎖存的過程)。

應用場合:數據有效遲后于時鐘信號有效。這意味著時鐘信號先到,數據信號后到。在某些運算器電路中有時采用鎖存器作為數據暫存器。

缺點:時序分析較困難。

不要鎖存器的原因有二:1、鎖存器容易產生毛刺,2、鎖存器在ASIC設計中應該說比ff要簡單,但是在FPGA的資源中,大部分器件沒有鎖存器這個東西,所以需要用一個邏輯門和ff來組成鎖存器,這樣就浪費了資源。

優點:面積小。鎖存器比FF快,所以用在地址鎖存是很合適的,不過一定要保證所有的latch信號源的質量,鎖存器在CPU設計中很常見,正是由于它的應用使得CPU的速度比外部IO部件邏輯快許多。latch完成同一個功能所需要的門較觸發器要少,所以在asic中用的較多。

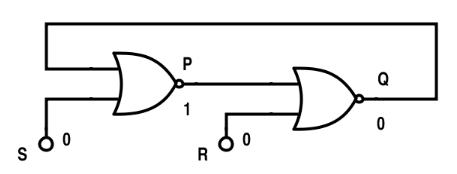

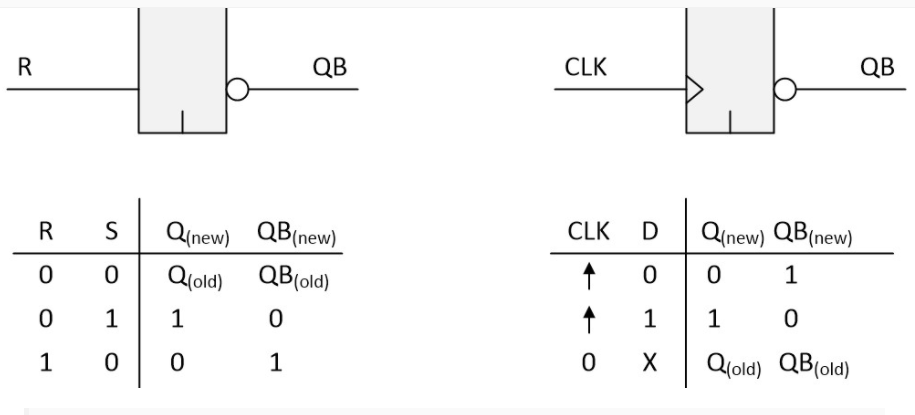

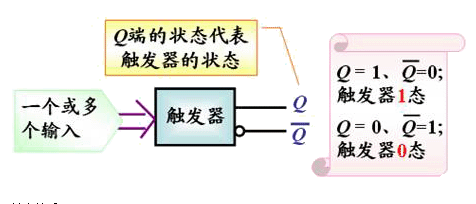

二、觸發器

觸發器(Flip-Flop,簡寫為 FF),也叫雙穩態門,又稱雙穩態觸發器。是一種可以在兩種狀態下運行的數字邏輯電路。觸發器一直保持它們的狀態,直到它們收到輸入脈沖,又稱為觸發。當收到輸入脈沖時,觸發器輸出就會根據規則改變狀態,然后保持這種狀態直到收到另一個觸發。

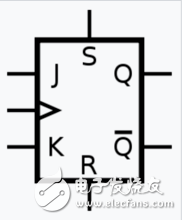

觸發器(flip-flops)電路相互關聯,從而為使用內存芯片和微處理器的數字集成電路(IC)形成邏輯門。它們可用來存儲一比特的數據。該數據可表示音序器的狀態、計數器的價值、在計算機內存的ASCII字符或任何其他的信息。 有幾種不同類型的觸發器(flip-flops)電路具有指示器,如T(切換)、S-R(設置/重置)J-K(也可能稱為Jack Kilby)和D(延遲)。典型的觸發器包括零個、一個或兩個輸入信號,以及時鐘信號和輸出信號。一些觸發器還包括一個重置當前輸出的明確輸入信號。第一個電子觸發器是在1919年由W.H.Eccles和F.W.Jordan發明的。

觸發器(flip-flop)---對脈沖邊沿敏感,其狀態只在時鐘脈沖的上升沿或下降沿的瞬間改變。

T觸發器(Toggle Flip-Flop,or Trigger Flip-Flop)設有一個輸入和輸出,當時鐘頻率由0轉為1時,如果T和Q不相同時,其輸出值會是1。輸入端T為1的時候,輸出端的狀態Q發生反轉;輸入端T為0的時候,輸出端的狀態Q保持不變。把JK觸發器的J和K輸入點連接在一起,即構成一個T觸發器。

應用場合:時鐘有效遲后于數據有效。這意味著數據信號先建立,時鐘信號后建立。在CP上升沿時刻打入到寄存器。 三、寄存器

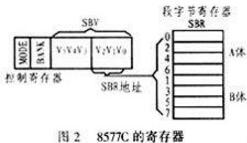

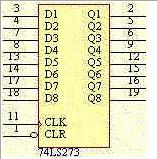

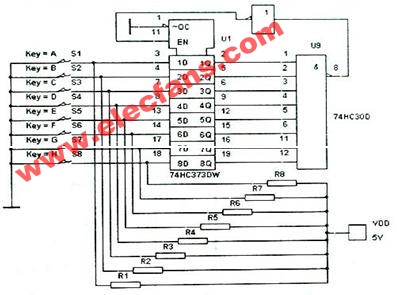

寄存器(register):用來存放數據的一些小型存儲區域,用來暫時存放參與運算的數據和運算結果,它被廣泛的用于各類數字系統和計算機中。其實寄存器就是一種常用的時序邏輯電路,但這種時序邏輯電路只包含存儲電路。寄存器的存儲電路是由鎖存器或觸發器構成的,因為一個鎖存器或觸發器能存儲1位二進制數,所以由N個鎖存器或觸發器可以構成N位寄存器。 工程中的寄存器一般按計算機中字節的位數設計,所以一般有8位寄存器、16位寄存器等。

對寄存器中的觸發器只要求它們具有置1、置0的功能即可,因而無論是用同步RS結構觸發器,還是用主從結構或邊沿觸發結構的觸發器,都可以組成寄存器。一般由D觸發器組成,有公共輸入/輸出使能控制端和時鐘,一般把使能控制端作為寄存器電路的選擇信號,把時鐘控制端作為數據輸入控制信號。

?

鎖存器與觸發器的區別

鎖存器和觸發器是具有記憶功能的二進制存貯器件,是組成各種時序邏輯電路的基本器件之一。區別為:latch同其所有的輸入信號相關,當輸入信號變化時latch就變化,沒有時鐘端;flip-flop受時鐘控制,只有在時鐘觸發時才采樣當前的輸入,產生輸出。當然因為latch和flip-flop二者都是時序邏輯,所以輸出不但同當前的輸入相關還同上一時間的輸出相關。

1、latch由電平觸發,非同步控制。在使能信號有效時latch相當于通路,在使能信號無效時latch保持輸出狀態。DFF由時鐘沿觸發,同步控制。

2、latch對輸入電平敏感,受布線延遲影響較大,很難保證輸出沒有毛刺產生;DFF則不易產生毛刺。

3、如果使用門電路來搭建latch和DFF,則latch消耗的門資源比DFF要少,這是latch比DFF優越的地方。所以,在ASIC中使用 latch的集成度比DFF高,但在FPGA中正好相反,因為FPGA中沒有標準的latch單元,但有DFF單元,一個LATCH需要多個LE才能實現。latch是電平觸發,相當于有一個使能端,且在激活之后(在使能電平的時候)相當于導線了,隨輸出而變化。在非使能狀態下是保持原來的信號,這就可以看出和flip-flop的差別,其實很多時候latch是不能代替ff的。

4、latch將靜態時序分析變得極為復雜。

5、目前latch只在極高端的電路中使用,如intel 的P4等CPU。 FPGA中有latch單元,寄存器單元就可以配置成latch單元,在xilinx v2p的手冊將該單元配置成為register/latch單元,附件是xilinx半個slice的結構圖。其它型號和廠家的FPGA沒有去查證。——個人認為xilinx是能直接配的而altera或許比較麻煩,要幾個LE才行,然而也非xilinx的器件每個slice都可以這樣配置,altera的只有DDR接口中有專門的latch單元,一般也只有高速電路中會采用latch的設計。altera的LE是沒有latch的結構的,又查了sp3和sp2e,別的不查了,手冊上說支持這種配置。有關altera的表述wangdian說的對,altera的ff不能配置成latch,它使用查找表來實現latch。

一般的設計規則是:在絕大多數設計中避免產生latch。它會讓您設計的時序完蛋,并且它的隱蔽性很強,非老手不能查出。latch最大的危害在于不能過濾毛刺。這對于下一級電路是極其危險的。所以,只要能用D觸發器的地方,就不用latch。

有些地方沒有時鐘,也只能用latch了。比如現在用一個clk接到latch的使能端(假設是高電平使能),這樣需要的setup時間,就是數據在時鐘的下降沿之前需要的時間,但是如果是一個DFF,那么setup時間就是在時鐘的上升沿需要的時間。這就說明如果數據晚于控制信號的情況下,只能用latch,這種情況就是,前面所提到的latch timing borrow。基本上相當于借了一個高電平時間。也就是說,latch借的時間也是有限的。

在if語句和case不全很容易產生latch,需要注意。VIA題目這兩個代碼哪個綜合更容易產生latch: 代碼1

always@(enable or ina or inb)

begin

begin

data_out = ina;

end

else

begin

data_out = inb;

end

end

代碼2

input[3:0] data_in;

always@(data_in)

begin

case(data_in)

0 : out1 = 1‘b1;

1,3 : out2 = 1’b1;

2,4,5,6,7 : out3 = 1‘b1;

default: out4 = 1’b1;

endcase

end

答案是代碼2在綜合時更容易產生latch。

對latch進行STA的分析其實也是可以,但是要對工具相當熟悉才行,不過很容易出錯。當前PrimeTime是支持進行latch分析的,現在一些綜合工具內置的STA分析功能也支持,比如RTL compiler, Design Compiler。除了ASIC里可以節省資源以外,latch在同步設計里出現的可能還是挺小的,現在處理過程中大都放在ff里打一下。

鎖存器電平觸發會把輸入端的毛刺帶入輸出;而觸發器由于邊沿作用可以有效抑制輸入端干擾。

在 CMOS 芯片內部經常使用鎖存器, 但是在PCB板級結構上, 建議用觸發器在時鐘邊沿上鎖存數據。這是因為在鎖存器閘門開啟期間數據的變化會直接反映到輸出端, 所以要注意控制閘門信號的脈沖寬度,而對于觸發器,只考慮時鐘的邊沿。

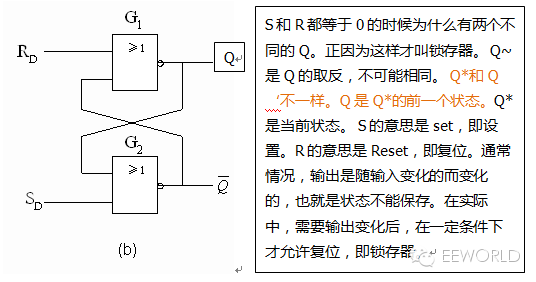

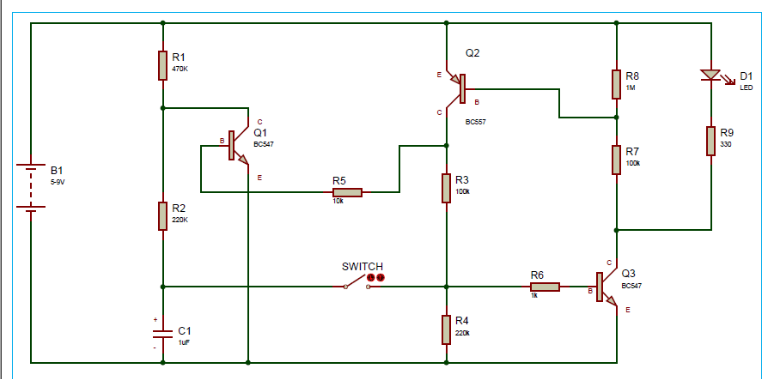

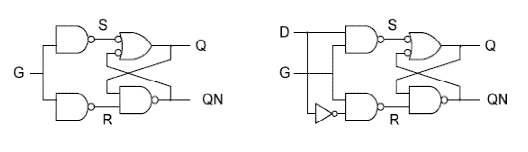

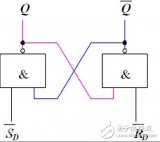

門電路是構建組合邏輯電路的基礎,而鎖存器和觸發器是構建時序邏輯電路的基礎。門電路是由晶體管構成的,鎖存器是由門電路構成的,而觸發器是由鎖存器構成的。也就是晶體管-》門電路-》鎖存器-》觸發器,前一級是后一級的基礎。鎖存器和觸發器它們的輸出都不僅僅取決于目前的輸入,而且和之前的輸入和輸出都有關系。

它們之間的不同在于:鎖存器沒有時鐘信號,而觸發器常常有時鐘觸發信號。 鎖存器是異步的,就是說在輸入信號改變后,輸出信號也隨之很快做出改變非常快。而另外一方面,今天許多計算機是同步的,這就意味著所有的時序電路的輸出信號隨著全局的時鐘信號同時做出改變。觸發器是一個同步版鎖存器。 觸發器泛指一類電路結構,它可以由觸發信號 (如: 時鐘、置位、復位等) 改變輸出狀態, 并保持這個狀態直到下一個或另一個觸發信號來到時。觸發信號可以用電平或邊沿操作,鎖存器是觸發器的一種應用類型。

寄存器與鎖存器的功能是提供數據寄存和鎖存。

寄存功能是指把數據暫時保存,需要時取出。鎖存功能是指總線電路中,鎖定數據輸出,使輸出端不隨輸入端變化。

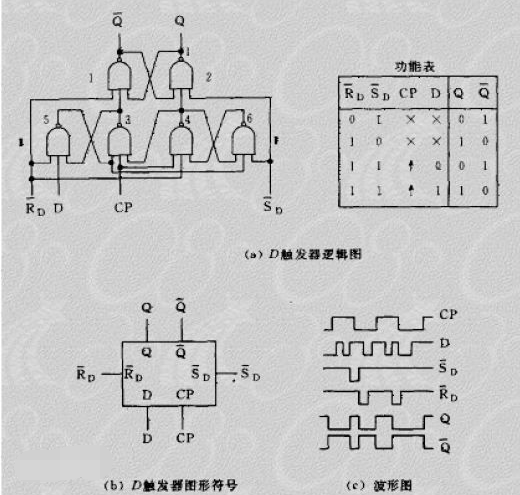

D觸發器和D鎖存器的區別

鐘控D觸發器其實就是D鎖存器,邊沿D觸發器才是真正的D觸發器,鐘控D觸發器在使能情況下輸出隨輸入變化,邊沿觸發器只有在邊沿跳變的情況下輸出才變化。

兩個鎖存器可以構成一個觸發器,歸根到底還是dff是邊沿觸發的,而latch是電平觸發的。鎖存器的輸出對輸入透明的,輸入是什么,輸出就是什么,這就是鎖存器不穩定的原因,而觸發器是由兩個鎖存器構成的一個主從觸發器,輸出對輸入是不透明的,必須在時鐘的上升/下降沿才會將輸入體現到輸出,所以能夠消除輸入的毛刺信號。

?

電子發燒友App

電子發燒友App

評論