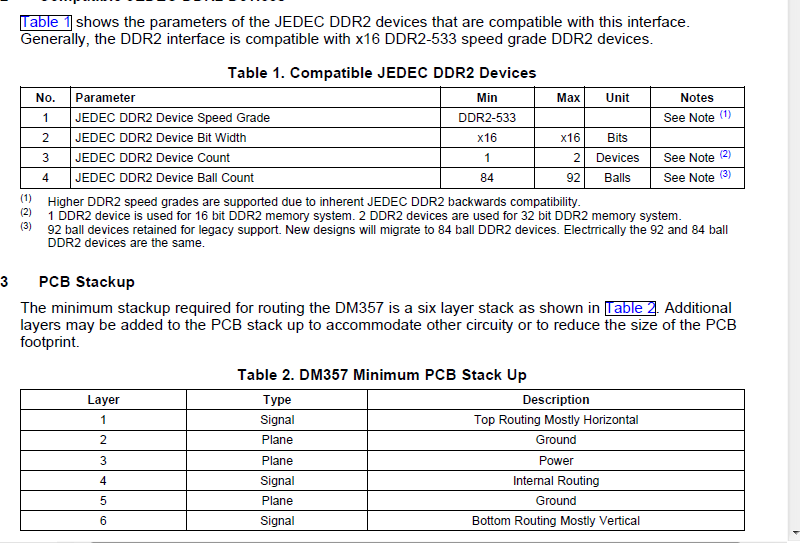

01

**概述**

串?dāng)_:即兩條信號(hào)線(xiàn)之間的耦合引起的線(xiàn)上噪聲干擾。之前的文章咱們說(shuō)過(guò),傳輸線(xiàn)可以等效為一段段RLC模型。走線(xiàn)上存在電感,當(dāng)走線(xiàn)上流過(guò)電流,就會(huì)產(chǎn)生磁場(chǎng),磁場(chǎng)在臨近導(dǎo)體耦合,又會(huì)產(chǎn)生感應(yīng)電動(dòng)勢(shì),從而產(chǎn)生感應(yīng)電流。另外,兩導(dǎo)體間還會(huì)形成等效電容,當(dāng)電壓變化時(shí)就會(huì)有電流耦合到臨近導(dǎo)體。

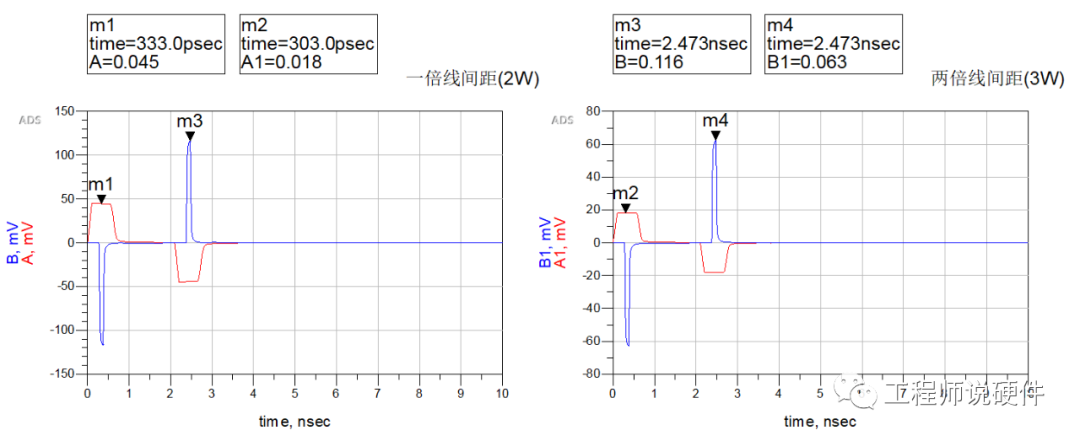

為了降低串?dāng)_帶來(lái)的影響,走線(xiàn)上通常要滿(mǎn)足3W原則,即兩根平行走線(xiàn)中心間距保持3倍線(xiàn)寬(一般要求串?dāng)_值在信號(hào)的5%以?xún)?nèi))。

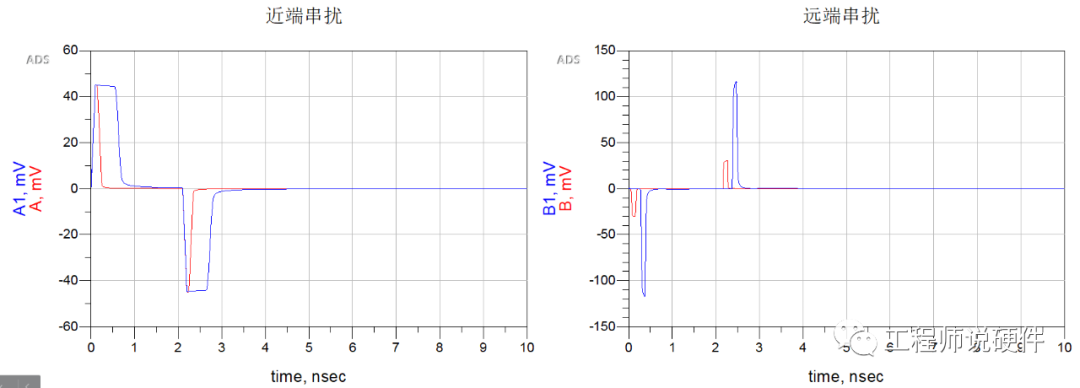

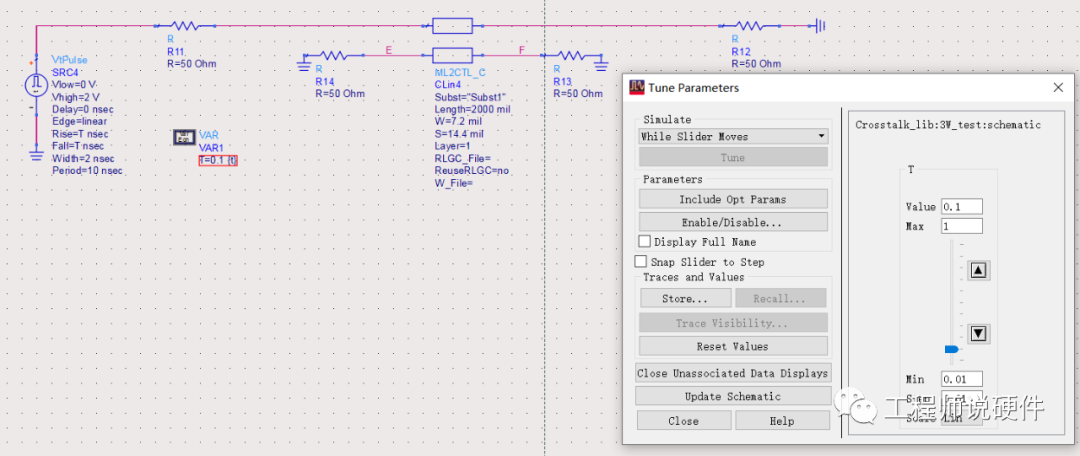

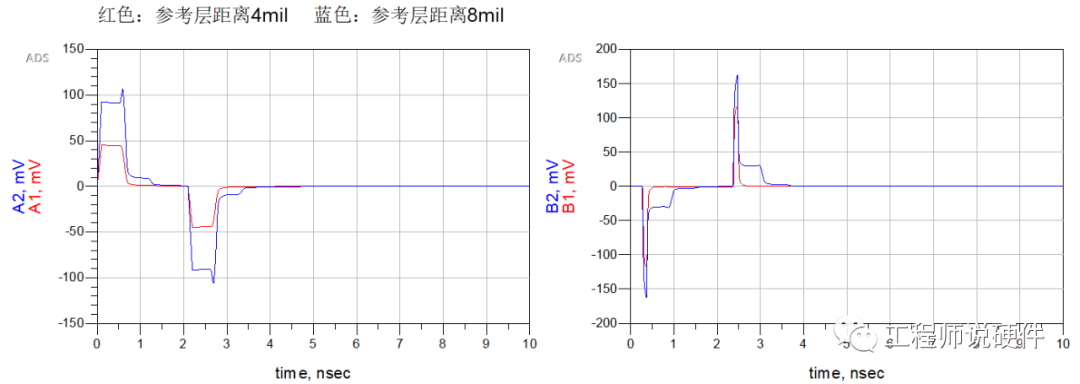

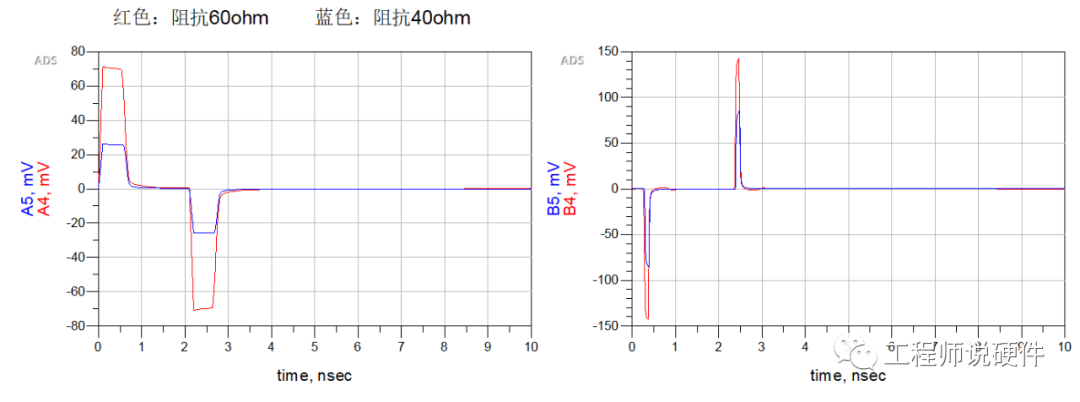

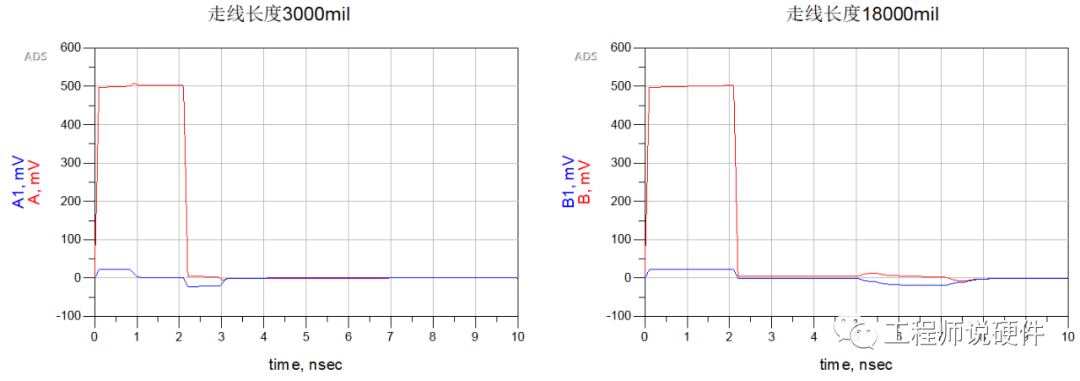

首先通過(guò)如下這個(gè)實(shí)驗(yàn),帶大家直觀地認(rèn)識(shí)串?dāng)_:

圖1、2 ADS仿真:串?dāng)_--3W線(xiàn)距驗(yàn)證

02

**串?dāng)_影響因素**

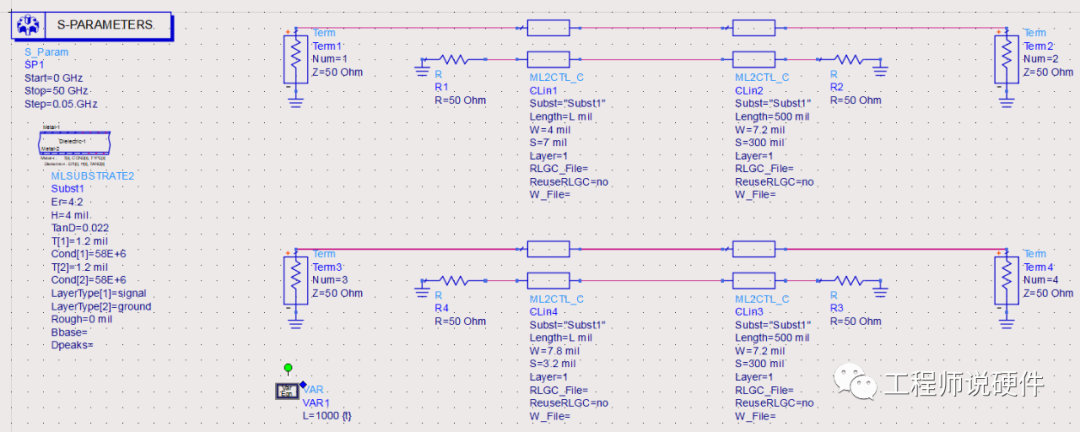

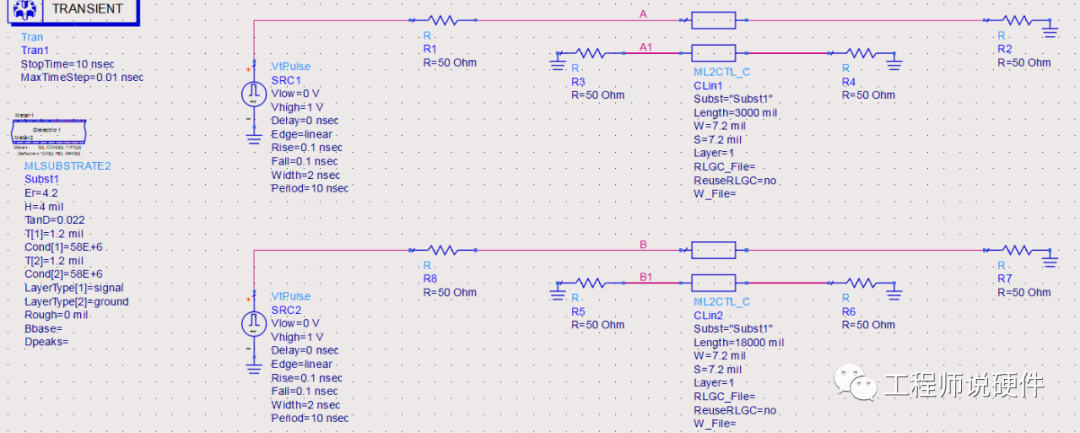

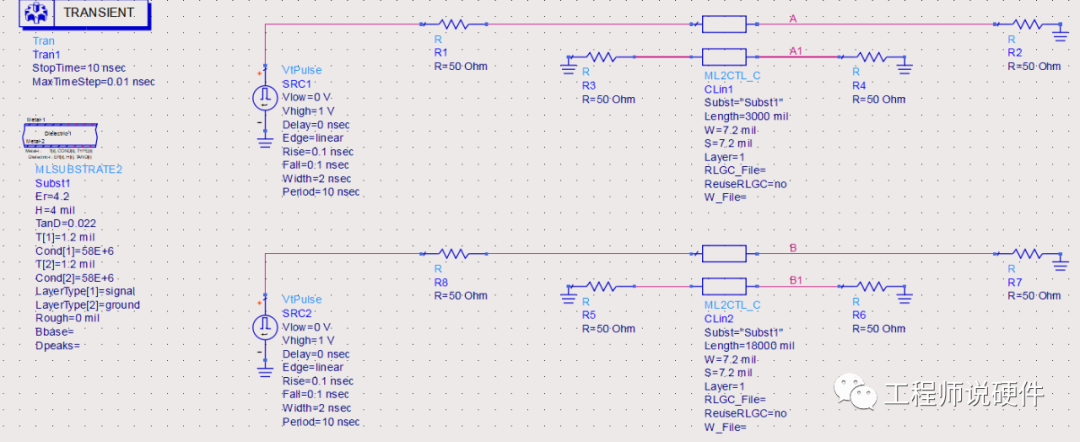

影響串?dāng)_的因素有平行走線(xiàn)長(zhǎng)度、邊沿時(shí)間、介質(zhì)、線(xiàn)間距、阻抗和反射等,下面將通過(guò)一列仿真實(shí)驗(yàn)直觀地介紹其影響。

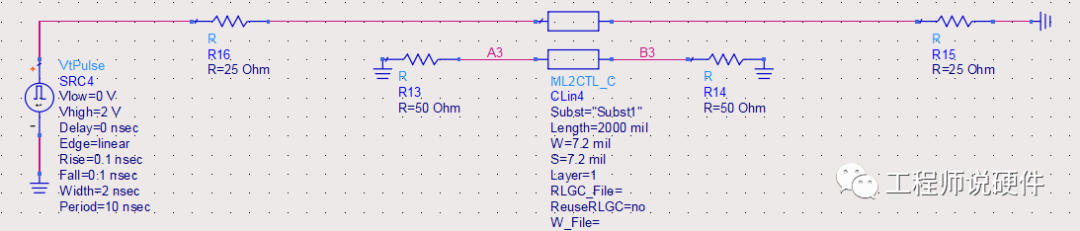

(1)對(duì)于有較長(zhǎng)平行走線(xiàn)的區(qū)域,如果反射與串?dāng)_不能兼顧時(shí),優(yōu)先考慮串?dāng)_的影響。相同走線(xiàn)長(zhǎng)度下,串?dāng)_帶來(lái)的插損影響要比阻抗不匹配大的多。

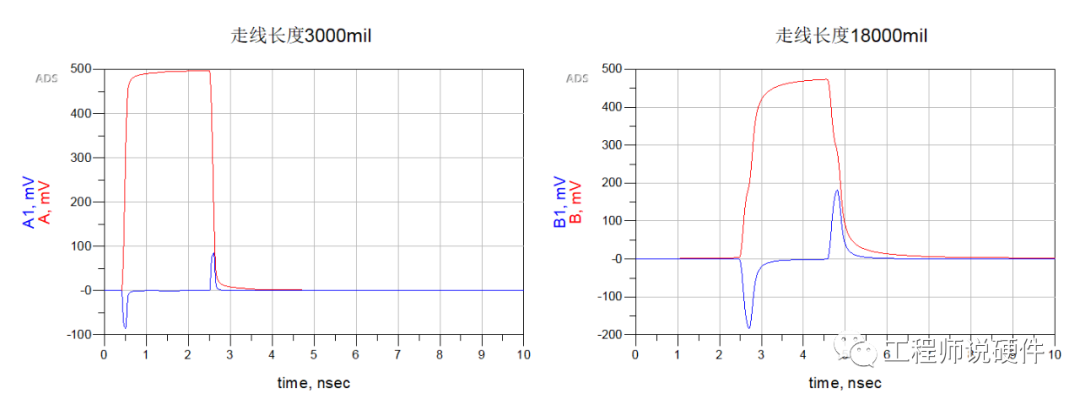

圖3、4 ADS仿真:串?dāng)_和反射的影響對(duì)比

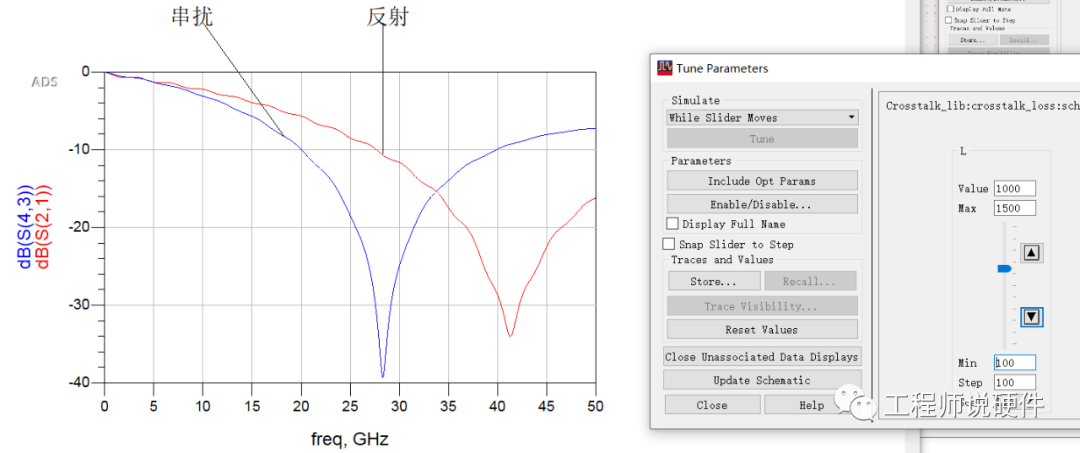

(2)在串?dāng)_到達(dá)飽和之前,增加平行走線(xiàn)長(zhǎng)度會(huì)導(dǎo)致遠(yuǎn)端串?dāng)_幅度增加。

圖5、6 ADS仿真:不同長(zhǎng)度平行走線(xiàn)下的串?dāng)_幅度對(duì)比(2W線(xiàn)寬)

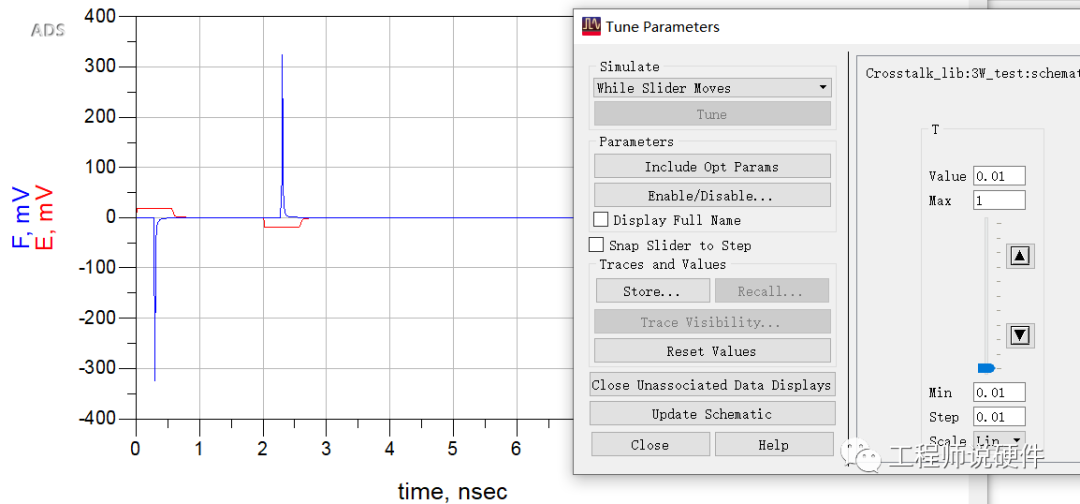

(3)邊沿越陡,串?dāng)_幅度越大。

圖7、8 ADS仿真:信號(hào)邊沿對(duì)串?dāng)_幅度的影響

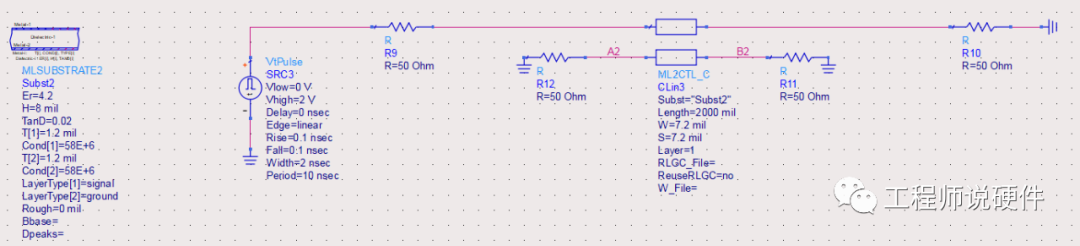

(4)信號(hào)層距離參考層越近,傳輸線(xiàn)和參考層耦合越緊密,臨近線(xiàn)串?dāng)_越小。

圖9、10 ADS仿真:到參考層的距離不同對(duì)串?dāng)_的影響

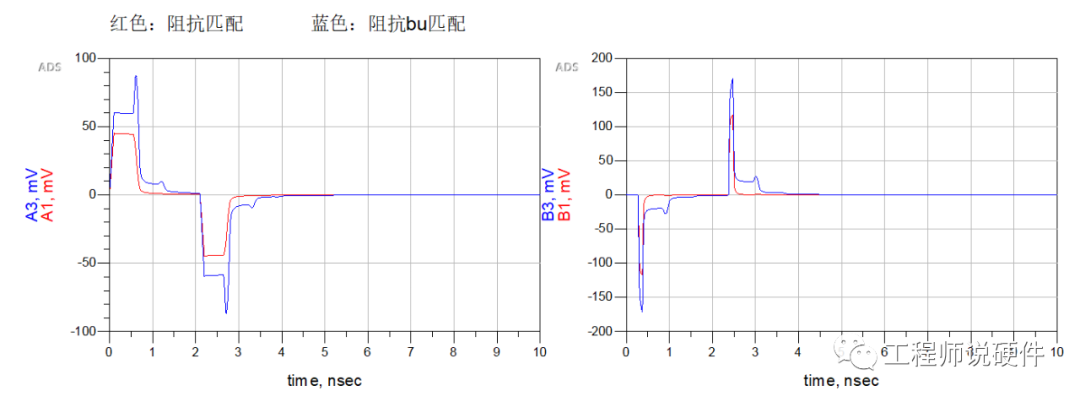

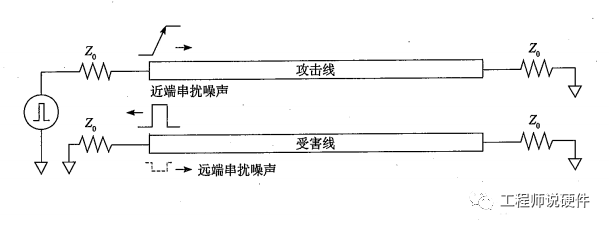

(5)如果線(xiàn)路中存在反射,反射的信號(hào)也會(huì)引起串?dāng)_。因此我們需要保證信號(hào)線(xiàn)阻抗的連續(xù)性,避免多次反射造成串?dāng)_的疊加。

圖11、12 ADS仿真:阻抗不匹配增加串?dāng)_的影響

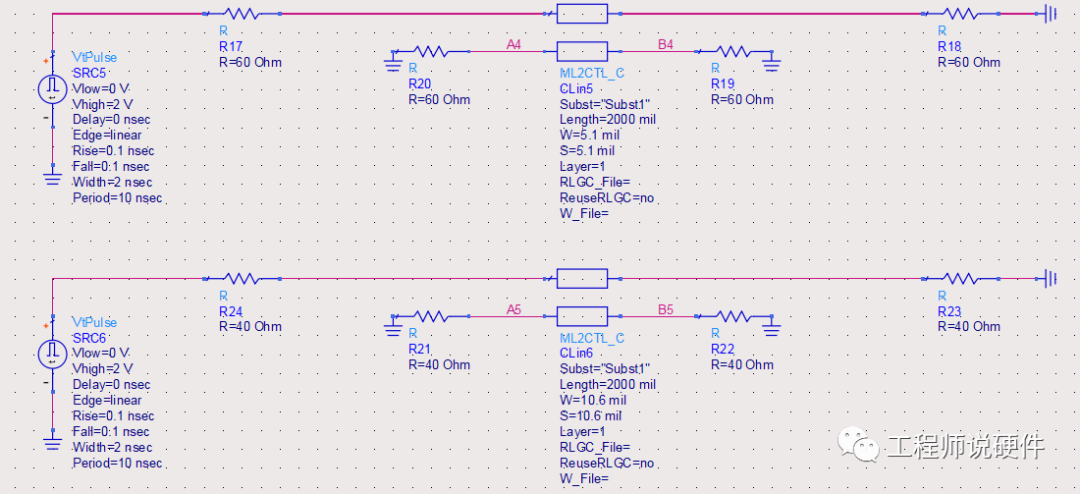

(6)兩根平行走線(xiàn)阻抗越小,串?dāng)_也越小。

圖13、14 ADS仿真:走線(xiàn)阻抗對(duì)串?dāng)_的影響

(8)信號(hào)線(xiàn)間距越大,串?dāng)_越小。概述中已演示案例,此處不在贅述仿真實(shí)驗(yàn)了。

03

**近端串?dāng)_和遠(yuǎn)端串?dāng)_**

串?dāng)_值測(cè)量通常在受害線(xiàn)的兩端,靠近源端的為近端(后向串?dāng)_),反之為遠(yuǎn)端(前向串?dāng)_)。

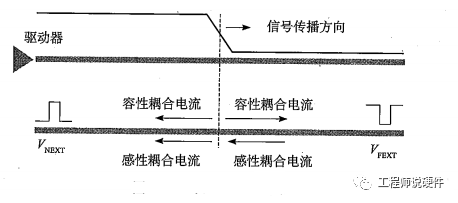

容性耦合的能量會(huì)向遠(yuǎn)端與近端傳輸,感性耦合則只朝著信號(hào)相反方向流動(dòng)。因此,近端串?dāng)_的能量為容性與感性耦合之和(Ic+IL),而遠(yuǎn)端串?dāng)_則為容性與感性耦合之差(Ic-IL)。如下為近端和遠(yuǎn)端串?dāng)_的示意圖。

圖15、16 近端和遠(yuǎn)端串?dāng)_示意圖

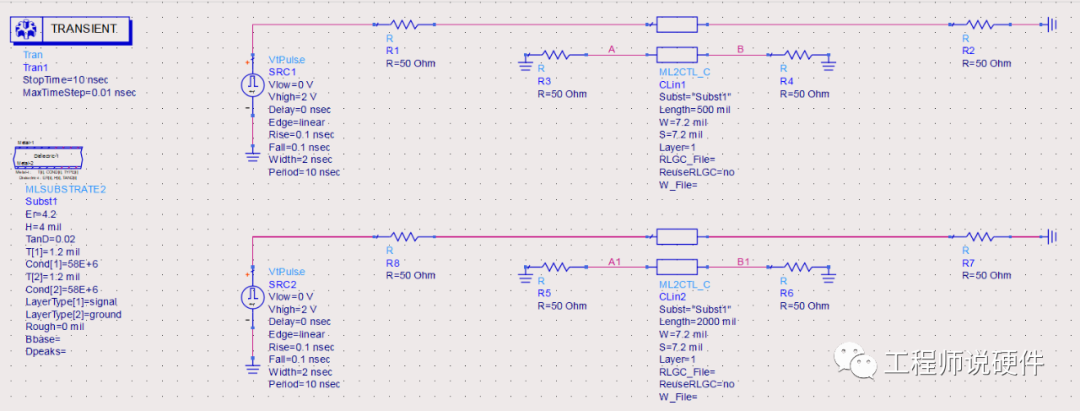

(1)信號(hào)在向前傳播的時(shí)候,近端串?dāng)_持續(xù)產(chǎn)生,方向跳變沿相同,幅度穩(wěn)定后不變,波形寬度逐漸增加。

圖17、18 ADS仿真:不同走線(xiàn)長(zhǎng)度的近端串?dāng)_

(2)遠(yuǎn)端串?dāng)_隨著信號(hào)向前傳播,不斷疊加,幅度逐漸增強(qiáng)(不會(huì)無(wú)限制增加,有飽和點(diǎn))。遠(yuǎn)端串?dāng)_的波形寬度等于信號(hào)邊沿時(shí)間。

圖19、20 ADS仿真:不同走線(xiàn)長(zhǎng)度的遠(yuǎn)端串?dāng)_

審核編輯:劉清

-

信號(hào)完整性

+關(guān)注

關(guān)注

68文章

1443瀏覽量

96690 -

耦合器

+關(guān)注

關(guān)注

8文章

735瀏覽量

60983 -

ADS仿真

+關(guān)注

關(guān)注

1文章

71瀏覽量

10847 -

RLC

+關(guān)注

關(guān)注

1文章

116瀏覽量

39642

原文標(biāo)題:信號(hào)完整性基礎(chǔ)--串?dāng)_(一)[20230706]

文章出處:【微信號(hào):EMC_EMI,微信公眾號(hào):電磁兼容EMC】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

常見(jiàn)信號(hào)完整性的問(wèn)題之PCB設(shè)計(jì)串擾的原因與Altium Designer中的串擾消除技術(shù)

信號(hào)完整性-串擾的模型

高速電路信號(hào)完整性分析與設(shè)計(jì)—串擾

【連載筆記】信號(hào)完整性-串擾和軌道塌陷

基于Protel 99的PCB信號(hào)完整性分析設(shè)計(jì)

高速電路信號(hào)完整性分析與設(shè)計(jì)—串擾

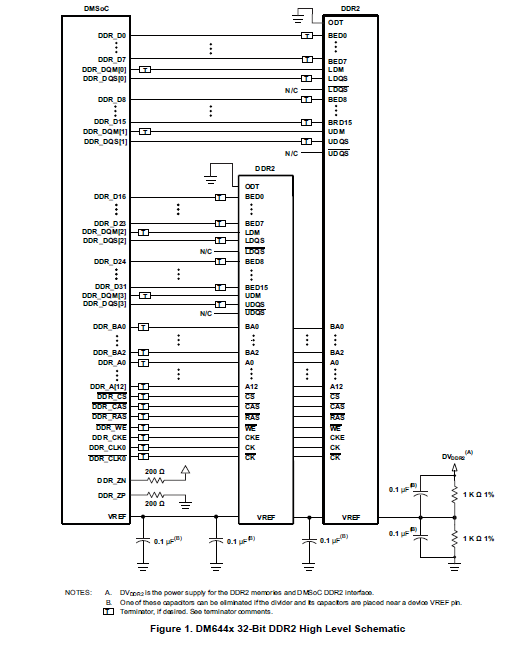

如何實(shí)現(xiàn)TMS320DM644x數(shù)字媒體系統(tǒng)芯片DMSo實(shí)施DDR2PCB布局

如何實(shí)現(xiàn)在TMS320DM357數(shù)字媒體系統(tǒng)芯片DMS實(shí)施DDR2PCB布局

PCB設(shè)計(jì)信號(hào)完整性與串擾問(wèn)題分析

信號(hào)完整性基礎(chǔ)-串?dāng)_

信號(hào)完整性基礎(chǔ)-串?dāng)_

評(píng)論