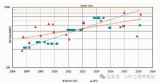

電子發(fā)燒友網(wǎng)報(bào)道(文/吳子鵬)先進(jìn)封裝包括倒裝焊、2.5D封裝、3D封裝、晶圓級(jí)封裝、Chiplet等,過(guò)去幾年我國(guó)先進(jìn)封裝產(chǎn)業(yè)發(fā)展迅猛。根據(jù)中國(guó)半導(dǎo)體協(xié)會(huì)的統(tǒng)計(jì)數(shù)據(jù),2023年我國(guó)先進(jìn)封裝市場(chǎng)規(guī)模達(dá)1330億元,2020年-2023年期間的年復(fù)合增長(zhǎng)率高達(dá)14%。不過(guò),目前國(guó)內(nèi)先進(jìn)封裝市場(chǎng)占比僅為39.0%,與全球先進(jìn)封裝市場(chǎng)占比48.8%相比仍有較大差距,尚有較大提升空間。

受益于AI產(chǎn)業(yè)大發(fā)展,目前全球先進(jìn)封裝產(chǎn)能吃緊。隨著AI、自動(dòng)駕駛等應(yīng)用對(duì)芯片性能要求越來(lái)越高,后續(xù)全球和中國(guó)先進(jìn)封裝產(chǎn)業(yè)仍有巨大的發(fā)展空間。在以“共筑先進(jìn)封裝新生態(tài),引領(lǐng)路徑創(chuàng)新大發(fā)展”為主題的第十六屆集成電路封測(cè)產(chǎn)業(yè)鏈創(chuàng)新發(fā)展論壇(CIPA 2024)上,專設(shè)“芯片設(shè)計(jì)與先進(jìn)封裝技術(shù)專題論壇”,探討先進(jìn)封裝的技術(shù)發(fā)展,以及先進(jìn)封裝如何賦能復(fù)雜SoC設(shè)計(jì)等產(chǎn)業(yè)前沿問(wèn)題。

Chiplet技術(shù)創(chuàng)新的挑戰(zhàn)

Chiplet是先進(jìn)封裝重要組成部分,通常被翻譯為“芯粒”或“小芯片”,憑借高性能、低功耗、高面積使用率等優(yōu)勢(shì),Chiplet被認(rèn)為是延續(xù)摩爾定律“經(jīng)濟(jì)效益”的有效手段。

芯和半導(dǎo)體聯(lián)合創(chuàng)始人&總裁代文亮博士指出,Chiplet讓復(fù)雜SoC的創(chuàng)新速度明顯加快。過(guò)往,傳統(tǒng)SoC的迭代速度是18-24個(gè)月。在Chiplet技術(shù)的幫助下,科技巨頭和芯片巨頭每3個(gè)月,或者是每半年就會(huì)發(fā)布一款新品,創(chuàng)新速度明顯提升。更為重要的是,Chiplet讓算法的支持更加高效靈活,不需要全部推倒重來(lái)設(shè)計(jì)芯片,只需要替換其中的計(jì)算單元即可,顯著提升了芯片創(chuàng)新對(duì)算法支持的普適性。

芯和半導(dǎo)體聯(lián)合創(chuàng)始人&總裁代文亮博士

當(dāng)然,作為芯片創(chuàng)新的革命性技術(shù),Chiplet技術(shù)發(fā)展也面臨著一些挑戰(zhàn),比如Chiplet在晶圓管理方面提升了連接復(fù)雜性、時(shí)間敏感性;管理多顆芯粒的規(guī)格可能給芯片良率帶來(lái)一定的挑戰(zhàn);Chiplet在芯片制造方面的成本還需要得到優(yōu)化等。

對(duì)此,代文亮博士特別提到了Chiplet設(shè)計(jì)的復(fù)雜性,涉及可行性、可優(yōu)化性、可實(shí)現(xiàn)性等問(wèn)題。他認(rèn)為,Chiplet后期的發(fā)展模式Chiplet Store,滿足連接標(biāo)準(zhǔn)的Chiplet都可以參與到復(fù)雜SoC創(chuàng)新中。以MCU廠商為例,原本MCU并不需要做大規(guī)模的復(fù)雜SoC,但是MCU是復(fù)雜SoC里重要的一部分,因此相關(guān)廠商可以將MCU打造成為滿足連接標(biāo)準(zhǔn)的Chiplet。因此,對(duì)于Chiplet發(fā)展來(lái)說(shuō),生態(tài)系統(tǒng)是非常重要的,EDA、Fabless、IDM、晶圓代工廠要高效溝通,這也是芯和半導(dǎo)體打造Chiplet先進(jìn)封裝平臺(tái)的主要原因。

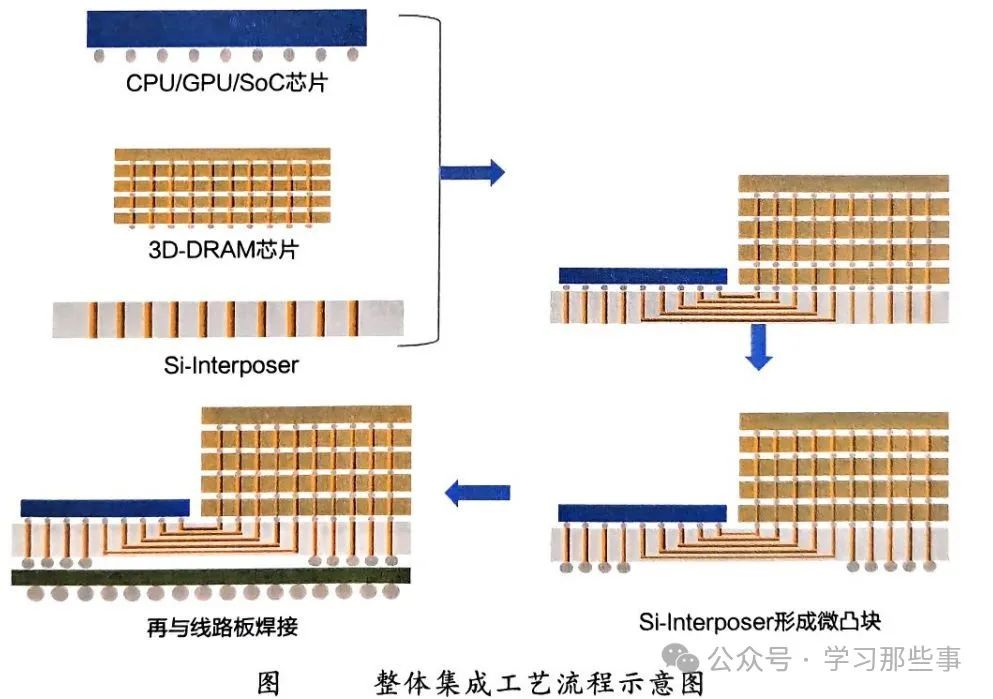

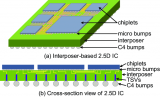

進(jìn)一步來(lái)看,要想高效利用Chiplet,離不開(kāi)先進(jìn)封裝技術(shù)。Chiplet讓芯片可分解成特定模塊,按封裝介質(zhì)材料和封裝工藝劃分,Chiplet的實(shí)現(xiàn)方式主要包括以下幾種:MCM、2.5D封裝、3D封裝。蘇州通富超威半導(dǎo)體有限公司封裝開(kāi)發(fā)經(jīng)理何志丹表示,無(wú)論是何種先進(jìn)封裝形式,要做的就是通過(guò)基板將Chiplet轉(zhuǎn)移到PCB板上。目前,Chiplet是“以大為美”,封裝尺寸越做越大,那么一個(gè)明顯的問(wèn)題就是翹曲。

蘇州通富超威半導(dǎo)體有限公司封裝開(kāi)發(fā)經(jīng)理何志丹

傳統(tǒng)貼片機(jī)和回流焊的方式,翹曲只有10微米左右,挑戰(zhàn)和影響并不大。在容納Chiplet的大封裝里,翹曲會(huì)達(dá)到150-200微米,因此傳統(tǒng)的封裝形式已經(jīng)不適用于Chiplet。何志丹指出,目前新產(chǎn)品的基板層數(shù)達(dá)到20層,甚至?xí)_(dá)到26-28層,這也就意味著翹曲將會(huì)出現(xiàn)更加嚴(yán)重的問(wèn)題,給引線焊接帶來(lái)了更大的挑戰(zhàn)。應(yīng)對(duì)翹曲,玻璃基板是一個(gè)非常好的方式,但玻璃基板依然在探索階段。

大尺寸封裝帶來(lái)的第二個(gè)問(wèn)題是散熱。先進(jìn)封裝芯片在能滿足高性能計(jì)算、人工智能、功率密度增長(zhǎng)需求的同時(shí),散熱問(wèn)題也變得更加復(fù)雜。因此,解決芯片封裝散熱問(wèn)題是一項(xiàng)至關(guān)重要的任務(wù)。何志丹提到,今天我們聽(tīng)到芯片的功耗,很多是600W、800W,功耗是非常高的。將芯片做薄,提升銅層覆蓋率是一個(gè)好的散熱解決方案。但更大更薄的芯片就會(huì)產(chǎn)生更嚴(yán)重的翹曲,更加不利于焊接。通富超威半導(dǎo)體在解決散熱方面的一個(gè)解決方案是在TIM材料上采用面積大、熱度小的材料。

先進(jìn)封裝賦能大算力芯片創(chuàng)新

賦能高性能計(jì)算是先進(jìn)封裝技術(shù)發(fā)展的主要推動(dòng)力,反過(guò)來(lái)說(shuō),先進(jìn)封裝是打造大算力芯片的重要手段。天芯互聯(lián)產(chǎn)品總監(jiān)張偉杰表示,當(dāng)前算力每12個(gè)月翻一倍,算力高能效是非常重要的,需要先進(jìn)封裝實(shí)現(xiàn)高集成、高密度,并要求供電模塊實(shí)現(xiàn)小型化。

天芯互聯(lián)產(chǎn)品總監(jiān)張偉杰

在先進(jìn)封裝方面,2.5D/3D封裝是產(chǎn)業(yè)后續(xù)發(fā)展的方向,板級(jí)扇出也能提升系統(tǒng)性能。天芯互聯(lián)目前正在做這方面的工作,比如該公司在先進(jìn)封裝與系統(tǒng)集成解決方案方面提供工藝流程、仿真服務(wù)、封裝仿真等服務(wù)。張偉杰以一款5nm芯片為例,基于天芯互聯(lián)的方案,在5500×4800um的Wafer上實(shí)現(xiàn)4顆AI計(jì)算die的互聯(lián),打造多核架構(gòu),能夠減少Fan-out信號(hào)數(shù)量,降低基板難度。

基于Chiplet和先進(jìn)封裝技術(shù)的大算力芯片,一個(gè)重要的特性是異構(gòu)集成,因此電源網(wǎng)絡(luò)會(huì)越來(lái)越復(fù)雜,如何優(yōu)化電源也是重要一環(huán)。張偉杰稱,從數(shù)據(jù)中心的電源架構(gòu)來(lái)看,從380V交流轉(zhuǎn)換到220V和直流,然后再轉(zhuǎn)換到48V供電。同時(shí),在新的供電架構(gòu)下,48V依然會(huì)轉(zhuǎn)化為0.8V或者是1.2V,要保證效率,電流就會(huì)非常大,對(duì)于電源模塊的散熱和通用能力有更高的要求。天芯互聯(lián)能夠依托晶圓級(jí)封裝(WLP)、系統(tǒng)級(jí)封裝(SiP)和板級(jí)扇出封裝(FOPLP)平臺(tái)提供領(lǐng)先的電源系統(tǒng)方案。比如在板級(jí)扇出封裝(FOPLP)平臺(tái)里,天芯互聯(lián)把GaN、控制芯片和電感合封,不僅效率更高、體積更小,而且還可以實(shí)現(xiàn)共同散熱。

在高性能計(jì)算芯片方面,最典型的例子是GPGPU。當(dāng)前,GPGPU依然是AI訓(xùn)練任務(wù)的基石。根據(jù)Verified Market Research預(yù)測(cè),2028年全球GPU市場(chǎng)規(guī)模將達(dá)到2465.1億美元,主要應(yīng)用領(lǐng)域包括AI、數(shù)據(jù)中心和智能汽車等。蕪湖立德智興半導(dǎo)體有限公司CTO李元雄專門(mén)分析了萬(wàn)億晶體管級(jí)的GPU芯片如何通過(guò)先進(jìn)封裝技術(shù)來(lái)實(shí)現(xiàn)。

蕪湖立德智興半導(dǎo)體有限公司CTO李元雄

李元雄指出,萬(wàn)億晶體管規(guī)模的GPU的實(shí)現(xiàn)方式就是橫向擴(kuò)展和堆疊。在堆疊方面,英特爾公司采用的是3D封裝技術(shù)Foveros,可以在處理器制造過(guò)程中以垂直方式堆疊計(jì)算模塊,而不是傳統(tǒng)的水平方式。臺(tái)積電則采用了SoIC(系統(tǒng)級(jí)集成單芯片),能夠在創(chuàng)造鍵合界面讓計(jì)算模塊可以直接堆疊在芯片上。封裝技術(shù)主要指標(biāo)為凸點(diǎn)間距,凸點(diǎn)間距越小,封裝集成度越高、難度越大。臺(tái)積電的3D SoIC的凸點(diǎn)間距最小可達(dá)6um,居于所有封裝技術(shù)首位。為了實(shí)現(xiàn)這種堆疊,還需要配套的連接技術(shù),比如臺(tái)積電使用的高密度硅通孔(TSV),和高精度納米級(jí)的混合鍵合(Hybrid bonding)。

在橫向拓展上主要手段有扇出型晶圓級(jí)封裝工藝等,需要重構(gòu)晶圓,挑戰(zhàn)在于保證重構(gòu)晶圓達(dá)到一定的精度。立德智興提供了一款關(guān)鍵設(shè)備,不僅提升了重構(gòu)晶圓的精度,還提供自動(dòng)光學(xué)檢測(cè),來(lái)提升芯片的可靠性。

結(jié)語(yǔ)

先進(jìn)封裝是當(dāng)前和未來(lái)芯片產(chǎn)業(yè)發(fā)展的重點(diǎn),是打造高性能計(jì)算芯片的主要手段。當(dāng)然,無(wú)論是Chiplet,還是2.5D/3D封裝,都有一些額外的挑戰(zhàn),比如大封裝的翹曲和散熱,異構(gòu)集成的供電等問(wèn)題。產(chǎn)業(yè)界依然在探索如何用更好的方式實(shí)現(xiàn)先進(jìn)封裝,這也需要制造和封裝巨頭起到更好的引導(dǎo)作用,先進(jìn)封裝需要標(biāo)準(zhǔn)引領(lǐng)。

-

soc

+關(guān)注

關(guān)注

38文章

4358瀏覽量

222009 -

AI

+關(guān)注

關(guān)注

88文章

34591瀏覽量

276289 -

chiplet

+關(guān)注

關(guān)注

6文章

453瀏覽量

12914 -

先進(jìn)封裝

+關(guān)注

關(guān)注

2文章

465瀏覽量

549 -

2.5D封裝

+關(guān)注

關(guān)注

0文章

24瀏覽量

324

發(fā)布評(píng)論請(qǐng)先 登錄

2.5D/3D封裝技術(shù)升級(jí),拉高AI芯片性能天花板

多芯粒2.5D/3D集成技術(shù)研究現(xiàn)狀

Chiplet與先進(jìn)封裝設(shè)計(jì)中EDA工具面臨的挑戰(zhàn)

2.5D封裝為何成為AI芯片的“寵兒”?

先進(jìn)封裝技術(shù):3.5D封裝、AMD、AI訓(xùn)練降本

2.5D集成電路的Chiplet布局設(shè)計(jì)

一文詳解2.5D封裝工藝

最全對(duì)比!2.5D vs 3D封裝技術(shù)

技術(shù)資訊 | 2.5D 與 3D 封裝

高帶寬Chiplet互連的技術(shù)、挑戰(zhàn)與解決方案

2.5D封裝的熱力挑戰(zhàn)

深入剖析2.5D封裝技術(shù)優(yōu)勢(shì)及應(yīng)用

一文理解2.5D和3D封裝技術(shù)

AI應(yīng)用致復(fù)雜SoC需求暴漲,2.5D/Chiplet等先進(jìn)封裝技術(shù)的機(jī)遇和挑戰(zhàn)

AI應(yīng)用致復(fù)雜SoC需求暴漲,2.5D/Chiplet等先進(jìn)封裝技術(shù)的機(jī)遇和挑戰(zhàn)

評(píng)論