一、引言

隨著半導(dǎo)體技術(shù)的不斷發(fā)展,芯片粘接工藝作為微電子封裝技術(shù)中的關(guān)鍵環(huán)節(jié),對(duì)于確保芯片與外部電路的穩(wěn)定連接、提升封裝產(chǎn)品的可靠性和性能具有至關(guān)重要的作用。芯片粘接工藝涉及多種技術(shù)和材料,其工藝參數(shù)的精確控制對(duì)于保證粘接質(zhì)量至關(guān)重要。本文將對(duì)芯片粘接工藝及其關(guān)鍵工藝參數(shù)進(jìn)行詳細(xì)介紹。

二、芯片粘接工藝概述

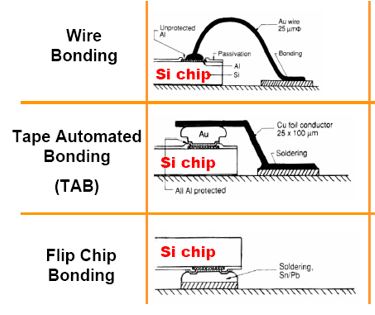

芯片粘接工藝,又稱芯片貼裝、芯片鍵合或芯片覆貼,是將切割并挑選好的裸芯片通過(guò)特定工藝固定到框架或基板上,以實(shí)現(xiàn)芯片與外部電路的電連接。該工藝過(guò)程通常包括涂敷粘合劑、定位芯片、施加壓力和固化等步驟。

涂敷粘合劑

- 粘合劑的選擇對(duì)粘接質(zhì)量有著重要影響。常見的粘合材料包括有機(jī)硅、環(huán)氧樹脂、聚苯乙烯等。有機(jī)硅具有良好的電氣絕緣性、機(jī)械性能和熱性能,成本較低,被廣泛應(yīng)用于半導(dǎo)體封裝領(lǐng)域。環(huán)氧樹脂則以其良好的耐高溫和耐化學(xué)性能,在高性能、高可靠性的封裝應(yīng)用中占據(jù)重要地位。

- 涂敷粘合劑的方式多種多樣,如手工涂膠、絲網(wǎng)印刷等。手工涂膠適用于小批量生產(chǎn)和研發(fā)階段,但精度較低;絲網(wǎng)印刷則能實(shí)現(xiàn)高精度、大面積的涂膠,適用于大規(guī)模生產(chǎn)。

定位芯片

- 準(zhǔn)確的芯片定位是粘接成功的基礎(chǔ)。在微米甚至納米級(jí)別的精度上實(shí)現(xiàn)完美對(duì)齊,對(duì)于確保粘接質(zhì)量和芯片性能至關(guān)重要。

- 現(xiàn)代芯片粘接設(shè)備通常采用視覺定位系統(tǒng)或激光對(duì)準(zhǔn)系統(tǒng)來(lái)實(shí)現(xiàn)高精度的芯片定位。視覺定位系統(tǒng)利用高精度攝像頭與圖像處理技術(shù),識(shí)別芯片特征與基板上的標(biāo)記,指導(dǎo)機(jī)械臂或平臺(tái)進(jìn)行精確定位;激光對(duì)準(zhǔn)系統(tǒng)則利用激光光斑作為參照,通過(guò)反射或干涉原理實(shí)現(xiàn)超精密對(duì)準(zhǔn)。

施加壓力

- 施加一定的壓力使芯片與框架或基板的焊接區(qū)域緊密鍵合起來(lái),是芯片粘接工藝中的重要步驟。

- 壓力的大小和施加方式需要根據(jù)粘合劑的類型、芯片的尺寸和形狀以及基板的材質(zhì)等因素進(jìn)行精確控制。過(guò)大或過(guò)小的壓力都可能影響粘接質(zhì)量。

固化

- 固化是使粘合劑形成牢固連接的關(guān)鍵步驟。在固定芯片位置后,需要再次加熱進(jìn)行固化,使粘合劑達(dá)到其最佳性能狀態(tài)。

- 固化的溫度和時(shí)間等參數(shù)需要根據(jù)粘合劑的種類和工藝要求進(jìn)行精確控制。固化溫度過(guò)高或時(shí)間過(guò)長(zhǎng)可能導(dǎo)致粘合劑老化或芯片損壞;固化溫度過(guò)低或時(shí)間過(guò)短則可能導(dǎo)致粘合劑固化不完全,影響粘接質(zhì)量。

三、芯片粘接工藝參數(shù)詳解

芯片粘接工藝參數(shù)的選擇和控制對(duì)于保證粘接質(zhì)量至關(guān)重要。以下將詳細(xì)介紹幾種常見的芯片粘接工藝參數(shù)及其影響因素。

粘合劑的選擇

- 粘合劑的選擇需要考慮芯片的材質(zhì)、基板的材質(zhì)、封裝要求以及生產(chǎn)工藝等多種因素。

- 對(duì)于需要電氣連接的場(chǎng)合,如倒裝芯片封裝,導(dǎo)電膠是一種理想的選擇。導(dǎo)電膠不僅具有良好的機(jī)械強(qiáng)度和電性能,還能實(shí)現(xiàn)芯片與外部電路的穩(wěn)定電連接。

- 對(duì)于不需要電連接的場(chǎng)合,如許多邏輯芯片和存儲(chǔ)芯片的封裝,非導(dǎo)電膠如有機(jī)硅、環(huán)氧樹脂等則更為常用。這些材料具有良好的機(jī)械性能和熱性能,成本較低,且易于加工和使用。

涂膠工藝參數(shù)

- 涂膠工藝參數(shù)主要包括涂膠方式、涂膠量、涂膠速度等。

- 涂膠方式的選擇需要根據(jù)生產(chǎn)規(guī)模和精度要求進(jìn)行確定。手工涂膠適用于小批量生產(chǎn)和研發(fā)階段,但精度較低;絲網(wǎng)印刷則能實(shí)現(xiàn)高精度、大面積的涂膠,適用于大規(guī)模生產(chǎn)。

- 涂膠量的控制對(duì)于保證粘接質(zhì)量至關(guān)重要。涂膠量過(guò)多可能導(dǎo)致膠粘劑溢出到芯片或基板上,影響后續(xù)的焊接工藝;涂膠量過(guò)少則可能導(dǎo)致粘接強(qiáng)度不足,芯片容易脫落。

- 涂膠速度的選擇需要考慮粘合劑的固化速度和生產(chǎn)效率。過(guò)快的涂膠速度可能導(dǎo)致粘合劑分布不均勻,影響粘接質(zhì)量;過(guò)慢的涂膠速度則可能降低生產(chǎn)效率。

定位精度參數(shù)

- 定位精度是芯片粘接工藝中的關(guān)鍵參數(shù)之一。它直接影響芯片與基板之間的對(duì)齊程度和粘接質(zhì)量。

- 現(xiàn)代芯片粘接設(shè)備通常采用視覺定位系統(tǒng)或激光對(duì)準(zhǔn)系統(tǒng)來(lái)實(shí)現(xiàn)高精度的芯片定位。視覺定位系統(tǒng)利用高精度攝像頭與圖像處理技術(shù),識(shí)別芯片特征與基板上的標(biāo)記,指導(dǎo)機(jī)械臂或平臺(tái)進(jìn)行精確定位;激光對(duì)準(zhǔn)系統(tǒng)則利用激光光斑作為參照,通過(guò)反射或干涉原理實(shí)現(xiàn)超精密對(duì)準(zhǔn)。

- 定位精度的要求隨著芯片尺寸的不斷縮小而不斷提高。對(duì)于微米乃至納米級(jí)的芯片,需要采用更先進(jìn)的定位技術(shù)和設(shè)備來(lái)實(shí)現(xiàn)高精度的芯片定位。

壓力參數(shù)

- 壓力是芯片粘接工藝中的重要參數(shù)之一。它直接影響芯片與基板之間的粘接強(qiáng)度和均勻性。

- 壓力的大小和施加方式需要根據(jù)粘合劑的類型、芯片的尺寸和形狀以及基板的材質(zhì)等因素進(jìn)行精確控制。過(guò)大或過(guò)小的壓力都可能影響粘接質(zhì)量。

- 施加壓力的方式有多種,如使用壓合機(jī)、熱壓機(jī)等設(shè)備。這些設(shè)備能夠根據(jù)預(yù)設(shè)的壓力參數(shù)對(duì)芯片進(jìn)行精確的壓力施加,確保粘接質(zhì)量。

固化工藝參數(shù)

- 固化是使粘合劑形成牢固連接的關(guān)鍵步驟。固化工藝參數(shù)的選擇和控制對(duì)于保證粘接質(zhì)量至關(guān)重要。

- 固化的溫度和時(shí)間等參數(shù)需要根據(jù)粘合劑的種類和工藝要求進(jìn)行精確控制。固化溫度過(guò)高或時(shí)間過(guò)長(zhǎng)可能導(dǎo)致粘合劑老化或芯片損壞;固化溫度過(guò)低或時(shí)間過(guò)短則可能導(dǎo)致粘合劑固化不完全,影響粘接質(zhì)量。

- 固化過(guò)程通常在熱氮?dú)獗Wo(hù)的環(huán)境中進(jìn)行,以防止粘合劑在高溫下氧化或產(chǎn)生孔洞等缺陷。同時(shí),還需要對(duì)固化過(guò)程進(jìn)行實(shí)時(shí)監(jiān)控和調(diào)整,以確保固化質(zhì)量和生產(chǎn)效率。

四、芯片粘接工藝的應(yīng)用與挑戰(zhàn)

應(yīng)用

- 芯片粘接工藝在半導(dǎo)體封裝領(lǐng)域具有廣泛的應(yīng)用。無(wú)論是傳統(tǒng)的引線鍵合封裝、倒裝封裝還是新型的晶圓級(jí)扇出封裝等,都需要采用芯片粘接工藝將芯片固定到框架或基板上。

- 隨著半導(dǎo)體技術(shù)的不斷發(fā)展,芯片粘接工藝也在不斷創(chuàng)新和改進(jìn)。例如,采用納米銀燒結(jié)技術(shù)、共晶焊技術(shù)等新型粘接技術(shù),可以實(shí)現(xiàn)更高精度、更高可靠性和更高性能的芯片粘接。

挑戰(zhàn)

- 盡管芯片粘接工藝在半導(dǎo)體封裝領(lǐng)域取得了顯著進(jìn)展,但仍面臨著一些挑戰(zhàn)。

- 首先,芯片尺寸的不斷縮小對(duì)粘接精度和工藝穩(wěn)定性提出了更高的要求。如何實(shí)現(xiàn)微米乃至納米級(jí)的定位精度和粘接強(qiáng)度,是當(dāng)前芯片粘接工藝面臨的重要挑戰(zhàn)之一。

- 其次,隨著芯片功率的不斷提高和封裝密度的不斷增加,芯片粘接工藝還需要考慮熱膨脹系數(shù)不匹配、應(yīng)力集中等問(wèn)題。這些問(wèn)題可能導(dǎo)致芯片在長(zhǎng)期使用過(guò)程中出現(xiàn)開裂、脫落等故障。

- 此外,芯片粘接工藝還需要考慮生產(chǎn)效率、成本控制等因素。如何在保證粘接質(zhì)量的前提下提高生產(chǎn)效率、降低生產(chǎn)成本,是當(dāng)前芯片粘接工藝研究的重要方向之一。

五、結(jié)論

芯片粘接工藝作為微電子封裝技術(shù)中的關(guān)鍵環(huán)節(jié),對(duì)于確保芯片與外部電路的穩(wěn)定連接、提升封裝產(chǎn)品的可靠性和性能具有至關(guān)重要的作用。通過(guò)對(duì)芯片粘接工藝及其關(guān)鍵工藝參數(shù)的詳細(xì)介紹和分析,我們可以更好地理解這一工藝過(guò)程及其影響因素。未來(lái),隨著半導(dǎo)體技術(shù)的不斷發(fā)展,芯片粘接工藝將繼續(xù)面臨新的挑戰(zhàn)和機(jī)遇。通過(guò)不斷創(chuàng)新和改進(jìn),我們相信芯片粘接工藝將為半導(dǎo)體封裝領(lǐng)域帶來(lái)更多的創(chuàng)新和進(jìn)步。

-

芯片

+關(guān)注

關(guān)注

459文章

52252瀏覽量

436837 -

半導(dǎo)體封裝

+關(guān)注

關(guān)注

4文章

292瀏覽量

14317 -

微電子

+關(guān)注

關(guān)注

18文章

399瀏覽量

41729

發(fā)布評(píng)論請(qǐng)先 登錄

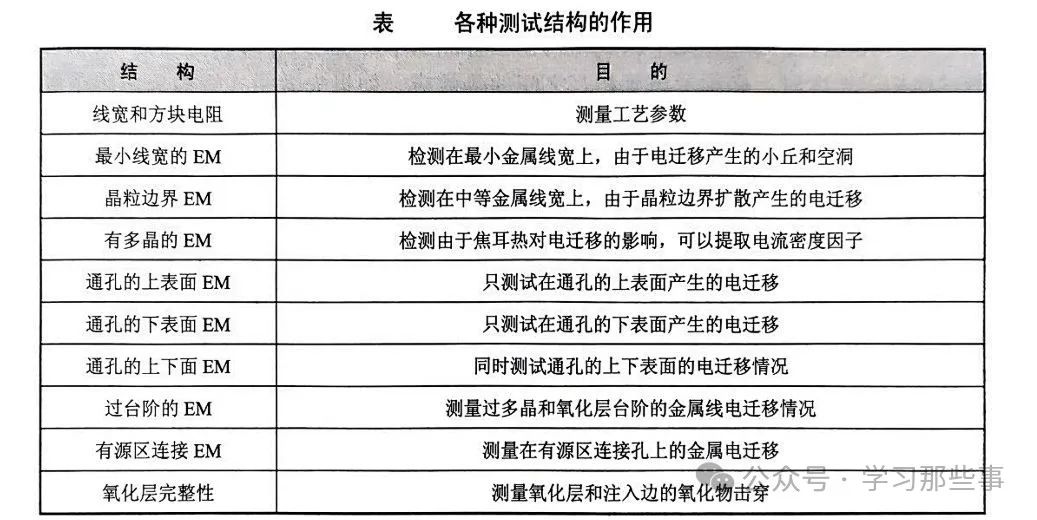

提供半導(dǎo)體工藝可靠性測(cè)試-WLR晶圓可靠性測(cè)試

如何實(shí)現(xiàn)高可靠性電源的半導(dǎo)體解決方案

《炬豐科技-半導(dǎo)體工藝》用于半導(dǎo)體封裝基板的化學(xué)鍍 Ni-P/Pd/Au

碳化硅功率器件可靠性之芯片研發(fā)及封裝篇

半導(dǎo)體器件可靠性及工藝控制

智能電表外殼粘接,使用密封膠可確保外殼固定的可靠性

半導(dǎo)體芯片封裝膠水的粘接原理

半導(dǎo)體封裝技術(shù)簡(jiǎn)介 什么是倒裝芯片技術(shù)?

半導(dǎo)體封裝的可靠性測(cè)試及標(biāo)準(zhǔn)介紹

半導(dǎo)體封裝技術(shù)的可靠性挑戰(zhàn)與解決方案

半導(dǎo)體集成電路的可靠性評(píng)價(jià)

漢思膠水在半導(dǎo)體封裝中的應(yīng)用概覽

提升功率半導(dǎo)體可靠性:推拉力測(cè)試機(jī)在封裝工藝優(yōu)化中的應(yīng)用

精通芯片粘接工藝:提升半導(dǎo)體封裝可靠性

精通芯片粘接工藝:提升半導(dǎo)體封裝可靠性

評(píng)論