來源:半導(dǎo)體小馬;作者:小馬

前面分享了先進封裝的四要素一分鐘讓你明白什么是先進封裝,今天分享一下先進封裝四要素中的再布線(RDL)。

RDL(Redistribution Layer)即重分布層,是先進封裝中實現(xiàn)芯片水平方向電氣延伸和互連的關(guān)鍵技術(shù),在 3D/2.5D 封裝集成以及 FOWLP(扇出型晶圓級封裝)中應(yīng)用廣泛。

一、工作原理

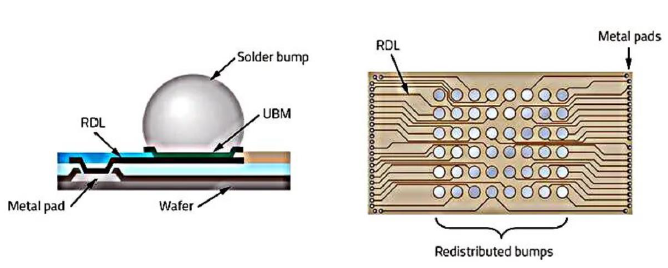

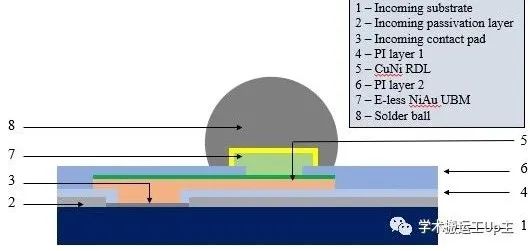

通過在芯片表面沉積金屬層和相應(yīng)的介電層,形成金屬導(dǎo)線,將 IO 端口重新設(shè)計到更寬敞的區(qū)域,構(gòu)建出表面陣列布局。簡單來說,就是把芯片原本位于邊緣或四周的 I/O 觸點,通過半導(dǎo)體工藝延伸到芯片表面其他位置,擴展布局到占位更寬松的區(qū)域,實現(xiàn) I/O 觸點的重新布線。

二、優(yōu)勢

降低設(shè)備成本:打破了傳統(tǒng)封裝中昂貴且耗時的引線鍵合和倒裝芯片鍵合工藝的束縛,通過減少設(shè)備所需的元件數(shù)量,有效降低設(shè)備成本。

減少占地面積:可將多個芯片集成到單個封裝中,極大地減少器件的整體占地面積,滿足智能手機、可穿戴設(shè)備等對空間要求極高的產(chǎn)品需求。

改善電氣性能:RDL 中介層信號通孔尺寸極小,可大幅改善 SerDes 信號完整性,其金屬厚度優(yōu)勢也能提升內(nèi)存 SI,同時低損耗介電材料可降低介電損耗,優(yōu)化整個封裝的電氣性能。

提高設(shè)計靈活性:RDL介質(zhì)層利用精細(xì)的線路寬度和間距,減少路由干擾,支持更多引腳數(shù)量,使 I/O 觸點間距更靈活,凸點面積更大,為芯片設(shè)計提供更大自由度。

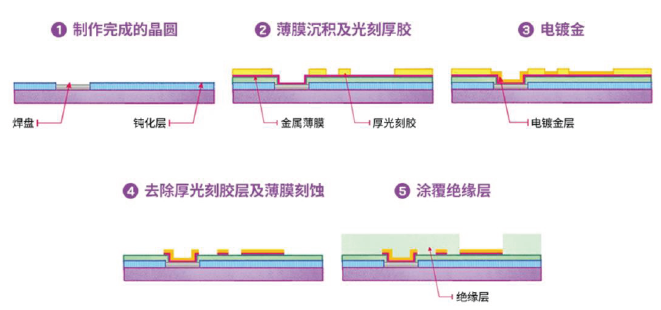

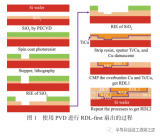

三、工藝流程

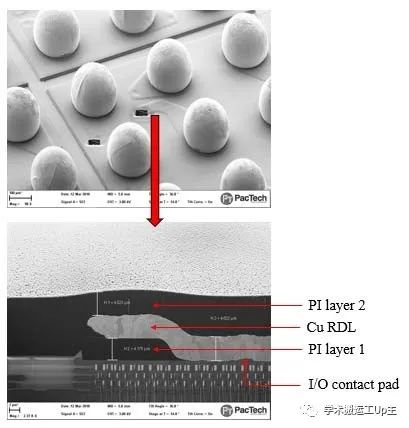

在重新分配層工藝中,首先通過濺射工藝創(chuàng)建一層金屬薄膜,之后在金屬薄膜上涂覆厚層光刻膠。隨后利用光刻工藝?yán)L制電路圖案,在電路圖案的曝光區(qū)域電鍍金層,以形成金屬引線。由于重新分配工藝本身就是重建焊盤的工藝,因此確保引線鍵合強度是十分重要的。這也正是被廣泛用于引線鍵合的材料—金,被用于電鍍的原因。

四、應(yīng)用領(lǐng)域

RDL 技術(shù)已廣泛應(yīng)用于MEMS器件、傳感器、功率器件、存儲器、微處理器和圖形處理器等眾多領(lǐng)域的封裝,為實現(xiàn)更小、更快、更高效的芯片設(shè)計提供技術(shù)支撐。

在WLP中:在FIWLP/FOWLP中,RDL是最為關(guān)鍵的技術(shù),通過RDL將IOPad進行扇入Fan-In或扇出Fan-Out,形成不同類型的晶圓級封裝。

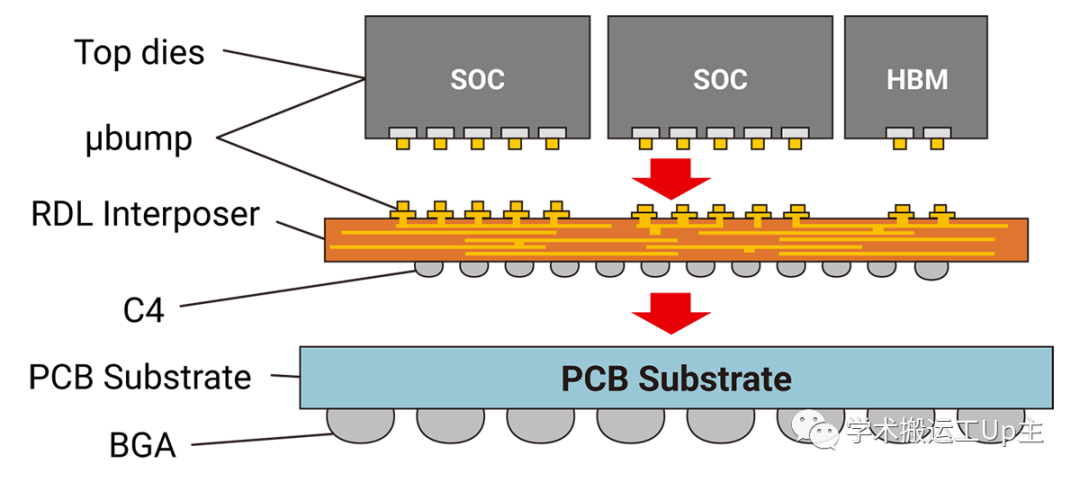

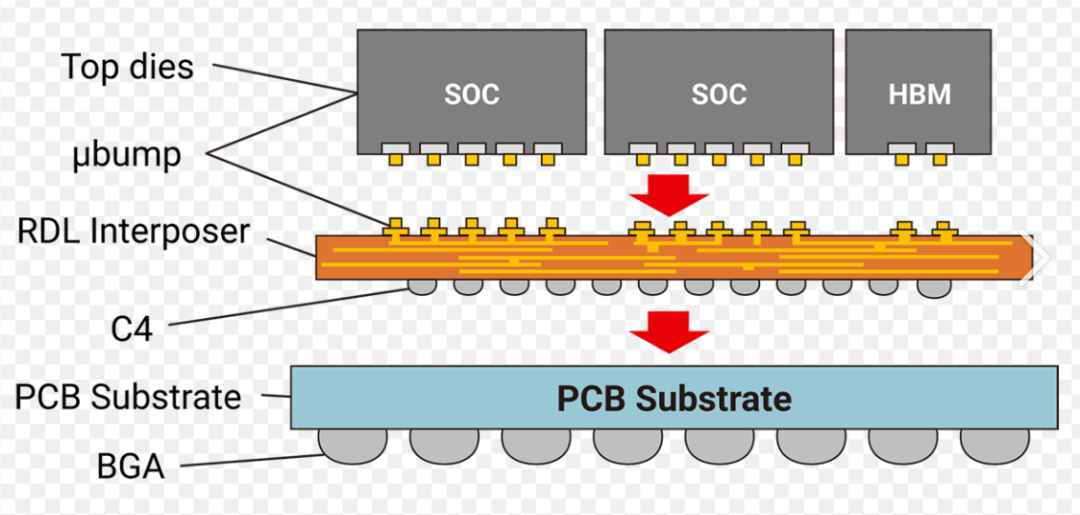

在2.5D中:除了硅基板上的TSV,RDL同樣不可或缺,通過RDL將網(wǎng)絡(luò)互聯(lián)并分布到不同的位置,從而將硅基板上方芯片的Bump和基板下方的Bump連接。

在3D中:對于上下堆疊是同一種芯片,通常TSV就可以直接完成電氣互聯(lián)功能了,而堆疊上下如果是不同類型芯片,則需要通過RDL重新布線層將上下層芯片的IO進行對準(zhǔn),從而完成電氣互聯(lián)。

五、技術(shù)發(fā)展

目前 4 層 RDL 技術(shù)已經(jīng)成熟,良率可達 99%,能滿足約 85% 的封裝需求。未來,RDL 工藝將朝著提高粘附力,減少熱循環(huán)過程中的機械應(yīng)力和熱應(yīng)力的方向發(fā)展,同時對布線檢測等設(shè)備也提出了更高要求。

-

芯片

+關(guān)注

關(guān)注

459文章

52446瀏覽量

439886 -

晶圓

+關(guān)注

關(guān)注

53文章

5149瀏覽量

129674 -

先進封裝

+關(guān)注

關(guān)注

2文章

471瀏覽量

609

原文標(biāo)題:先進封裝四要素中再布線(RDL)是什么?

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

先進封裝關(guān)鍵技術(shù)之TSV框架研究

芯片設(shè)計中再分布層(RDL)技術(shù)的優(yōu)勢

晶圓級封裝中的窄間距RDL技術(shù)

先進封裝RDL-first工藝研究進展

先進封裝技術(shù)及發(fā)展趨勢

什么是先進封裝?先進封裝技術(shù)包括哪些技術(shù)

Manz亞智科技 RDL先進制程加速全球板級封裝部署和生產(chǎn)

芯片先進封裝里的RDL

芯片封裝中的RDL(重分布層)技術(shù)

先進封裝中的RDL技術(shù)是什么

先進封裝中的RDL技術(shù)是什么

評論