聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1645文章

22050瀏覽量

618423 -

可編程邏輯

+關注

關注

7文章

526瀏覽量

44762 -

quartus

+關注

關注

17文章

173瀏覽量

75562

發布評論請先 登錄

相關推薦

熱點推薦

FPGA quartus ii里的靜態時序分析

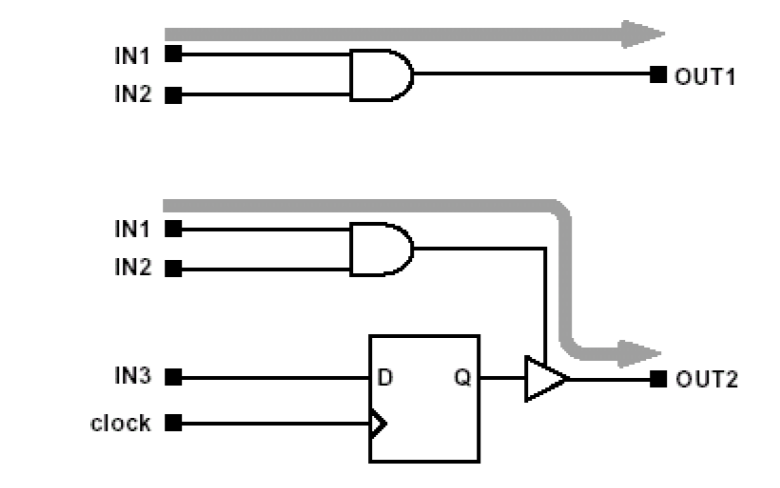

在fpga工程中加入時序約束的目的: 1、給quartusii 提出時序要求; 2、quartusii 在布局布線時會盡量優先去滿足給出的時序要求; 3、STA靜態

FPGA的IO口時序約束分析

在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現PCB板級的時序收斂。因此,

發表于 09-27 09:56

?2055次閱讀

靜態時序分析在高速 FPGA設計中的應用

介紹了采用STA (靜態時序分析)對FPGA (現場可編程門陣列)設計進行時序驗證的基本原理,并介紹了幾種與STA相關聯的時序約束。針對

發表于 05-27 08:58

?70次下載

正點原子FPGA靜態時序分析與時序約束教程

時序分析結果,并根據設計者的修復使設計完全滿足時序約束的要求。本章包括以下幾個部分: 1.1 靜態時序分析簡介 1.2

發表于 11-11 08:00

?66次下載

如何讀懂FPGA開發過程中的Vivado時序報告?

FPGA開發過程中,vivado和quartus等開發軟件都會提供時序報告,以方便開發者判斷自己的工程時序是否滿足時序要求。

發表于 06-26 15:29

?1660次閱讀

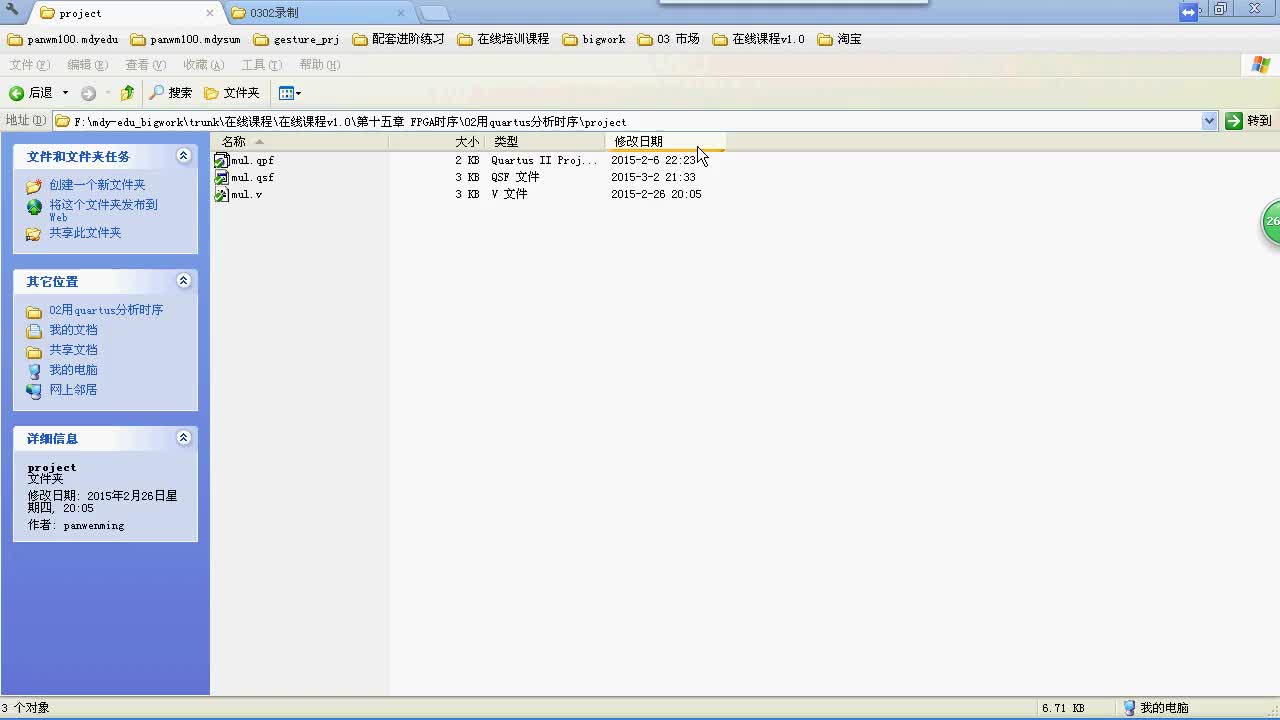

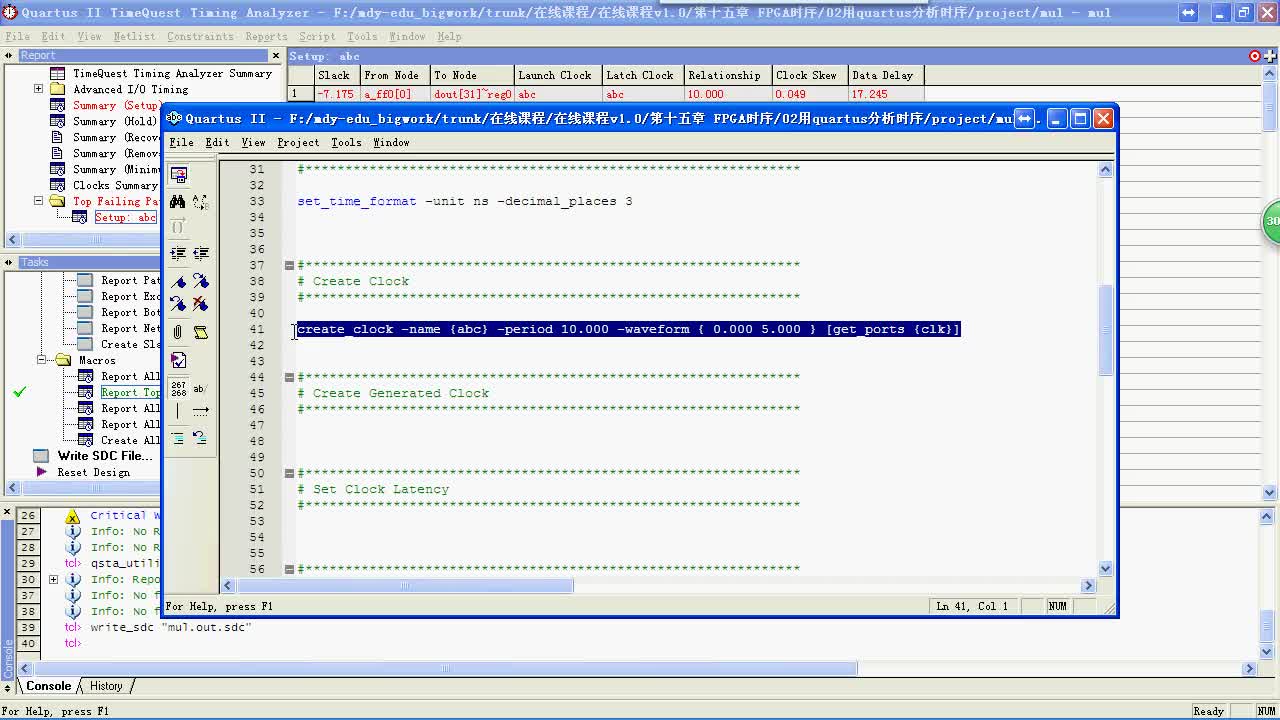

FPGA時序:用quartus分析時序

FPGA時序:用quartus分析時序

評論