大多數(shù)數(shù)字功能可分為:數(shù)據(jù)通道、儲存器、控制單元、I/O。加法器和乘法器屬于數(shù)據(jù)通道部分。

一般對數(shù)據(jù)通道有如下要求:首先是規(guī)整性以優(yōu)化版圖,其次是局域性(時間、空間,算子相鄰布置)以使版圖緊湊,正交性(數(shù)據(jù)流、控制流)以便規(guī)整布線,另外還需要層次化和模塊化。

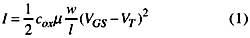

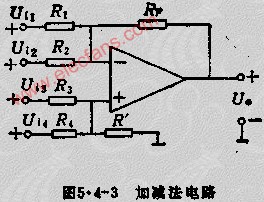

- 簡單加法器

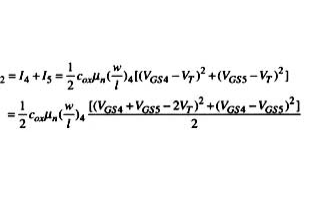

簡單加法器是一個3輸入2輸出的邏輯單元,輸入是兩個相加位和一個前級進位,輸出是和,以及本級進位。功能就是實現(xiàn)帶進位的1位加法。邏輯表達式是:

SUM=A xor B xor Cin (異或的符號我不知道怎么弄出來,只好用xor代替了。)

Carry=AB+Cin(A+B)用組合邏輯來實現(xiàn)的話有下面幾種方法

一是普通方法,將上面的邏輯表達式轉(zhuǎn)換成只有與或非的形式(便于電路實現(xiàn))

SUM=ABC+A(not B)(not C)+(not A)(not B)C+(not A)B(not C) 需要16個管子

Carry=AB+BC+AC 需要10個管子

另外A、B、C都需要反相信號(每個反相器2個管子)所以還需要6個。

總共32個管子。上面計算管子的時候,邏輯是按管子串聯(lián)算的,這樣省管子,但是因為串聯(lián)也會帶來問題(閾值電壓損失?)。另外一種稍微使用了一點技巧,它利用輸出的進位產(chǎn)生“和”位

SUM=ABC+(A+B+C)(not Carry)

Carry=AB+(A+B)C

這樣總共需要28個管子。這種形式的電路重復利用Carry-out信號來產(chǎn)生 SUM,不需要異或門,節(jié)省了管子。但是它也有缺點:SUM信號比Carry遲產(chǎn)生。不過話又說回來,這未嘗不是一個優(yōu)點,因為在加法器鏈中,關(guān)鍵路徑是進位信號的傳遞,也就是說通常加法器鏈的延時取決于每個加法器進位信號的產(chǎn)生時間(下面將要討論這方面的問題),而不是“和”信號的延時。所以這種電路的這個特點不會對速度造成太大的影響。對組合邏輯加法器可以進行如下的優(yōu)化:

- 加大Carry Stage中管子的尺寸以提高Carry out的驅(qū)動能力。

- 減小Carry out信號驅(qū)動的管子的尺寸(在Sum Stage中),以減小Carry out信號的負載。

- 盡量使Carry out的線短,并少用擴散層作為布線層。

- 把Carry in信號驅(qū)動的管子放在靠近輸出端(減少Body Effect)。

- 通過仔細模擬決定管子尺寸。

除了使用組合邏輯以外,還可以使用傳輸門邏輯來實現(xiàn)簡單加法器。這里就不細談了。傳輸門加法器共需24個管子。它的特點是:輸出既有SUM、Carry,又有它們的反信號; SUM和Carry的延時時間相同;無閾值損失。當然,它的速度不如組合邏輯。

- 串行進位加法器

串行進位加法器可以說是最簡單的一種多位加法器,它是由n個一位加法器(也就是上面分析的簡單加法器)串聯(lián)而成,第i級的Carry-out用來產(chǎn)生第i+1級的 SUM和Carry。

這種加法器結(jié)構(gòu)簡單,但是速度慢,n位加法器的延時=n * (一位延時)。這種加法器可以通過同時利用正信號和反信號來達到優(yōu)化進位鏈的效果。(這種方法很巧妙,不過空口說好像不大容易說清楚,以后把圖畫出來就清楚了,:-P)

- 超前進位加法器

- 曼徹斯特進位鏈

- 條件求和加法器

- 進位選擇加法器

- 其他加法器

- 加法器小結(jié)

電子發(fā)燒友App

電子發(fā)燒友App

評論