行業背景 隨著工業技術的不斷發展,物聯網作為新興生產力正在改變許多行業的工作方式。在半導體芯片行業,自動蝕刻機的物聯網應用正在助力企業達到監控設備更加便利、故障運維更加高效、數據分析更加精準等等

2024-03-20 17:52:39 823

823

。

通過實驗驗證和數據分析得出金絲與金鋁焊盤鍵合和鎳鈀金焊盤鍵合的工藝窗口和關鍵參數,使其能滿足在金線線弧高度小于100um、弧長小于500um的要求下,鍵合后第一焊點和第二焊點拉力要大于5gf,并

2024-03-10 14:14:51

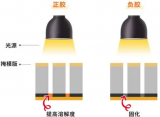

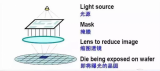

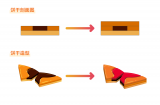

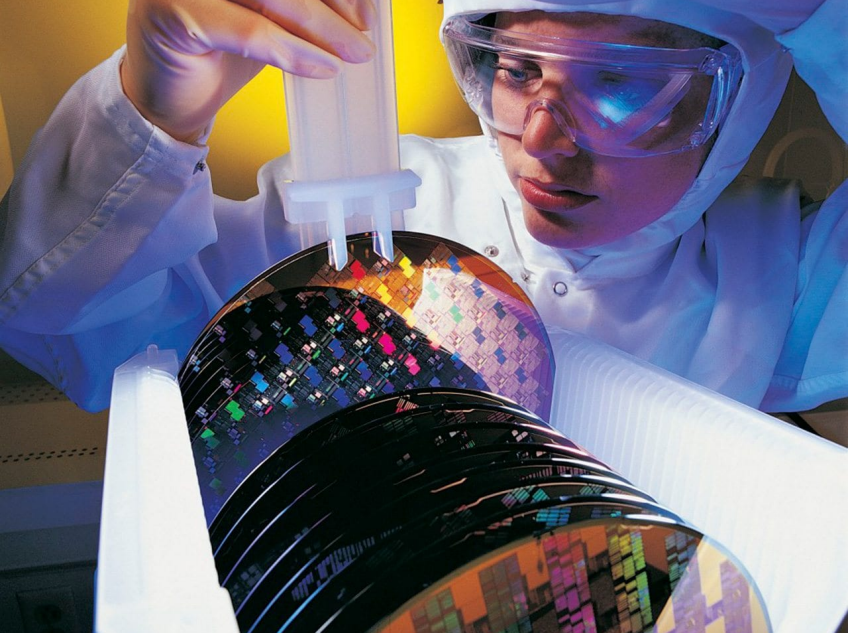

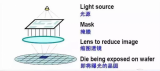

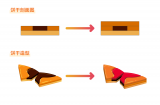

利用光刻機發出的光通過具有圖形的光罩對涂有光刻膠的薄片曝光,光刻膠見光后會發生性質變化,從而使光罩上得圖形復印到薄片上,從而使薄片具有電子線路圖的作用。

2024-03-06 14:28:50 62

62

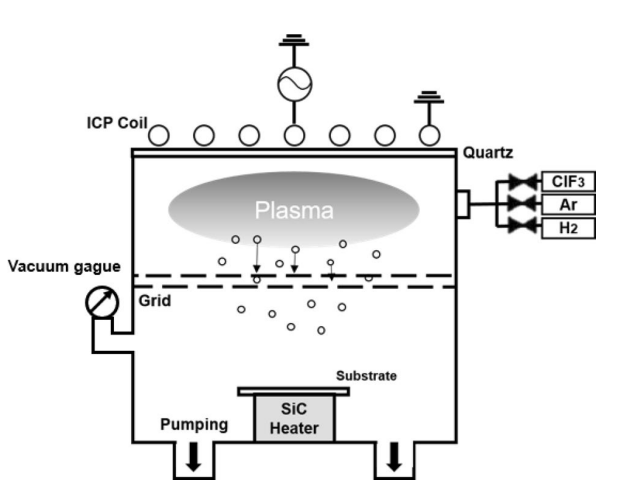

根據已公開的研究報告,東京電子的新式蝕刻機具備在極低溫環境下進行高速蝕刻的能力。據悉,該機器可在33分鐘內完成10微米的蝕刻工作。此外,設備使用了新開發的激光氣體,搭配氬氣和氟化碳氣體以提升工藝水平。

2024-02-18 15:00:22 109

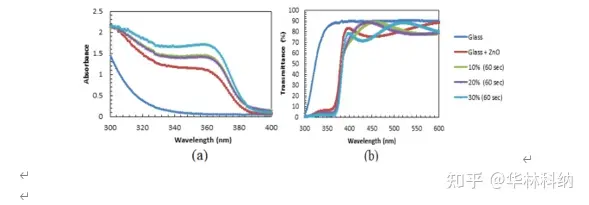

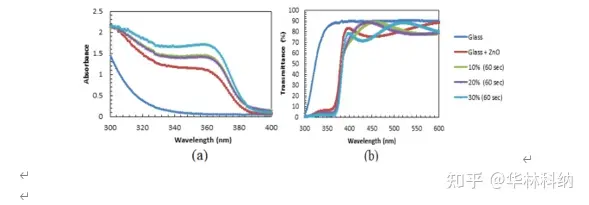

109 蝕刻時間和過氧化氫濃度對ZnO玻璃基板的影響 本研究的目的是確定蝕刻ZnO薄膜的最佳技術。使用射頻濺射設備在玻璃基板上沉積ZnO。為了蝕刻ZnO薄膜,使用10%、20%和30%的過氧化氫(H2O2

2024-02-02 17:56:45 306

306

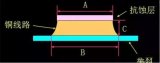

通常正片工藝是以堿性蝕刻工藝為基礎的。底片上面,所需的路徑或銅表面是黑色的,而不需要的部分是完全透明的。同樣,在路線工藝曝光后,完全透明的部分被暴露在紫外線下的干膜阻滯劑的化學作用硬化,隨后的顯影過程將在下一工序中沖走無硬襯底的干膜

2024-01-17 15:33:35 163

163 光照條件的設置、掩模版設計以及光刻膠工藝等因素對分辨率的影響都反映在k?因子中,k?因子也常被用于評估光刻工藝的難度,ASML認為其物理極限在0.25,k?體現了各家晶圓廠運用光刻技術的水平。

2023-12-18 10:53:05 326

326

在微電子制造領域,光刻機和蝕刻機是兩種不可或缺的重要設備。它們在制造半導體芯片、集成電路等微小器件的過程中發揮著關鍵作用。然而,盡管它們在功能上有所相似,但在技術原理、應用場景等方面卻存在著明顯的區別。本文將對光刻機和蝕刻機的差異進行深入探討。

2023-12-16 11:00:09 371

371

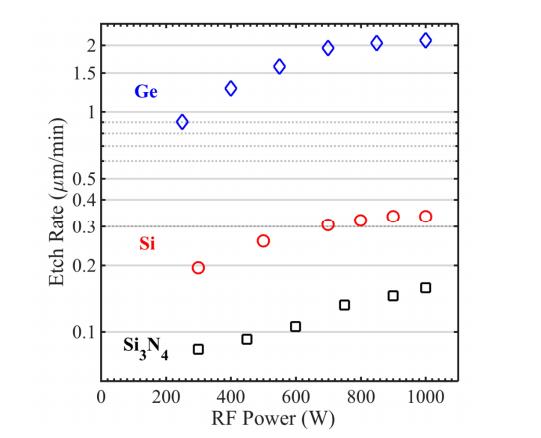

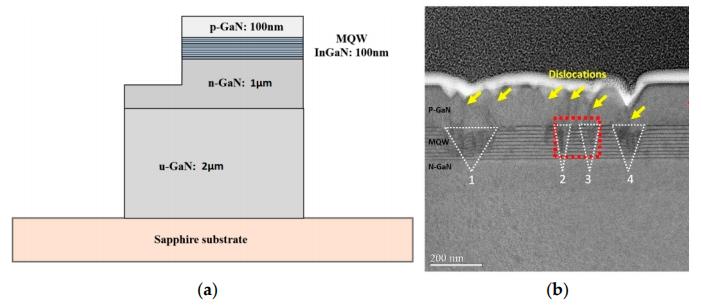

技術提供了典型應用。蝕刻工藝對器件特性有著較大的影響,尤其是在精確控制蝕刻深度和較小化等離子體損傷的情況下影響較大。

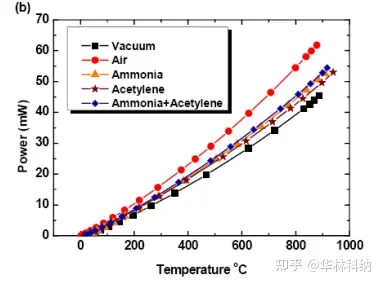

2023-12-13 09:51:24 294

294

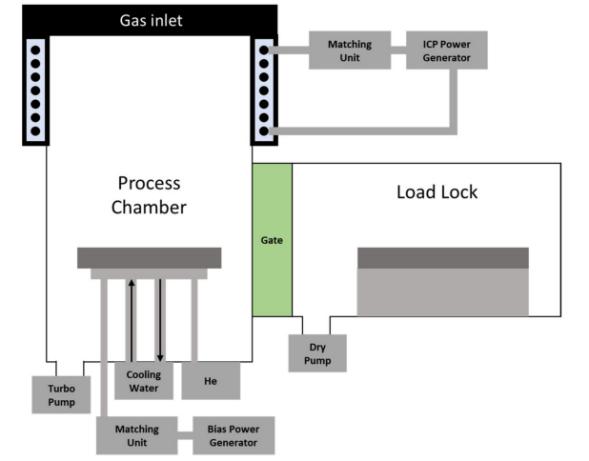

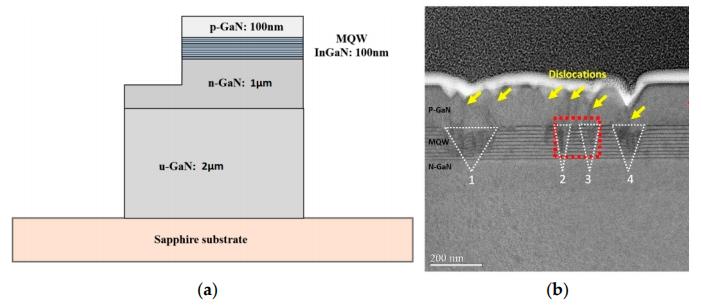

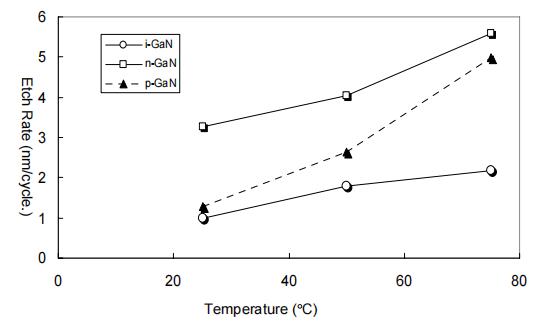

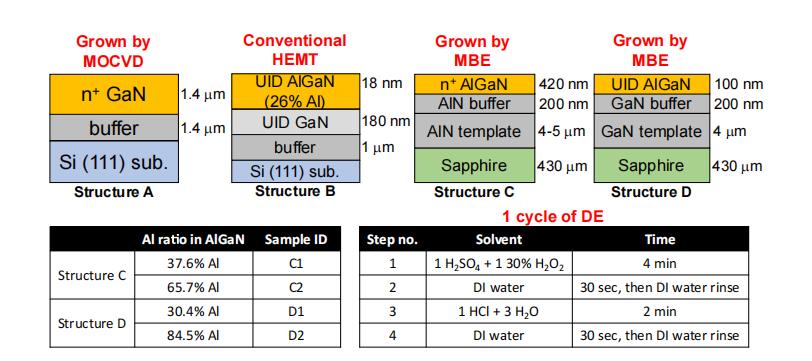

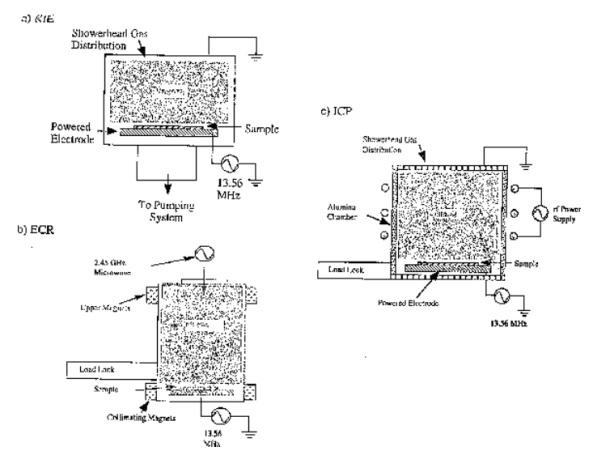

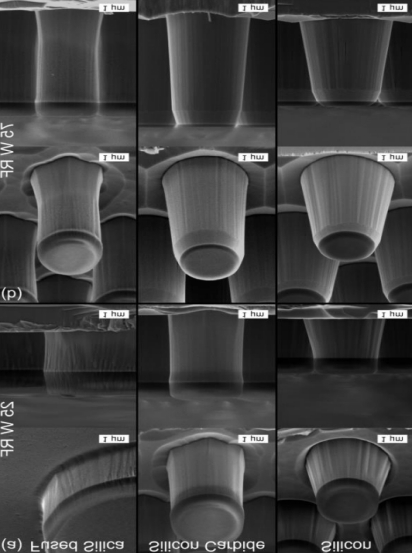

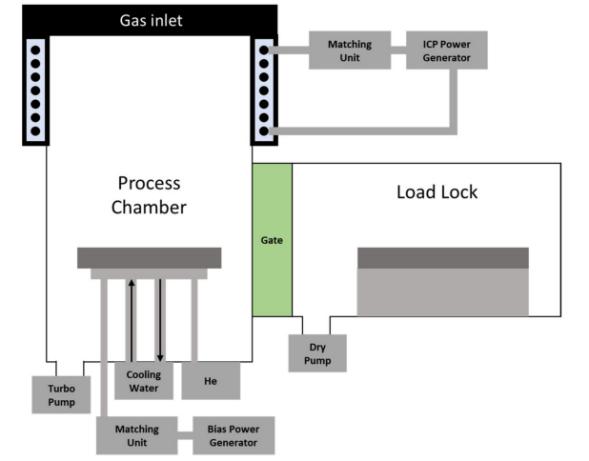

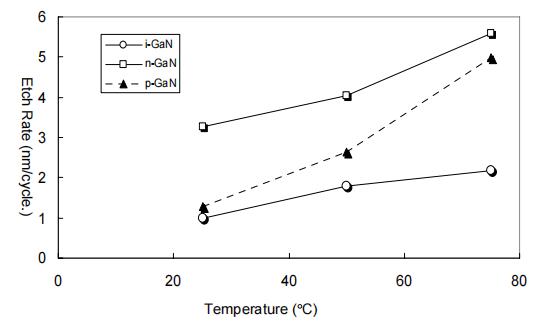

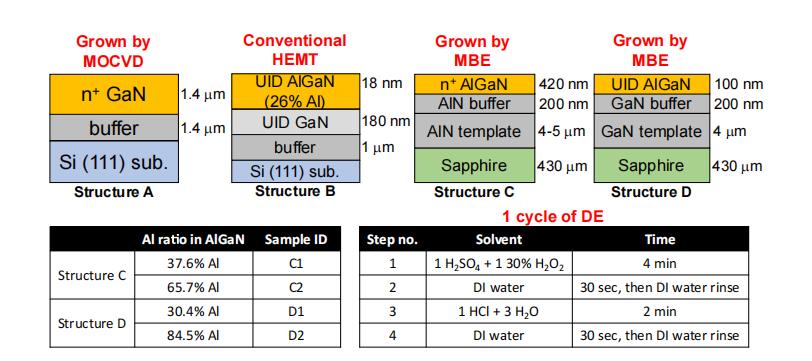

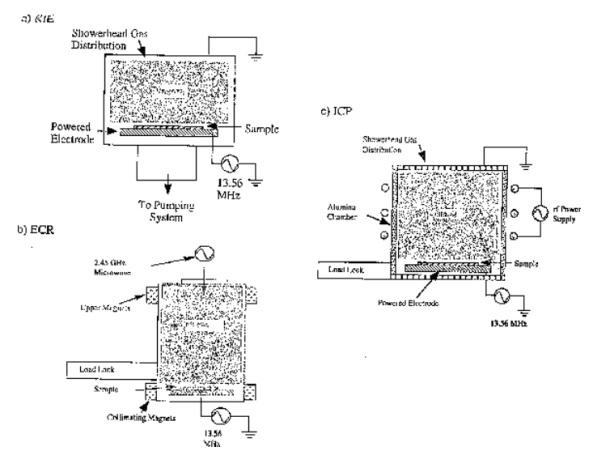

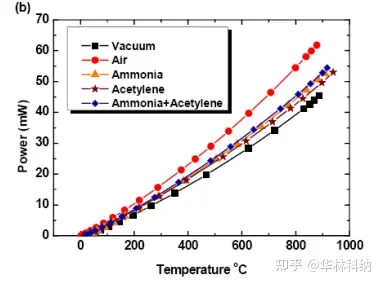

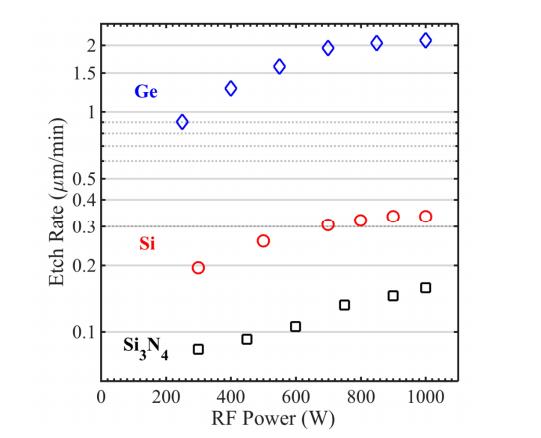

GaN和相關合金由于其優異的特性以及大的帶隙、高的擊穿電場和高的電子飽和速度而成為有吸引力的材料之一,與優化工藝過程相關的成熟材料是有源/無源射頻光電子器件近期發展的關鍵問題。專用于三元結構的干法蝕刻工藝特別重要,因為這種器件通常包括異質結構。因此,GaN基光電器件的制造部分或全部依賴于干法刻蝕。

2023-12-11 15:04:20 188

188

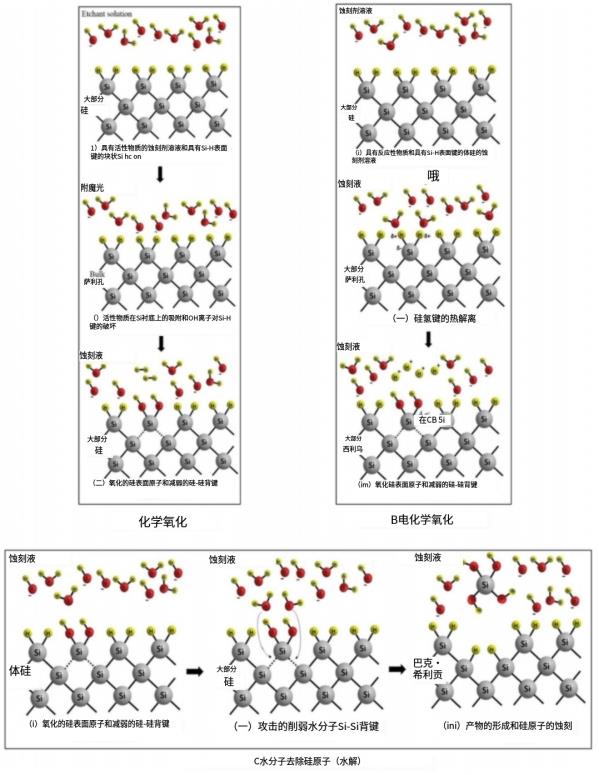

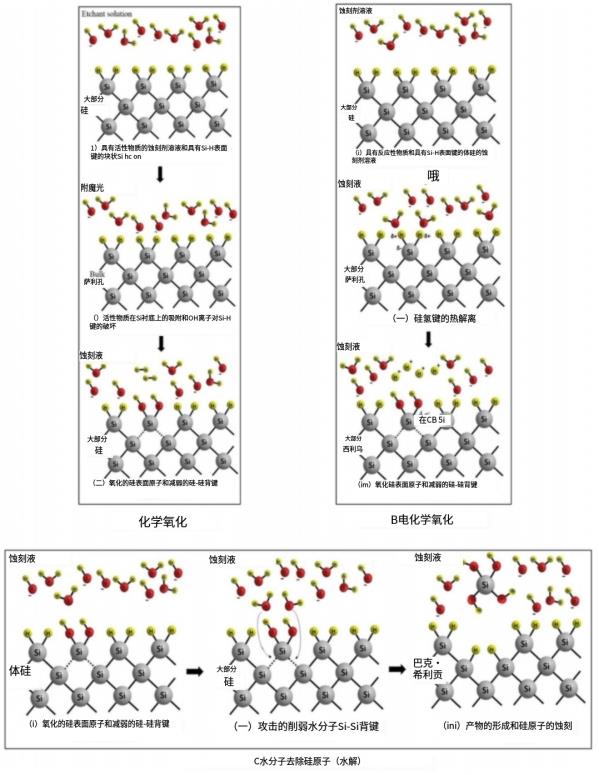

刻蝕的機制,按發生順序可概分為「反應物接近表面」、「表面氧化」、「表面反應」、「生成物離開表面」等過程。所以整個刻蝕,包含反應物接近、生成物離開的擴散效應,以及化學反應兩部分。

2023-12-11 10:24:18 250

250

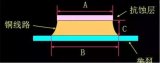

另外一種工藝方法是整個板子上都鍍銅,感光膜以外的部分僅僅是錫或鉛錫抗蝕層。這種工藝稱為“全板鍍銅工藝“。與圖形電鍍相比,全板鍍銅的缺點是板面各處都要鍍兩次銅而且蝕刻時還必須都把它們腐蝕掉。

2023-12-06 15:03:45 263

263 按工藝要求排放出部分比重高的溶液經分析后補加氯化銨和氨的水溶液,使蝕刻液的比重調整到工藝充許的范圍。

2023-12-06 15:01:46 286

286 W刻蝕工藝中使用SF6作為主刻步氣體,并通過加入N2以增加對光刻膠的選擇比,加入O2減少碳沉積。在W回刻工藝中分為兩步,第一步是快速均勻地刻掉大部分W,第二步則降低刻蝕速率減弱負載效應,避免產生凹坑,并使用對TiN有高選擇比的化學氣體進行刻蝕。

2023-12-06 09:38:53 1536

1536 光刻工藝就是把芯片制作所需要的線路與功能做出來。利用光刻機發出的光通過具有圖形的光罩對涂有光刻膠的薄片曝光,光刻膠見光后會發生性質變化,從而使光罩上得圖形復印到薄片上,從而使薄片具有電子線路圖的作用

2023-12-04 09:17:24 1335

1335

GaN作為寬禁帶III-V族化合物半導體最近被深入研究。為了實現GaN基器件的良好性能,GaN的處理技術至關重要。目前英思特已經嘗試了許多GaN蝕刻方法,大部分GaN刻蝕是通過等離子體刻蝕來完成

2023-12-01 17:02:39 259

259

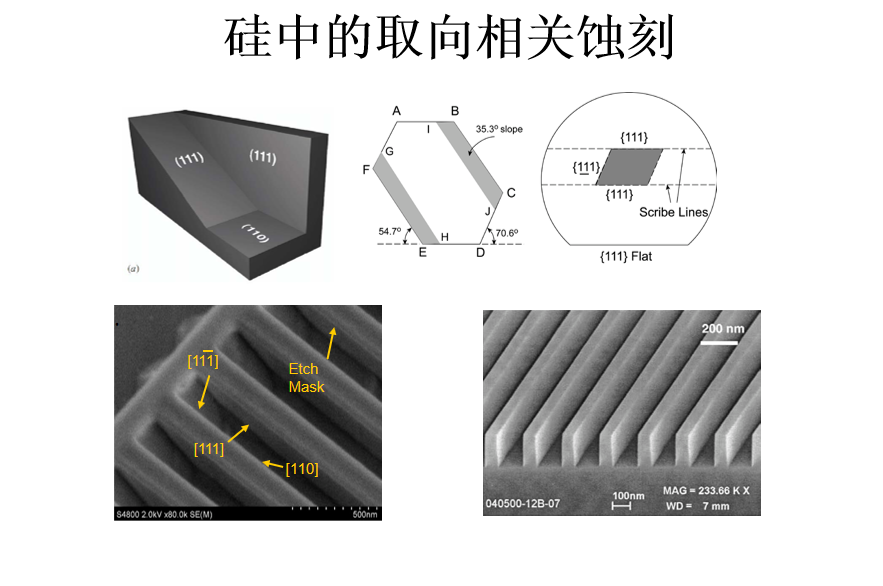

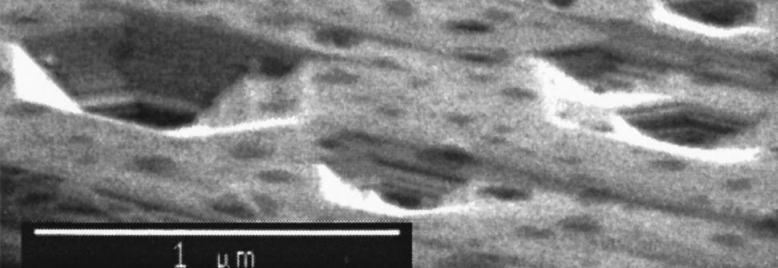

由于其獨特的材料特性,III族氮化物半導體廣泛應用于電力、高頻電子和固態照明等領域。加熱的四甲基氫氧化銨(TMAH)和KOH3處理的取向相關蝕刻已經被用于去除III族氮化物材料中干法蝕刻引起的損傷,并縮小垂直結構。

2023-11-30 09:01:58 166

166

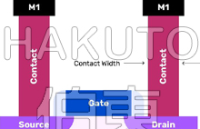

在半導體芯片等器件工藝中,后道制程中的金屬連接是經過金屬薄膜沉積,圖形化和蝕刻工藝,最后在器件元件之間得到導電連接。

2023-11-29 09:15:31 434

434

一、上架整體流程

二、上架HarmonyOS應用

獲取到HarmonyOS應用軟件包后,開發者可將應用提交至AGC申請上架。上架成功后,用戶即可在華為應用市場搜索獲取開發者的HarmonyOS

2023-11-24 14:44:27

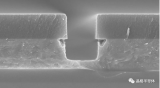

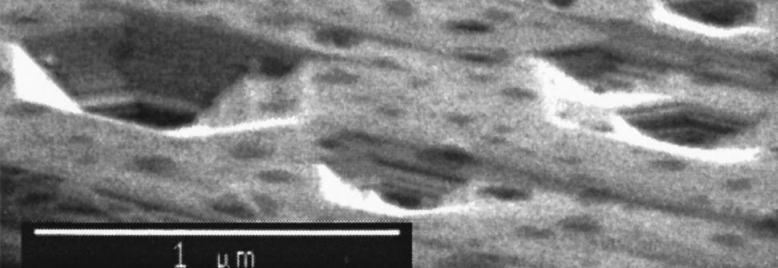

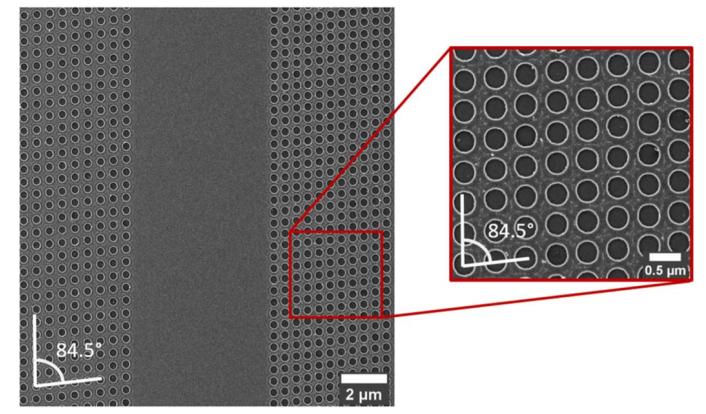

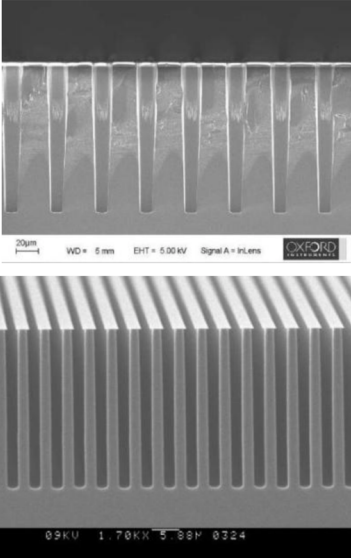

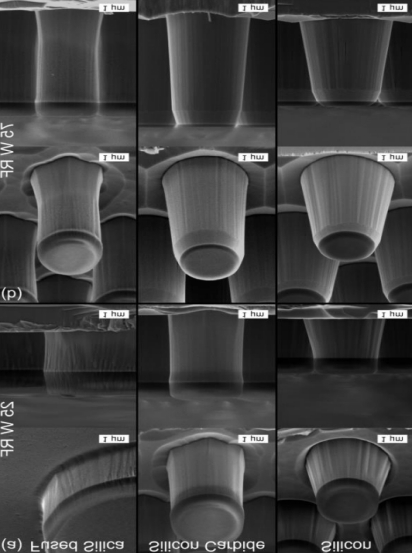

目前,大多數III族氮化物的加工都是通過干法等離子體蝕刻完成的。干法蝕刻有幾個缺點,包括產生離子誘導損傷和難以獲得激光器所需的光滑蝕刻側壁。干法蝕刻產生的側壁典型均方根(rms)粗糙度約為50納米

2023-11-24 14:10:30 241

241

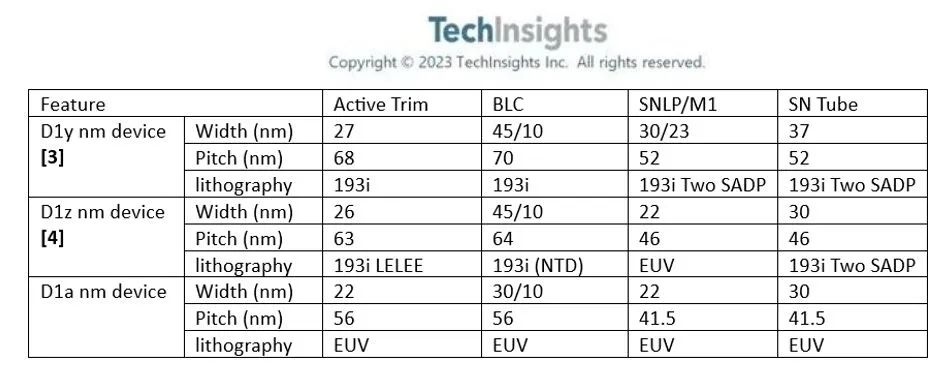

三星D1a nm LPDDR5X器件的EUV光刻工藝

2023-11-23 18:13:02 579

579

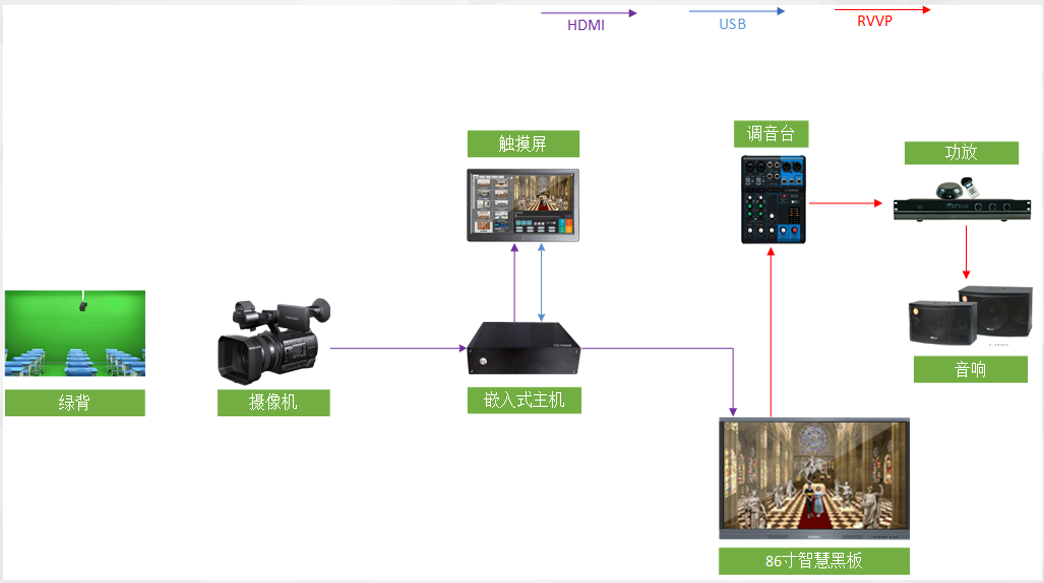

通過這個功能,我們可以實現直接使用NDI信號輸入帶透明效果(alpha通道)的CG素材。

2023-11-15 10:13:04 364

364

蝕刻設備的結構及不同成分的蝕刻液都會對蝕刻因子或側蝕度產生影響,或者用樂觀的話來說,可以對其進行控制。采用某些添加劑可以降低側蝕度。這些添加劑的化學成分一般屬于商業秘密,各自的研制者是不向外界透露的。至于蝕刻設備的結構問題,后面的章節將專門討論。

2023-11-14 15:23:10 217

217 自動蝕刻機是利用電解作用或化學反應對金屬板進行處理,以獲得所需圖紋、花紋、幾何形狀的自動化設備,廣泛應用于芯片、數碼、航空、機械、標牌等領域中。現有一家蝕刻機設備制造商,要求對全國各地的蝕刻機設

2023-11-08 13:59:52 146

146

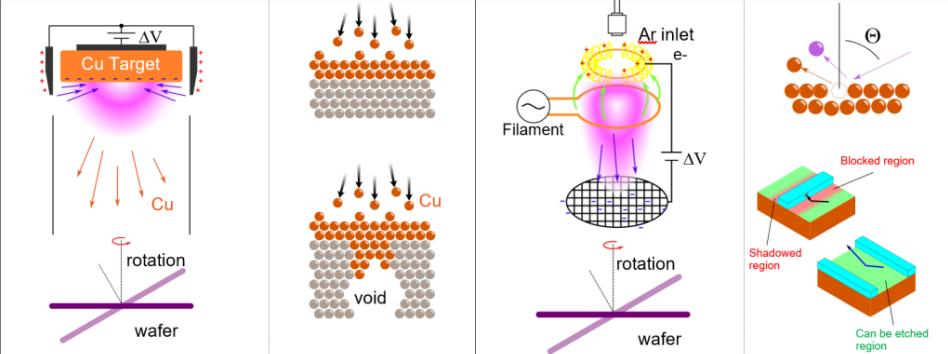

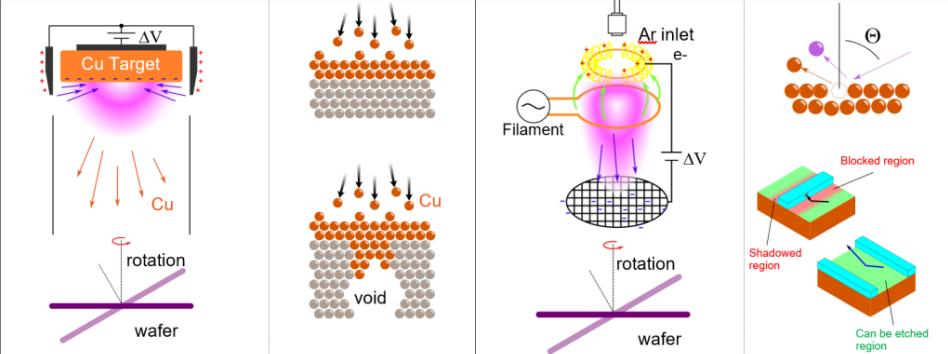

近年來,銅(Cu)作為互連材料越來越受歡迎,因為它具有低電阻率、不會形成小丘以及對電遷移(EM)故障的高抵抗力。傳統上,化學機械拋光(CMP)方法用于制備銅細線。除了復雜的工藝步驟之外,該方法的一個顯著缺點是需要許多對環境不友好的化學品,例如表面活性劑和強氧化劑。

2023-11-08 09:46:21 188

188

TAIYO太陽誘電MLCC陶瓷貼電容問答小課堂

2023-11-01 16:04:02 224

224 ,建議對于此位置采用圖鍍銅鎳金制作;

3、如果客戶已經做好引線引出需要鍍硬金的焊盤時,只需要在外層蝕刻后,走鍍硬金流程即可;

4、當金厚>4um以上的時,不可以制作;

5、針對鍍金+鍍硬金中使用二次干

2023-10-27 11:25:48

;

5、針對鍍金+鍍硬金中使用二次干膜的工藝,金厚與鍍硬金焊盤的間距對應要求:常規金厚0.38um最小7mil,0.8um最小8mil,1.0um以上10mil。

二、全板電鍍軟金

1、金厚要求

2023-10-24 18:49:18

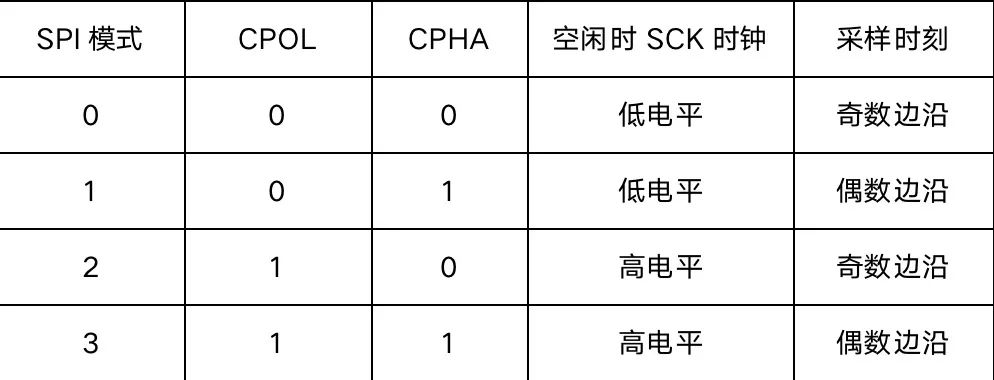

MCU微課堂 | CKS32F4xx系列產品SPI通信

2023-10-24 17:12:19 371

371

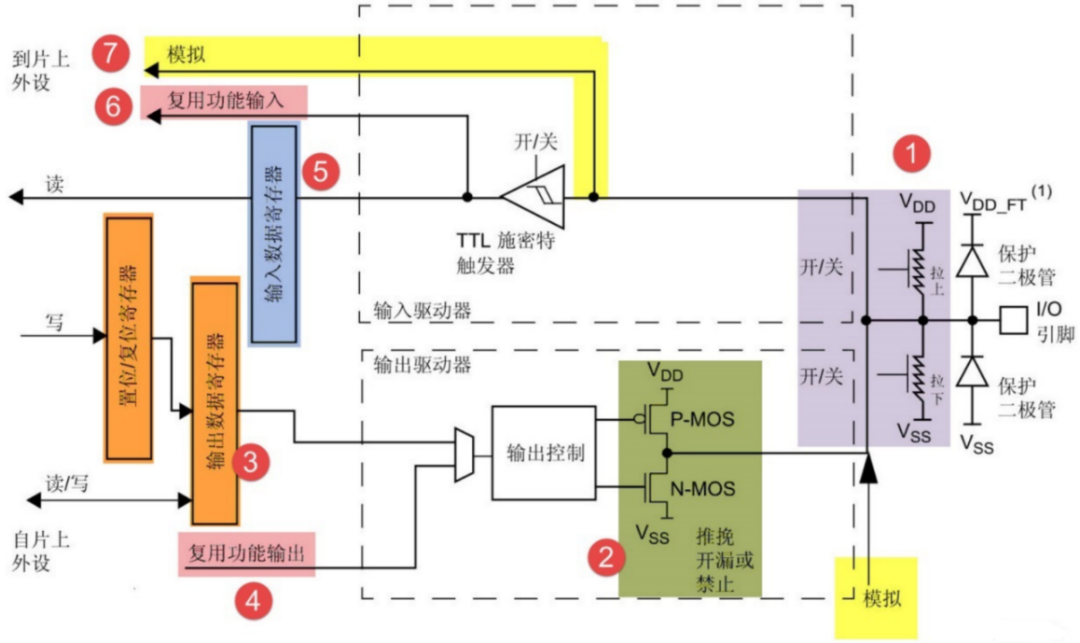

MCU微課堂 | CKS32F4xx系列產品GPIO口配置

2023-10-24 15:14:00 332

332

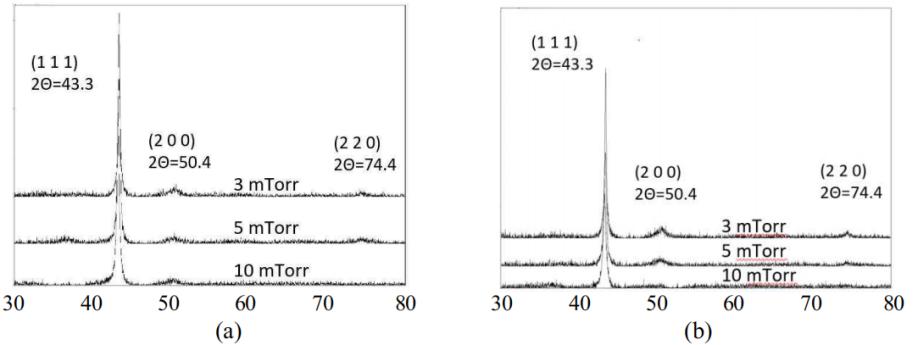

Bumping工藝是一種先進的封裝工藝,而Sputter是Bumping工藝的第一道工序,其重要程度可想而知。Sputter的膜厚直接影響Bumping的質量,所以必須控制好Sputter的膜厚及均勻性是非常關鍵。

2023-10-23 11:18:18 475

475

干法蝕刻(dry etch)工藝通常由四個基本狀態構成:蝕刻前(before etch),部分蝕刻(partial etch),蝕刻到位(just etch),過度蝕刻(over etch),主要表征有蝕刻速率,選擇比,關鍵尺寸,均勻性,終點探測。

2023-10-18 09:53:19 788

788

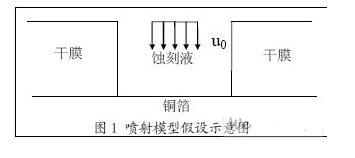

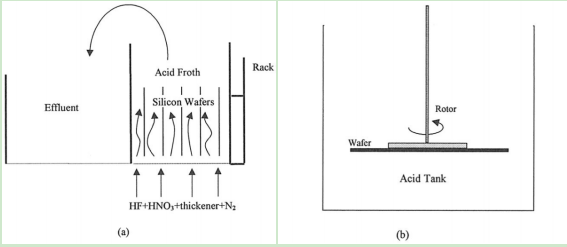

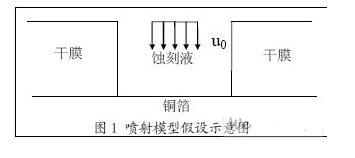

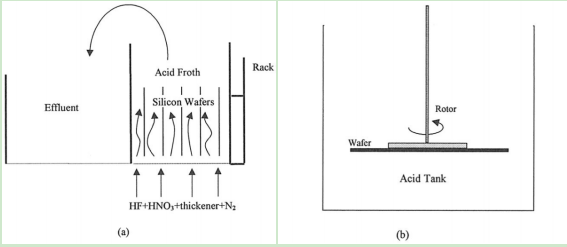

在精細印制電路制作過程中,噴淋蝕刻是影響產品質量合格率重要的工序之一。現有很多的文章對精細線路的蝕刻做了大量的研究,但是大多數都只停留在表象的研究中,并沒有從本質上認識噴淋蝕刻中出現的問題。

2023-10-17 15:15:35 164

164

蝕刻液的化學成分的組成:蝕刻液的化學組分不同,其蝕刻速率就不相同,蝕刻系數也不同。如普遍使用的酸性氯化銅蝕刻液的蝕刻系數通常是&;堿性氯化銅蝕刻液系數可達3.5-4。而正處在開發階段的以硝酸為主的蝕刻液可以達到幾乎沒有側蝕問題,蝕刻后的導線側壁接近垂直。

2023-10-16 15:04:35 553

553 GaN及相關合金可用于制造藍色/綠色/紫外線發射器以及高溫、高功率電子器件。由于 III 族氮化物的濕法化學蝕刻結果有限,因此人們投入了大量精力來開發干法蝕刻工藝。干法蝕刻開發一開始集中于臺面結構,其中需要高蝕刻速率、各向異性輪廓、光滑側壁和不同材料的同等蝕刻。

2023-10-07 15:43:56 319

319

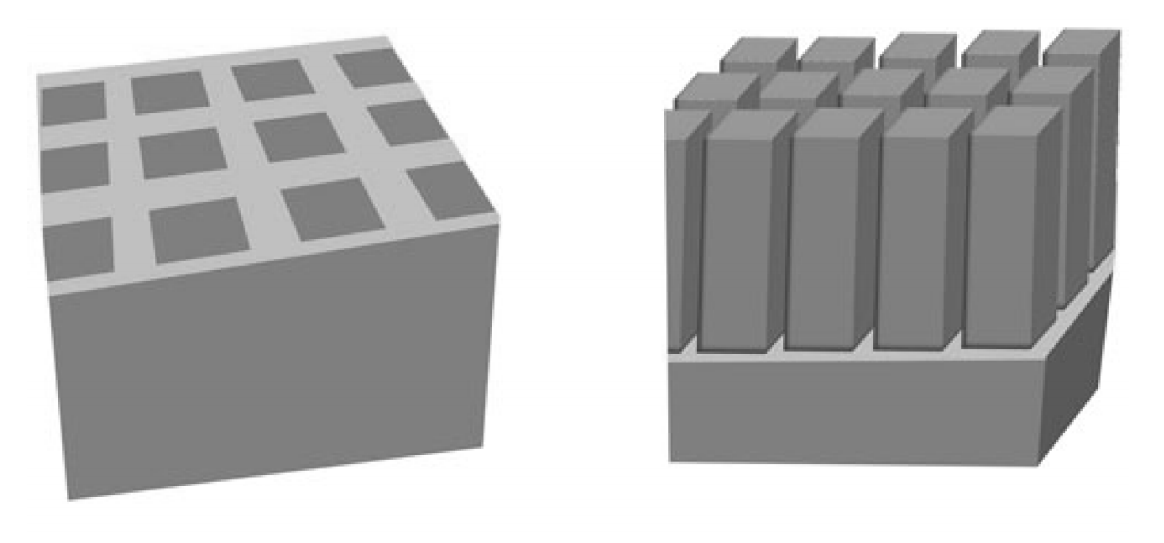

銅的電阻率取決于其晶體結構、空隙體積、晶界和材料界面失配,這在較小的尺度上變得更加重要。傳統上,銅(Cu)線的形成是通過使用溝槽蝕刻工藝在低k二氧化硅中蝕刻溝槽圖案,然后通過鑲嵌流用Cu填充溝槽來完成的。

2023-09-22 09:57:23 281

281

4層藍牙產品PCB設計素材

2023-09-20 07:43:16

一站式PCBA智造廠家今天為大家講講pcb打樣蝕刻工藝注意事項有哪些?PCB打樣蝕刻工藝注意事項。PCB打樣中,在銅箔部分預鍍一層鉛錫防腐層,保留在板外層,即電路的圖形部分,然后是其余的銅箔被化學方法腐蝕,稱為蝕刻。

2023-09-18 11:06:30 670

670 隨著技術的發展,與ic制造相關的排放量也增加了,特別是光刻和蝕刻能耗較大,例如n3工程中光刻工序產生的二氧化碳排放量約占45%。imec的工程師們半導體制造過程中產生的尾氣可以建模軟件平臺開發,可持續半導體技術及系統計劃(ssts)的使用率

2023-09-13 10:56:53 290

290 【摘要 / 前言】 電鍍會影響連接器系統的壽命和質量, 包括耐腐蝕性、導電性、可焊性,當然還有成本 。 ? ? 【小課堂背景】 ? ? 這是 Samtec質量工程經理 Phil Eckert 和首席

2023-09-08 09:22:32 472

472

要注意的是,蝕刻時的板子上面有兩層銅。在外層蝕刻工藝中僅僅有一層銅是必須被全部蝕刻掉的,其余的將形成最終所需要的電路。這種類型的圖形電鍍,其特點是鍍銅層僅存在于鉛錫抗蝕層的下面。

2023-09-07 14:41:12 474

474

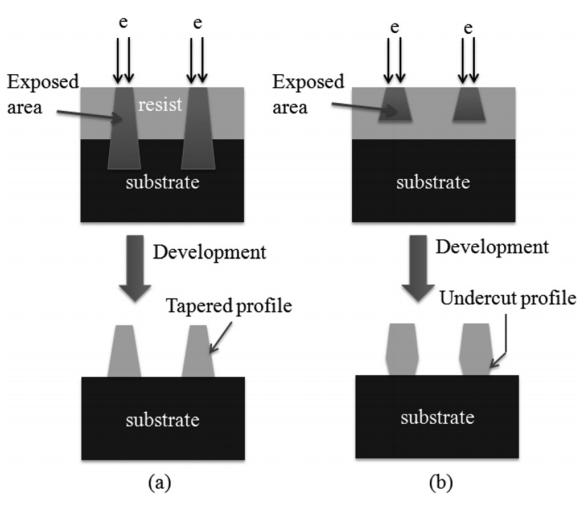

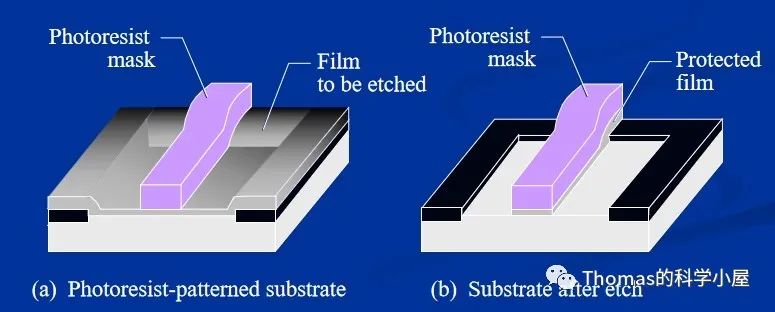

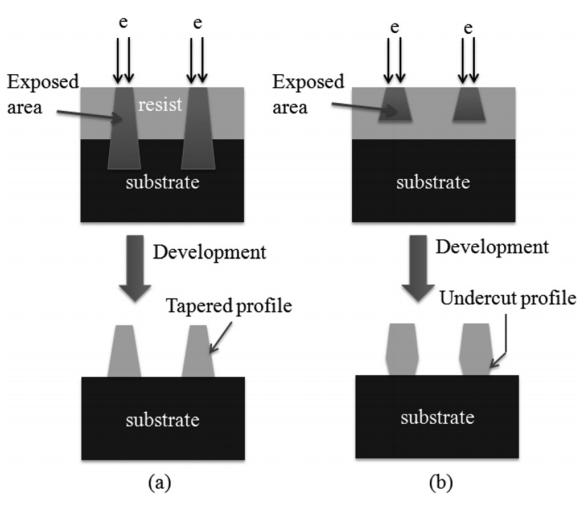

直接蝕刻和剝離是兩種比較流行的圖案轉移工藝。在直接蝕刻工藝中,首先使用光刻技術對聚合物抗蝕劑進行構圖,然后通過干法蝕刻技術用抗蝕劑作為掩模將圖案轉移到襯底或子層上。

2023-09-07 09:57:14 292

292

在印制板外層電路的加工工藝中,還有另外一種方法,就是用感光膜代替金屬鍍層做抗蝕層。這種方法非常近似于內層蝕刻工藝,可以參閱內層制作工藝中的蝕刻。

2023-09-06 09:36:57 811

811

一個優秀的工程師設計的產品一定是既滿足設計需求又滿足生產工藝。規范產品的電路設計,輔助PCB設計的相關工藝參數,使得生產出來的實物產品滿足可生產性、可測試性、可維修性等的技術規范要求。本文將從初學者

2023-08-28 13:55:03

半導體制造工藝之光刻工藝詳解

2023-08-24 10:38:54 1221

1221

光刻是半導體芯片生產流程中最復雜、最關鍵的工藝步驟,耗時長、成本高。半導體芯片生產的難點和關鍵點在于將電路圖從掩模上轉移至硅片上,這一過程通過光刻來實現, 光刻的工藝水平直接決定芯片的制程水平和性能水平。

2023-08-23 10:47:53 1586

1586

我們華林科納通過光學反射光譜半實時地原位監測用有機堿性溶液的濕法蝕刻,以實現用于線波導的氫化非晶硅(a-Si:H)膜的高分辨率厚度控制。由a-Si:H的本征各向同性結構產生的各向同性蝕刻導致表面

2023-08-22 16:06:56 239

239

在半導體制程中,移除殘余材料的“減法工藝”不止“刻蝕”一種,引入其他材料的“加法工藝”也非“沉積”一種。比如,光刻工藝中的光刻膠涂敷,其實也是在基底上形成各種薄膜;又如氧化工藝中晶圓(硅)氧化,也需要在基底表面添加各種新材料。那為什么唯獨要強調“沉積”工藝呢?

2023-08-17 15:33:27 370

370

PCB蝕刻工藝中的“水池效應”現象,通常發生在頂部,這種現象會導致大尺寸PCB整個板面具有不同的蝕刻質量。

2023-08-10 18:25:43 1013

1013 當談到該創新工藝時,不可避免地要與傳統的光刻工藝體系進行對比。光刻工藝體系是一種減法工藝:首先要在襯底表面沉積一層材料,例如銅;然后在材料層表面涂布一層光刻膠;接著將光刻膠圖形化曝光并顯影,形成有圖案的光刻覆蓋區域

2023-07-29 11:01:50 835

835

刻蝕和蝕刻實質上是同一過程的不同稱呼,常常用來描述在材料表面上進行化學或物理腐蝕以去除或改變材料的特定部分的過程。在半導體制造中,這個過程常常用于雕刻芯片上的細微結構。

2023-07-28 15:16:59 4140

4140 蝕刻是一種從材料上去除的過程。基片表面上的一種薄膜基片。當掩碼層用于保護特定區域時在晶片表面,蝕刻的目的是“精確”移除未覆蓋的材料戴著面具。

2023-07-14 11:13:32 183

183

蝕刻是一種從材料上去除的過程。基片表面上的一種薄膜基片。當掩碼層用于保護特定區域時在晶片表面,蝕刻的目的是“精確”移除未覆蓋的材料戴著面具。

2023-07-12 09:26:03 190

190

在半導體制程中,移除殘余材料的“減法工藝”不止“刻蝕”一種,引入其他材料的“加法工藝”也非“沉積”一種。比如,光刻工藝中的光刻膠涂敷,其實也是在基底上形成各種薄膜;又如氧化工藝中晶圓(硅)氧化,也需要在基底表面添加各種新材料。那為什么唯獨要強調“沉積”工藝呢?

2023-06-29 16:58:37 404

404

在之前的文章里,我們介紹了晶圓制造、氧化過程和集成電路的部分發展史。現在,讓我們繼續了解光刻工藝,通過該過程將電子電路圖形轉移到晶圓上。光刻過程與使用膠片相機拍照非常相似。但是具體是怎么實現的呢?

2023-06-28 10:07:47 2427

2427

在上一篇文章,我們介紹了光刻工藝,即利用光罩(掩膜)把設計好的電路圖形繪制在涂覆了光刻膠的晶圓表面上。下一步,將在晶圓上進行刻蝕工藝,以去除不必要的材料,只保留所需的圖形。

2023-06-28 10:04:58 843

843

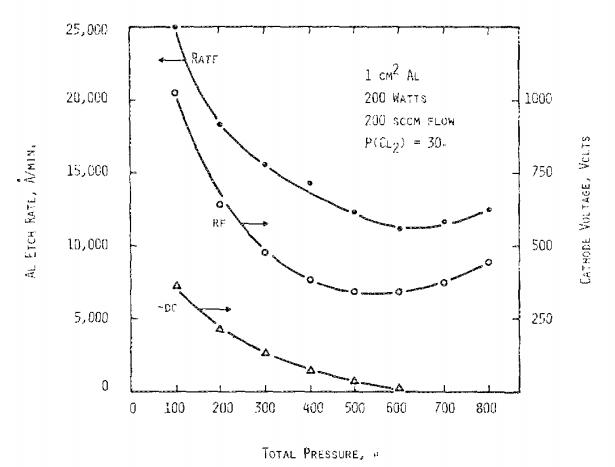

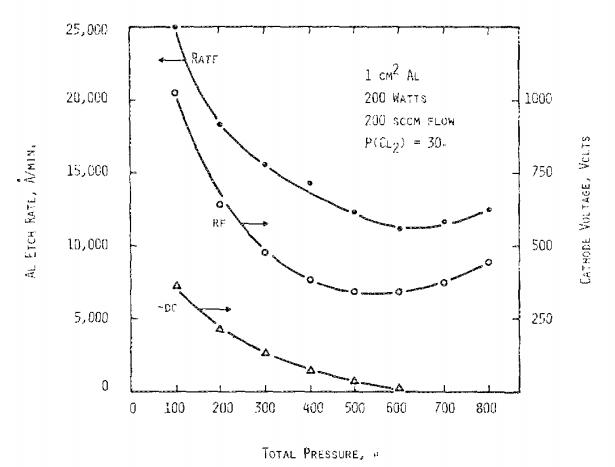

隨著集成電路互連線的寬度和間距接近3pm,鋁和鋁合金的等離子體蝕刻變得更有必要。為了防止蝕刻掩模下的橫向蝕刻,我們需要一個側壁鈍化機制。盡管AlCl和AlBr都具有可觀的蒸氣壓,但大多數鋁蝕刻的研究

2023-06-27 13:24:11 318

318

在介紹日本電子公司研發的全新蝕刻技術之前,我們需要了解蝕刻技術的歷史。蝕刻技術是芯片制造基礎工藝之一,它是指對光刻技術制作的圖案進行蝕刻,得到具有一定幾何形狀和結構的微細孔洞和凹坑的工藝。

2023-06-26 15:58:18 897

897

CMOS和MEMS制造技術,允許相對于其他薄膜選擇性地去除薄膜,在器件集成中一直具有很高的實用性。這種化學性質非常有用,但是當存在其他材料并且也已知在HF中蝕刻時,這就成了問題。由于器件的靜摩擦、緩慢的蝕刻速率以及橫向或分層膜的蝕刻速率降低,濕法化學也會有問題。

2023-06-26 13:32:44 1053

1053

,為什么是10%?為什么不能進一步的把常規控制能力推到8%,甚至5%呢?

從設計上,在《阻抗板是否高可靠,華秋有話說》一文中有提及,由理論公式推導,阻抗與介質厚度、線寬、銅厚、介電常數、阻焊厚度等因素有關,但

2023-06-25 10:25:55

,為什么是10%?為什么不能進一步的把常規控制能力推到8%,甚至5%呢?

從設計上,在《阻抗板是否高可靠,華秋有話說》一文中有提及,由理論公式推導,阻抗與介質厚度、線寬、銅厚、介電常數、阻焊厚度等因素有關,但

2023-06-25 09:57:07

上海伯東日本 Aston? 質譜儀能夠進行準確且可操作的端點檢測, OA% 是傳統 OES 計量解決方案的一個數量級(1/10). Aston? 質譜儀解決方案適用于具有高蝕刻吞吐量和大量重復相同

2023-06-20 17:28:31 258

258

外,學生還就感興趣的課題做深入調研。師生共同討論調研報告,實現教學互動。調研的內容涉及光刻工藝、光刻成像理論、SMO、OPC和DTCO技術。

2023-06-20 10:51:43 335

335

在干法蝕刻中,氣體受高頻(主要為 13.56 MHz 或 2.45 GHz)激發。在 1 到 100 Pa 的壓力下,其平均自由程為幾毫米到幾厘米。

2023-06-20 09:49:16 3689

3689

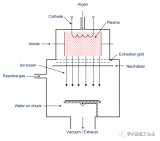

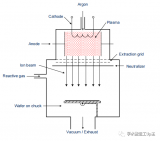

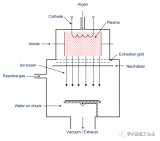

離子束蝕刻 (Ion beam etch) 是一種物理干法蝕刻工藝。由此,氬離子以約1至3keV的離子束輻射到表面上。由于離子的能量,它們會撞擊表面的材料。晶圓垂直或傾斜入離子束,蝕刻過程是絕對

2023-06-20 09:48:56 3989

3989

均勻性(1 σ)達到 離子束刻蝕屬于干法刻蝕, 其核心部件為離子源. 作為蝕刻機的核心部件,?KRi? 射頻離子源提供大尺寸, 高能量, 低濃度的寬束離子束, 接受客戶定制, 單次工藝時間更長, 滿足

2023-06-15 14:58:47 665

665

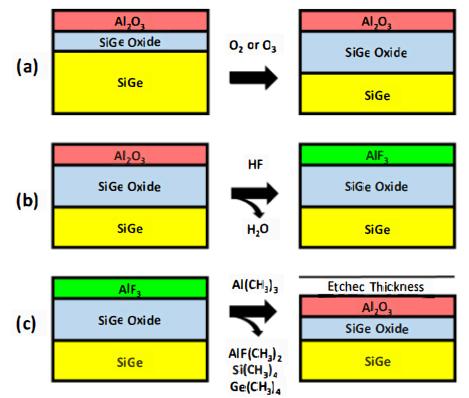

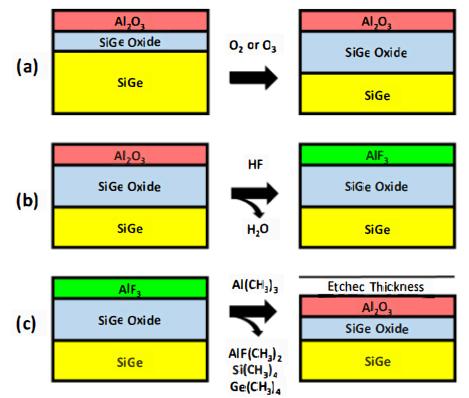

器件尺寸的不斷縮小促使半導體工業開發先進的工藝技術。近年來,原子層沉積(ALD)和原子層蝕刻(ALE)已經成為小型化的重要加工技術。ALD是一種沉積技術,它基于連續的、自限性的表面反應。ALE是一種蝕刻技術,允許以逐層的方式從表面去除材料。ALE可以基于利用表面改性和去除步驟的等離子體或熱連續反應。

2023-06-15 11:05:05 526

526

為了提供更優良的靜電完整性,三維(3D)設計(如全圍柵(GAA)場電子晶體管(FET ))預計將在互補金屬氧化物半導體技術中被采用。3D MOS架構為蝕刻應用帶來了一系列挑戰。雖然平面設備更多地依賴于各向異性蝕刻,但是3D設備在不同材料之間具有高選擇性,需要更多的各向異性蝕刻能力。

2023-06-14 11:03:53 1779

1779

光刻機可分為前道光刻機和后道光刻機。光刻機既可以用在前道工藝,也可以用在后道工藝,前道光刻機用于芯片的制造,曝光工藝極其復雜,后道光刻機主要用于封裝測試,實現高性能的先進封裝,技術難度相對較小。

2023-06-09 10:49:20 5857

5857

光刻工藝后,在硅片或晶圓上形成了光刻膠的圖形,下一步就是刻蝕。

2023-06-08 10:52:35 3320

3320

直接鍍銅陶瓷基板(Direct Plating Copper, DPC)是在陶瓷薄膜工藝加工基礎上發展起來的陶瓷電路加工工藝。以氮化鋁/氧化鋁陶瓷作為線路的基板,采用濺鍍工藝于基板表面復合金屬層,并以電鍍和光刻工藝形成電路。

2023-05-31 10:32:02 1587

1587

等離子體蝕刻是氮化鎵器件制造的一個必要步驟,然而,載體材料的選擇可能會實質上改變蝕刻特性。在小型單個芯片上制造氮化鎵(GaN)設備,通常會導致晶圓的成本上升。在本研究中,英思特通過鋁基和硅基載流子來研究蝕刻過程中蝕刻速率、選擇性、形貌和表面鈍化的影響。

2023-05-30 15:19:54 452

452

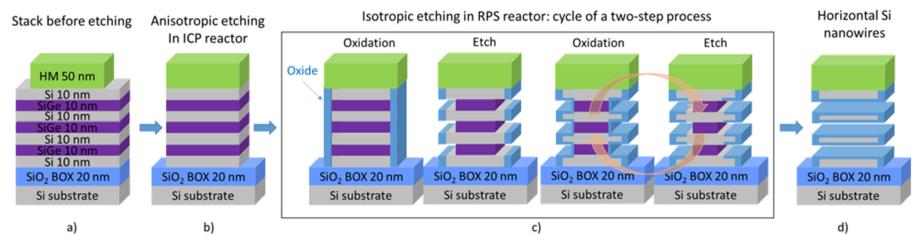

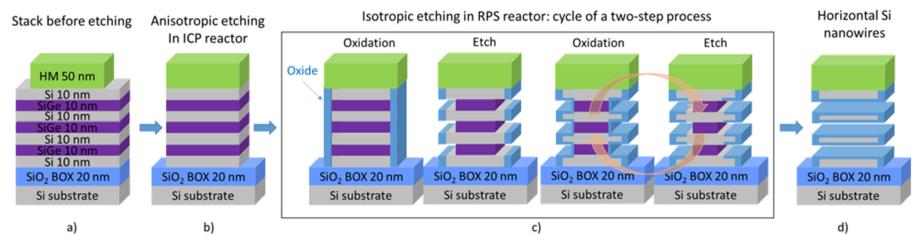

納米片工藝流程中最關鍵的蝕刻步驟包括虛擬柵極蝕刻、各向異性柱蝕刻、各向同性間隔蝕刻和通道釋放步驟。通過硅和 SiGe 交替層的剖面蝕刻是各向異性的,并使用氟化化學。優化內部間隔蝕刻(壓痕)和通道釋放步驟,以極低的硅損失去除 SiGe。

2023-05-30 15:14:11 1071

1071

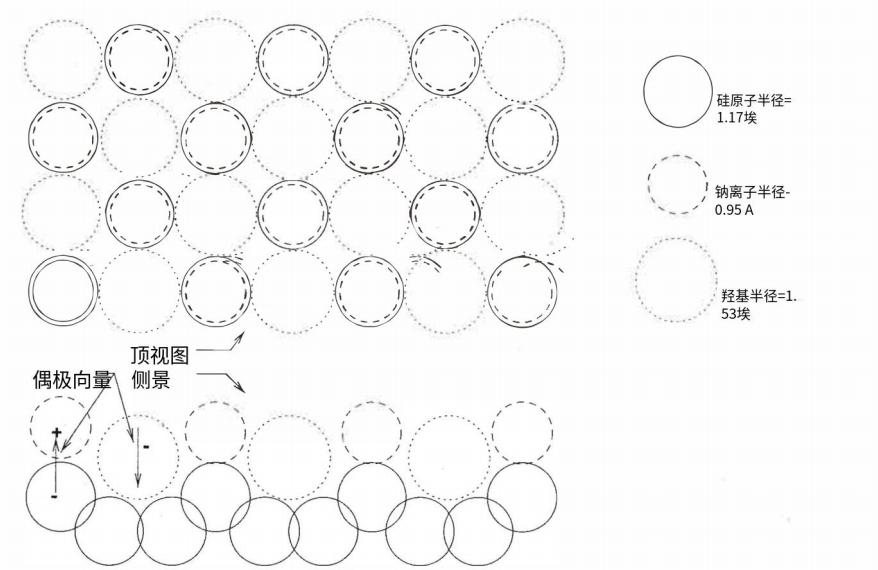

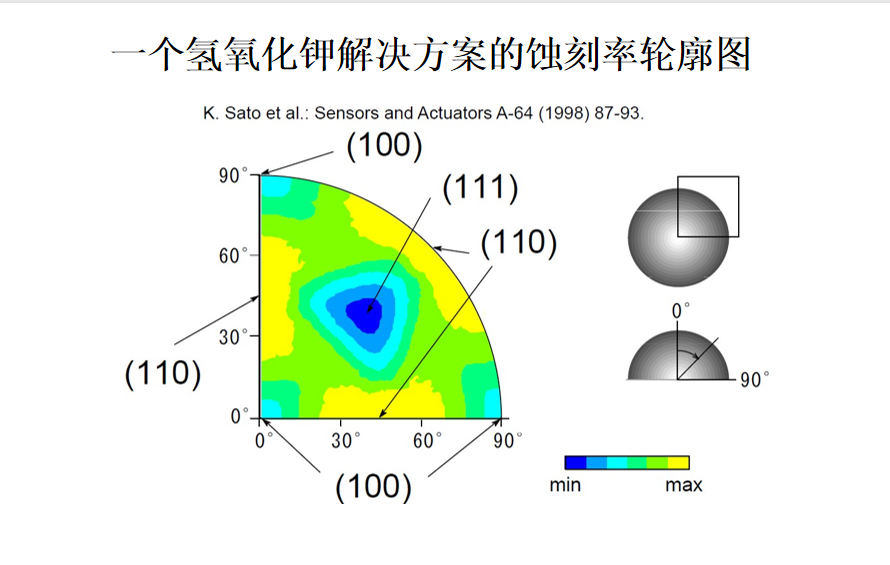

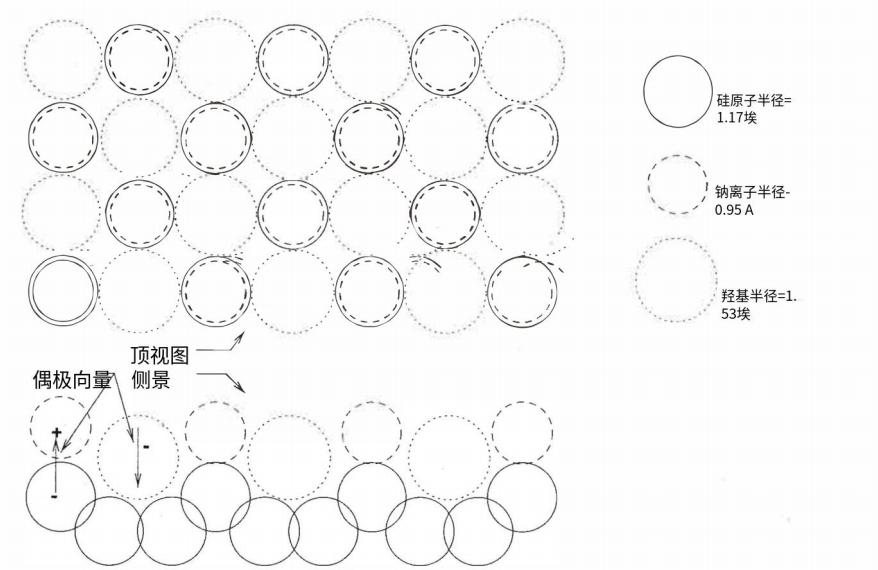

過去利用堿氫氧化物水溶液研究了硅的取向依賴蝕刻,這是制造硅中微結構的一種非常有用的技術。以10M氫氧化鉀(KOH)為蝕刻劑,研究了單晶硅球和晶片的各向異性蝕刻過程,測量了沿多個矢量方向的蝕刻速率,用單晶球發現了最慢的蝕刻面。英思特利用這些數據,提出了一種預測不同方向表面的傾角的方法

2023-05-29 09:42:40 618

618

蝕刻可能是濕制程階段最復雜的工藝,因為有很多因素會影響蝕刻速率。如果不保持這些因素的穩定,蝕刻率就會變化,因而影響產品質量。如果希望利用一種自動化方法來維護蝕刻化學,以下是你需要理解的基本概念。

2023-05-19 10:27:31 575

575

微電子機械系統(MEMS)是將機械元件和電子電路集成在一個共同的基板上,通過使用微量制造技術來實現尺寸從小于一微米到幾微米的高性能器件。由于現有的表面加工技術,目前大多數的MEMS器件都是基于硅的。

2023-05-19 10:19:26 352

352 一般適用于多層印制板的外層電路圖形的制作或微波印制板陰板法直接蝕刻圖形的制作抗蝕刻 圖形電鍍之金屬抗蝕層如鍍覆金、鎳、錫鉛合金

2023-05-18 16:23:48 4918

4918 蝕刻是微結構制造中采用的主要工藝之一。它分為兩類:濕法蝕刻和干法蝕刻,濕法蝕刻進一步細分為兩部分,即各向異性和各向同性蝕刻。硅濕法各向異性蝕刻廣泛用于制造微機電系統(MEMS)的硅體微加工和太陽能電池應用的表面紋理化。

2023-05-18 09:13:12 700

700

拋光硅晶片是通過各種機械和化學工藝制備的。首先,硅單晶錠被切成圓盤(晶片),然后是一個稱為拍打的扁平過程,包括使用磨料清洗晶片。通過蝕刻消除了以往成形過程中引起的機械損傷,蝕刻之后是各種單元操作,如拋光和清洗之前,它已經準備好為設備制造。

2023-05-16 10:03:00 584

584

其實不同顏色的PCB,它們的制造的材料、制造工序都是一樣的,包括敷銅層的位置也是一樣的,經過蝕刻工藝后就在PCB上留下了最終的布線,例如下圖這塊剛經過蝕刻工藝的PCB,敷銅走線就是原本的銅色,而PCB基板略顯微黃色。

2023-05-09 10:02:43 1699

1699

成本上講,化學鍍鎳/金工藝(Et.Ni5.Au0.1)比噴錫貴,而整板鍍金工藝則比噴錫便宜。

4)對印制插頭,一般鍍硬金,即純度為99.5%-99.7%含鎳、鉆的金合金。一般厚度為0.5

2023-04-25 16:52:12

一、傳統工藝品制作煥發生機,3D掃描技術帶來生產工藝革新 傳統工藝美術是老百姓在日常生活和勞作中的精神提煉與藝術創作的具體體現。而雕刻便是傳統工藝美術的具體表現之一。傳統的雕刻工藝包括木雕、浮雕

2023-04-25 13:04:47 375

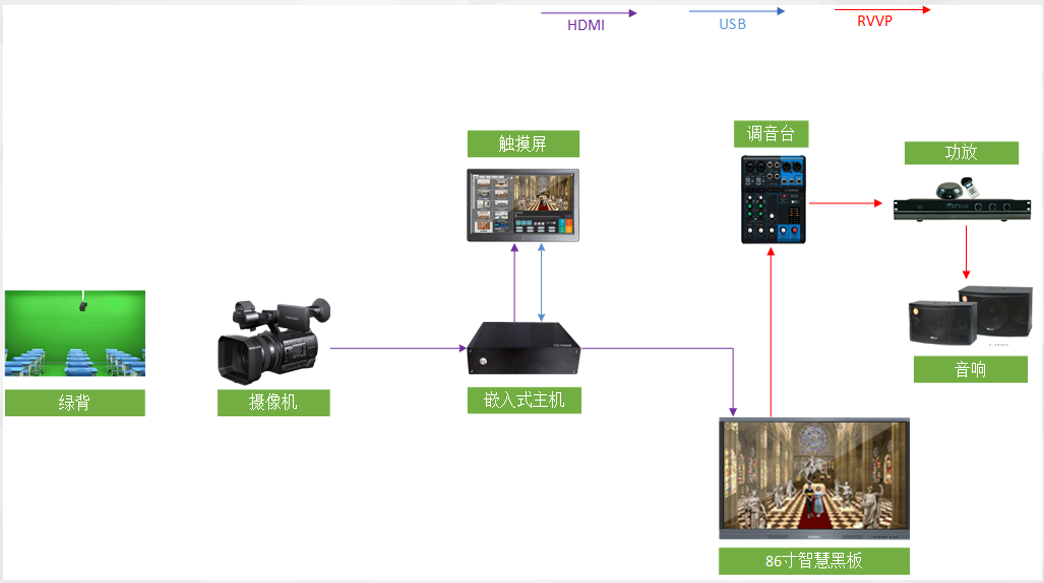

375 現代教育改革不斷深化,加之移動信息技術的不斷成熟發展,信息化技術+教育是成為建設數字化教育,實現教育高質發展的重要推動力量。為適應現代高校教學需求,改善教學體系,提高課堂教學質量, 游課堂嵌入式情景

2023-04-25 10:10:18 449

449

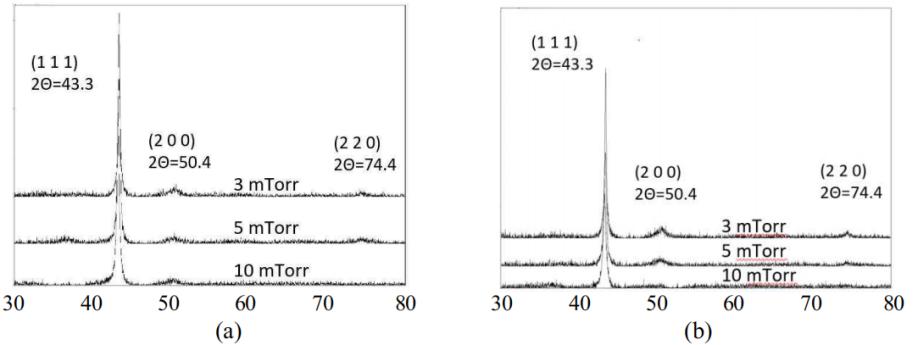

書籍:《炬豐科技-半導體工藝》 文章:單晶的濕法蝕刻和紅外吸收 編號:JFKJ-21-206 作者:炬豐科技 摘要 采用濕法腐蝕、x射線衍射和紅外吸收等方法研究了物理氣相色譜法生長AlN單晶的缺陷

2023-04-23 11:15:00 118

118 PCB制程中的COB工藝是什么呢?

2023-04-23 10:46:59

及鋼的蝕刻劑。它適用于絲網漏印油墨、液體光致抗蝕劑和鍍金印制電路版電路圖形的蝕刻。用三氯化鐵為蝕刻劑的蝕刻工藝流程如下: 預蝕刻檢查→蝕刻→水洗→浸酸處理→水洗→干燥→去抗蝕層→熱水洗→水沖洗

2023-04-20 15:25:28

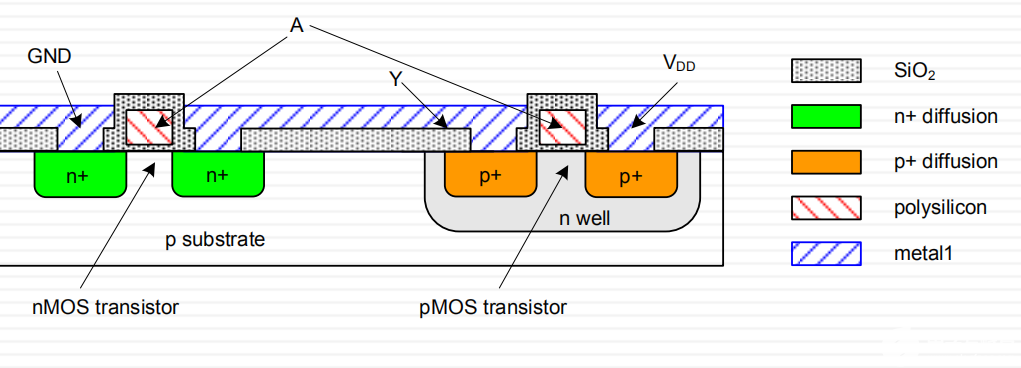

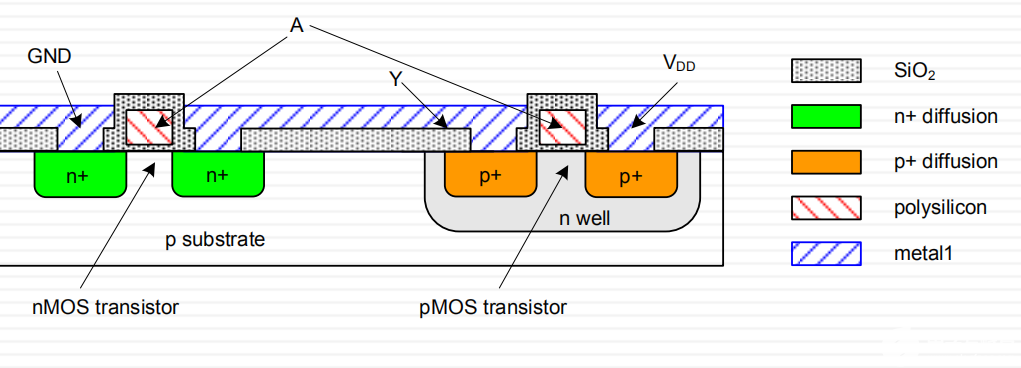

半導體工藝 1.CMOS晶體管是在硅片上制造的 ? 2.平版印刷的過程類似于印刷機 ? 3.每一步,不同的材料被存放或蝕刻 ? 4.通過查看頂部和頂部最容易理解文章全部詳情:壹叁叁伍捌零陸肆叁叁叁簡化制造中的晶圓截面的過程 ? 逆變器截面?? 要求pMOS晶體管的機身 ? 逆變器掩模組 晶體管

2023-04-20 11:16:00 247

247

那時集成電路也剛剛發明不久,光刻工藝還在微米級別,工藝步驟也比現在簡單很多美國是走在世界前列的。在那個對工藝要求并不高的年代,很多半導體公司通常自己用鏡頭設計光刻工具,光刻機在當時甚至不如照相機的結構復雜。

2023-04-20 09:22:33 1314

1314 反應離子蝕刻 (RIE)是一種干法蝕刻工藝,與半導體工業中使用的互補金屬氧化物半導體(CMOS)方法兼容。

2023-04-14 14:26:16 1253

1253

新的High NA EUV 光刻膠不能在封閉的研究環境中開發,必須通過精心設計的底層、新型硬掩模和高選擇性蝕刻工藝進行優化以獲得最佳性能。為了迎接這一挑戰,imec 最近開發了一個新的工具箱來匹配光刻膠和底層的屬性。

2023-04-13 11:52:12 1164

1164 干法蝕刻與濕法蝕刻之間的爭論是微電子制造商在項目開始時必須解決的首要問題之一。必須考慮許多因素來決定應在晶圓上使用哪種類型的蝕刻劑來制作電子芯片,是液體(濕法蝕刻)還是氣體(干法蝕刻)

2023-04-12 14:54:33 1004

1004 濕法蝕刻工藝的原理是使用化學溶液將固體材料轉化為液體化合物。選擇性非常高

2023-04-10 17:26:10 453

453

基于**混合現實仿真模擬技術的新型商務英語課堂教學模式,突破了傳統的商務英語課堂教學中“以教師為中心”的傳統授課方式,充分調動了學生在學習過程中的積極性,激發了學生對知識學習的興趣,提高了學生

2023-04-06 13:52:04 466

466 半導體行業的許多工藝步驟都會排放有害廢氣。對于使用非常活潑的氣體的化學氣相沉積或干法蝕刻,所謂的靠近源頭的廢氣使用點處理是常見的做法。相比之下,對于濕法化學工藝,使用中央濕式洗滌器處理廢氣是一種公認

2023-04-06 09:26:48 408

408

了革命性的變化,這種布局完全不同于90nm節點。從45nm節點后,雙重圖形化技術已經應用在柵圖形化工藝中。隨著技術節點的繼續縮小,MOSFET柵極關鍵尺寸CD繼續縮小遇到了困難,IC設計人員開始減少柵極之間的間距。

2023-04-03 09:39:40 2452

2452 經過多年的研發,隨著該行業在內存和邏輯方面面臨新的挑戰,一種稱為低溫蝕刻的技術正在重新出現,成為一種可能的生產選擇。

2023-03-29 10:14:41 392

392

印刷線路板從光板到顯出線路圖形的過程是一個比較復雜的物理和化學反應的過程,本文就對其最后的一步--蝕刻進行解析。目前,印刷電路板(PCB)加工的典型工藝采用"圖形電鍍法"。即先在

2023-03-29 10:04:07 886

886 研究表明,半導體的物理特性會根據其結構而變化,因此半導體晶圓在組裝成芯片之前被蝕刻成可調整其電氣和光學特性以及連接性的結構。

2023-03-28 09:58:34 251

251

在濕蝕刻的情況下,隨著SiNx/SiOy層的厚度減小,剩余的SiOy層由于表面張力而坍塌,蝕刻溶液對孔的滲透變得更具挑戰性。

2023-03-27 10:17:49 402

402

(Packaging)二. 多層板工藝流程:內層覆銅板(CCL)銅箔(Copper Foil)下料(Cut)→內層圖形制作(Inner-layer Pattern)→內層蝕刻(Inner-layer Etch

2023-03-24 11:24:22

電子發燒友App

電子發燒友App

硬聲App

硬聲App

823

823

62

62

109

109 306

306

163

163 326

326

371

371

294

294

188

188

250

250

263

263 1536

1536 1335

1335

259

259

166

166

434

434

241

241

217

217 146

146

188

188

475

475

788

788

164

164

553

553 319

319

281

281

670

670 290

290 472

472

474

474

292

292

811

811

1586

1586

239

239

370

370

1013

1013 835

835

4140

4140 183

183

190

190

404

404

2427

2427

843

843

318

318

897

897

1053

1053

258

258

335

335

3689

3689

3989

3989

665

665

526

526

1779

1779

5857

5857

1587

1587

452

452

1071

1071

618

618

575

575

352

352 700

700

584

584

1699

1699

375

375 449

449

118

118 247

247

1314

1314 1164

1164 1004

1004 466

466 408

408 2452

2452 886

886 402

402

評論