S2C Inc.今日宣布將最新的原型驗(yàn)證平臺(tái)Quad V7加入其V7 TAI Logic Module系列。Quad V7 是基于Xilinx Virtex-7 2000T可編程3D IC的最新一代SoC/ASIC原型硬件。

2013-01-23 11:28:14 2068

2068 基于 FPGA 的 ASIC 原型可快速、準(zhǔn)確地實(shí)現(xiàn) SoC 系統(tǒng)建模和驗(yàn)證并加速軟件和固件的開發(fā)。Xilinx 推出Virtex?-7 2000T 器件,使基于 FPGA 的原型得到了進(jìn)一步發(fā)展

2013-03-14 14:33:00 1269

1269

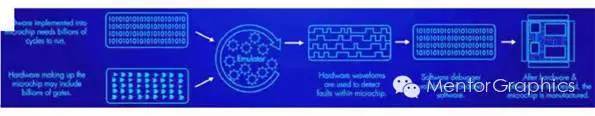

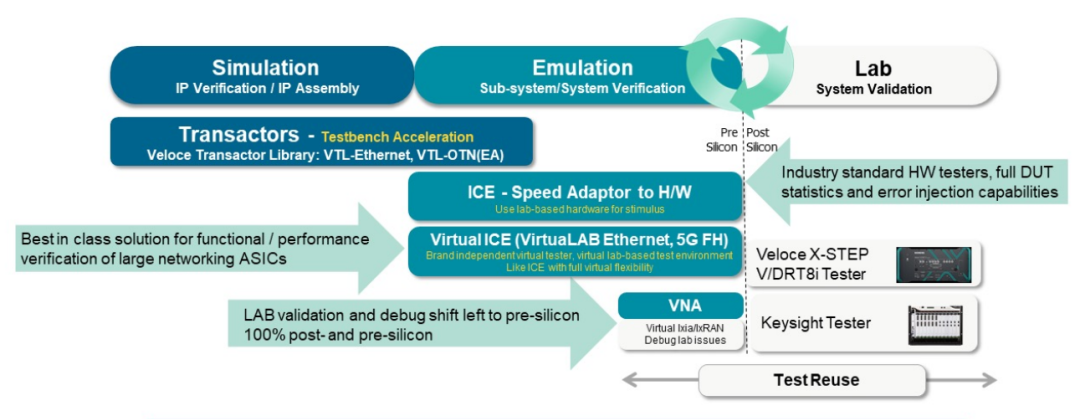

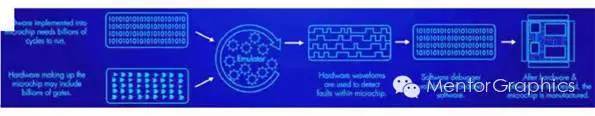

傳統(tǒng)的模擬工具已難以應(yīng)付日趨復(fù)雜的芯片設(shè)計(jì),這導(dǎo)致市場(chǎng)上對(duì)于能加速驗(yàn)證及除錯(cuò)流程的硬件仿真器需求持續(xù)攀升。明導(dǎo)國(guó)際Veloce平臺(tái)憑借其獨(dú)特的優(yōu)勢(shì)居于硬件仿真器市場(chǎng)領(lǐng)導(dǎo)地位...

2013-11-26 09:33:06 2037

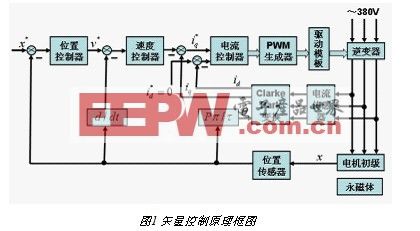

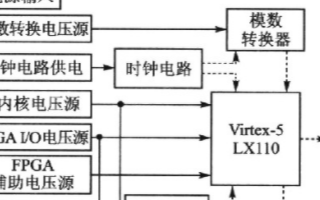

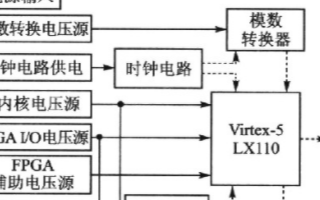

2037 在系統(tǒng)設(shè)計(jì)中,硬件復(fù)雜電路設(shè)計(jì)的調(diào)試與仿真工作對(duì)于設(shè)計(jì)者來(lái)說十分困難。為了降低仿真復(fù)雜度,加快仿真速度,本文提出利用FPGA加速的思想,實(shí)現(xiàn)軟硬件協(xié)同加速仿真。經(jīng)過實(shí)驗(yàn),相對(duì)于純軟件仿真,利用軟硬件協(xié)同加速仿真技術(shù),仿真速度提高近30倍,大大縮短了仿真時(shí)間。##仿真實(shí)例及結(jié)論

2014-03-25 11:52:52 4722

4722 在驗(yàn)證領(lǐng)域,虛擬探針增強(qiáng)了硬件加速仿真作為數(shù)據(jù)中心資源對(duì)硬件設(shè)計(jì)人員和軟件開發(fā)人員的吸引力。

2017-08-18 10:39:15 1841

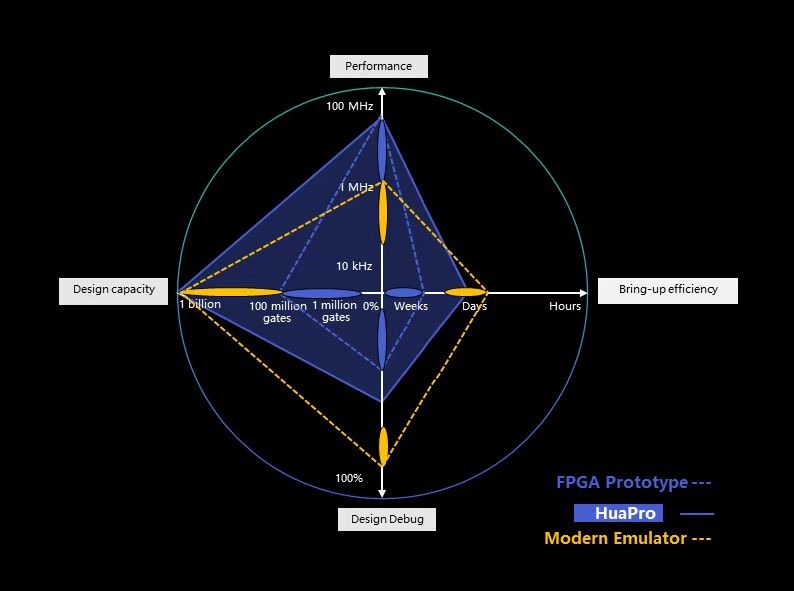

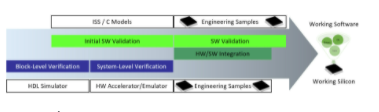

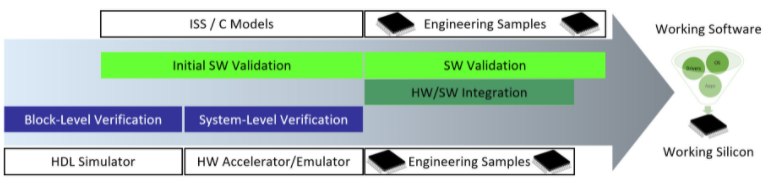

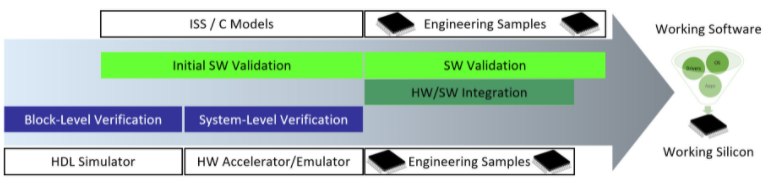

1841 軟件仿真(Simulation),原型驗(yàn)證(Prototyping),以及硬件仿真(Emulation),是當(dāng)前主要的三種有效的驗(yàn)證方法,在芯片前端設(shè)計(jì)的功能性驗(yàn)證階段起到了關(guān)鍵的作用。近年來(lái),由于

2023-07-31 23:16:05 415

415

兩方面的需求,解決了原型驗(yàn)證與硬件仿真兩種驗(yàn)證工具的融合平衡難題,是硬件驗(yàn)證系統(tǒng)的一次重大突破性創(chuàng)新,將極大助力軟硬件協(xié)同開發(fā),賦能大規(guī)模復(fù)雜系統(tǒng)應(yīng)用創(chuàng)新。 新產(chǎn)品亮相 統(tǒng)一的硬件仿真與原型驗(yàn)證系統(tǒng) 不斷發(fā)展的SoC和Chiplet芯片創(chuàng)新,使芯片

2022-12-02 17:01:44 1117

1117

的費(fèi)用持續(xù)上升。一次失敗的ASIC流片將會(huì)推遲數(shù)個(gè)月的上市時(shí)間。誰(shuí)愿意承擔(dān)簽字的責(zé)任呢? 一些BUG通過仿真和Emulation是抓不到的。傳統(tǒng)的驗(yàn)證方法認(rèn)為設(shè)計(jì)的功能符合功能定義就是對(duì)的。 但功能定義到底對(duì)不對(duì)呢?唯一的辦法就是建立一個(gè)真實(shí)的硬件:原型。

2019-07-11 08:19:24

講的很好,主要講解了廠商A和X兩個(gè)高端驗(yàn)證平臺(tái)。電子版,可以看看(中文)

2015-08-25 14:14:18

1ASIC 驗(yàn)證技術(shù).................................................11.1 ASIC 設(shè)計(jì)流程

2015-09-18 15:26:25

ASIC設(shè)計(jì)-FPGA原型驗(yàn)證

2020-03-19 16:15:49

Veloce Apps庫(kù),以引入新方式確保其設(shè)計(jì)能如期完成并滿足其功能和性能規(guī)范。Veloce OS操作系統(tǒng)為Veloce平臺(tái)增加了軟件可編程性和資源管理,使其更容易添加可提高硬件仿真加速器投資回報(bào)(ROI

2016-04-15 16:25:55

Graphics公司Veloce驗(yàn)證平臺(tái)在超大規(guī)模IC系統(tǒng)中仿真驗(yàn)證的應(yīng)用。借助Veloce的高速和大容量的特性,極大的提高功能驗(yàn)證的效率,解決由于芯片規(guī)模大FPGA無(wú)法驗(yàn)證的問題,保證芯片的按時(shí)投片

2010-05-28 13:41:35

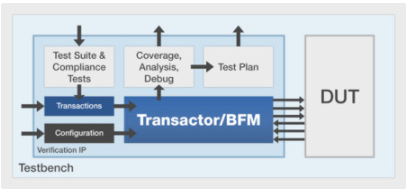

是項(xiàng)目周期驗(yàn)證部分的唯一工作,此作業(yè)由硬件描述語(yǔ)言 (HDL) 測(cè)試平臺(tái)驅(qū)動(dòng)的邏輯軟件仿真進(jìn)行管理。傳統(tǒng)的大箱式硬件仿真只用于最大型的設(shè)計(jì)。很多開發(fā)團(tuán)隊(duì)已采用正式驗(yàn)證對(duì)軟件仿真進(jìn)行補(bǔ)充,以增加基礎(chǔ)覆蓋范圍

2017-08-21 10:00:36

和語(yǔ)法糖化。它廣泛用于硬件設(shè)計(jì)和驗(yàn)證行業(yè),其中形式驗(yàn)證工具(例如模型檢查)和/或邏輯仿真工具用于證明或反駁給定 PSL 公式適用于給定設(shè)計(jì)。 PSL 最初由 Accellera 開發(fā),用于指定有關(guān)硬件

2022-02-16 13:36:53

ASIC的驗(yàn)證和調(diào)試需要更復(fù)雜的工具和技術(shù)。

應(yīng)用領(lǐng)域 :FPGA廣泛應(yīng)用于原型驗(yàn)證、信號(hào)處理、圖像處理、網(wǎng)絡(luò)加速等領(lǐng)域。ASIC則適用于需要高性能、低功耗的應(yīng)用,如移動(dòng)設(shè)備、嵌入式系統(tǒng)等。

2024-02-22 09:54:36

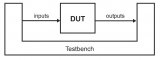

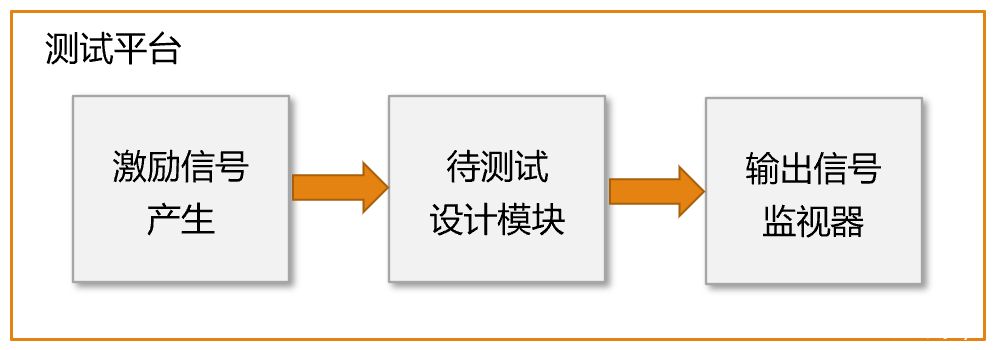

重來(lái)。因此,仿真在整個(gè)驗(yàn)證中的重要性可見一斑。(特權(quán)同學(xué),版權(quán)所有)提到仿真,我們通常會(huì)提t(yī)estbench的概念。所謂testbench,即測(cè)試平臺(tái),詳細(xì)的說就是給待驗(yàn)證的設(shè)計(jì)添加激勵(lì),同時(shí)觀察它

2019-04-10 06:35:34

FPGA_HW_SIM_FWK- FPGA硬件仿真框架 Python作為最流行的編程語(yǔ)言是硬件驗(yàn)證語(yǔ)言(HVL)的自然選擇,特別是對(duì)于IC設(shè)計(jì)領(lǐng)域的新人來(lái)說,他們對(duì)SystemVerilog、Verilog、SystemC、e

2022-11-03 13:07:24

SoC芯片的規(guī)模一般遠(yuǎn)大于普通的ASIC,同時(shí)深亞微米工藝帶來(lái)的設(shè)計(jì)困難等使得SoC設(shè)計(jì)的復(fù)雜度大大提高。仿真與驗(yàn)證是SoC設(shè)計(jì)流程中最復(fù)雜、最耗時(shí)的環(huán)節(jié),約占整個(gè)芯片開發(fā)周期的50%~80%,采用

2019-10-11 07:07:07

SoC驗(yàn)證超越了常規(guī)邏輯仿真,但用于加速SoC驗(yàn)證的廣泛應(yīng)用的三種備選方法不但面臨可靠性問題,而且難以進(jìn)行權(quán)衡。而且,最重要的問題還在于硬件加速訪問權(quán)限、時(shí)機(jī)及其穩(wěn)定性。

2019-11-11 06:37:11

易用、綜合而全面的全速ASIC/ASSP驗(yàn)證工作流程,能顯著加速ASIC、ASSP以及SoC設(shè)計(jì)的功能驗(yàn)證。Confirma平臺(tái)包括Certify多FPGA實(shí)施工具、HAPS以及采用

2018-11-20 15:49:49

機(jī)的協(xié)商,保持接口參數(shù)同步;數(shù)據(jù)通道驗(yàn)證在該接口參數(shù)下的功能和性能,實(shí)現(xiàn)了接口的功能和性能驗(yàn)證的自動(dòng)化,大大提高了測(cè)試效率,保證測(cè)試用例的覆蓋率。該工具適用于多種平臺(tái)下的UART和SPI接口驗(yàn)證。0

2019-06-21 05:00:09

目前我使用NI的機(jī)箱采集數(shù)據(jù),labview做軟件平臺(tái)生成一個(gè)系統(tǒng)。想要達(dá)到實(shí)時(shí)性效果。能否給NI或labview采用硬件加速,提高處理速的呢?如何做呢?有什么資料可以參考?

2018-09-29 09:34:24

【招聘】射頻/模擬、ASIC設(shè)計(jì)/驗(yàn)證、系統(tǒng)、模擬設(shè)計(jì)等 射頻集成電路工程師(TRX 方向)-BJ 射頻/模擬集成電路工程師(RF/Analog IC Engineer)-BJ 射頻IC工程師

2017-03-03 14:54:37

ASIC做原型驗(yàn)證(Prototyping)的。不可否認(rèn),原型驗(yàn)證仍然是FPGA的一個(gè)重大市場(chǎng)。 在AI應(yīng)用中,除了對(duì)RTL code的功能驗(yàn)證和高速仿真外,F(xiàn)PGA Prototyping對(duì)于產(chǎn)品

2023-03-28 11:14:04

職位描述:1.負(fù)責(zé)我司數(shù)據(jù)通信產(chǎn)品的FPGA和ASIC應(yīng)用的仿真驗(yàn)證工作; 2.著重負(fù)責(zé)仿真驗(yàn)證平臺(tái)系統(tǒng)的搭建和仿真驗(yàn)證方法的引進(jìn); 3.編寫各種設(shè)計(jì)文檔和標(biāo)準(zhǔn)化資料,實(shí)現(xiàn)資源、經(jīng)驗(yàn)共享。 任職要求

2015-07-16 11:04:49

SystemC和SystemVerilog在設(shè)計(jì)中的地位問題,我認(rèn)為在驗(yàn)證方面,SystemC有明顯的優(yōu)勢(shì)。如果你設(shè)計(jì)純粹的ASIC,那么用SystemVerilog可能就足夠了。但是在很多場(chǎng)合,軟硬件同時(shí)存在

2012-03-01 11:30:19

工程師(在印度諾伊達(dá)同事支持之下)的最近經(jīng)歷表明,事情可能在變化。更具體地講,將運(yùn)行于軟件仿真器上的驗(yàn)證平臺(tái)和運(yùn)行于硬件仿真器的設(shè)計(jì)進(jìn)行聯(lián)調(diào)是可行的,從而充分利用兩個(gè)驗(yàn)證平臺(tái)的價(jià)值。構(gòu)建參考設(shè)計(jì),促進(jìn)

2017-04-05 14:17:46

本文提出了一種基于FPGA的NoC驗(yàn)證平臺(tái)。詳細(xì)討論了該驗(yàn)證平臺(tái)中FPGA硬件平臺(tái)和NoC軟件的基本功能,并闡述了TG/R,MPU,MPI以及NoC軟件的可重用性等特點(diǎn)。通過一個(gè)實(shí)例仿真驗(yàn)證的結(jié)果說明了該驗(yàn)證平臺(tái)的基本功能和優(yōu)越性。

2021-05-06 07:20:48

電子硬件設(shè)計(jì)仿真:批量驗(yàn)證神器 雖然摩爾定律進(jìn)行了三次修改:現(xiàn)在規(guī)定約兩年內(nèi)使集成電路中的晶體管數(shù)目增加一倍,但趨勢(shì)是設(shè)計(jì)/器件會(huì)繼續(xù)變得越來(lái)越大。如今,平均設(shè)計(jì)尺寸達(dá)到或超過 5,000 萬(wàn)

2015-04-15 20:10:45

、強(qiáng)大的操作和顯示方法,讓用戶能夠從更多角度查看電路工作情況,同時(shí)使得使用方法更加簡(jiǎn)單。 針對(duì)這些需求,圣景微電子開發(fā)了Matrix Stimuli這個(gè)通用仿真驗(yàn)證平臺(tái),它將數(shù)字電路、模擬電路的仿真

2012-04-27 14:33:36

在設(shè)計(jì)、仿真、開發(fā)、調(diào)試、測(cè)試、集成驗(yàn)證和維護(hù)等各階段配置項(xiàng)級(jí)別和系統(tǒng)級(jí)別的動(dòng)態(tài)測(cè)試與驗(yàn)證。ETest提供了針對(duì)嵌入式系統(tǒng)的半實(shí)物硬件在環(huán)仿真測(cè)試環(huán)境,通過模擬待測(cè)系統(tǒng)的外部環(huán)境并產(chǎn)生信號(hào)輸入到待

2021-12-21 06:37:13

。基于FPGA的原型驗(yàn)證方法憑借其速度快、易修改、真實(shí)性的特點(diǎn),已經(jīng)成為ASIC芯片設(shè)計(jì)中重要的驗(yàn)證方法。本文主要描述高頻RFID芯片的FPGA原型驗(yàn)證平臺(tái)的設(shè)計(jì),并給出驗(yàn)證結(jié)果。1、RFID芯片的FPGA

2019-05-29 08:03:31

摘要:在芯片規(guī)模指數(shù)式上升和要求面市時(shí)間快速縮短的雙重壓力下,驗(yàn)證已成為數(shù)字集成電路設(shè)計(jì)的瓶頸。利用硬件加速驗(yàn)證技術(shù)能很好地解決這一問題。該文論述了硬件加速驗(yàn)

2010-04-26 10:20:15 16

16 摘要:在ASIC設(shè)計(jì)中首先重要的就是要對(duì)系統(tǒng)進(jìn)行邏輯功能驗(yàn)證,確保系統(tǒng)功能的正確。本文介紹了一個(gè)基于MentorGraphics公司仿真工具M(jìn)odelsim和Mathworks公司的Matlab構(gòu)建的平臺(tái)對(duì)指紋識(shí)別

2010-06-08 08:43:15 28

28 平臺(tái)ASIC架構(gòu)突破傳統(tǒng)ASIC設(shè)計(jì)局限性

采用先進(jìn)半導(dǎo)體工藝,結(jié)構(gòu)化ASIC平臺(tái)可以提供更多經(jīng)預(yù)定義、預(yù)驗(yàn)證和預(yù)擴(kuò)散的金屬層,并支持各種存儲(chǔ)器接口,能簡(jiǎn)化接口設(shè)計(jì)

2009-12-27 13:33:33 1146

1146

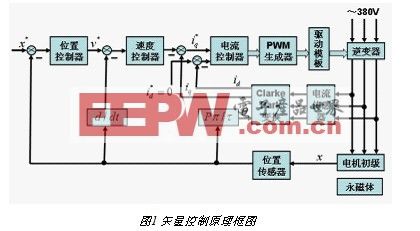

永磁同步直線電機(jī)硬件在環(huán)實(shí)時(shí)仿真平臺(tái)

挑戰(zhàn):采用LabView8.6.1和兩個(gè)cRIO軟硬件平臺(tái)快速搭建一套永磁同步直線電機(jī)硬件在環(huán)實(shí)時(shí)仿真系統(tǒng)。

2010-05-13 10:24:07 2168

2168

對(duì)ASIC設(shè)計(jì)進(jìn)行FPGA原型驗(yàn)證時(shí),由于物理結(jié)構(gòu)不同,ASIC的代碼必須進(jìn)行一定的轉(zhuǎn)換后才能作為FPGA的輸入。 現(xiàn)代集成電路設(shè)計(jì)中,芯片的規(guī)模和復(fù)雜度正呈指數(shù)增加。尤其在ASIC設(shè)計(jì)流程中

2011-03-25 15:16:20 108

108 針對(duì)數(shù)字信號(hào)處理器的不同仿真和驗(yàn)證要求,提出了一種可測(cè)性軟硬件協(xié)同仿真和驗(yàn)證平臺(tái)的設(shè)計(jì). 采用可配置IP 模塊和總線結(jié)構(gòu),實(shí)現(xiàn)了硬件平臺(tái)可配置性和可重用性;采用在線仿真模塊

2011-06-09 17:54:21 39

39 基于動(dòng)態(tài)的RTL仿真依然是驗(yàn)證超大規(guī)模集成電路的主要方法 在使用動(dòng)態(tài)仿真方法對(duì)通用微處理器這樣大規(guī)模的設(shè)計(jì)進(jìn)行功能驗(yàn)證時(shí)仿真速度成為了瓶頸#通常的解決方案是使用:.? 進(jìn)行硬

2011-06-28 17:09:13 40

40 本文基于PXI和cRIO搭建了ESP硬件在環(huán)仿真平臺(tái)。平臺(tái)可以將控制器放在仿真回路中,方便對(duì)控制器中的算法進(jìn)行測(cè)試。仿真試驗(yàn)臺(tái)的搭建提高了ESP控制算法的開發(fā)速度。

2011-08-26 10:31:27 6238

6238

本文描述ASIC驗(yàn)證方法和過程,有助于ASIC設(shè)計(jì)者對(duì)驗(yàn)證的認(rèn)識(shí)。模擬是驗(yàn)證ASIC并產(chǎn)生測(cè)試矢量的唯一途徑,設(shè)計(jì)者可以對(duì)ASIC芯片或者在ASIC應(yīng)用系統(tǒng)中進(jìn)行功能和時(shí)序模擬。

2012-05-24 09:32:47 23

23 本文描述ASIC驗(yàn)證方法和過程,有助于ASIC設(shè)計(jì)者對(duì)驗(yàn)證的認(rèn)識(shí)。模擬是驗(yàn)證ASIC并產(chǎn)生測(cè)試矢量的唯一途徑,設(shè)計(jì)者可以對(duì)ASIC芯片或者在ASIC應(yīng)用系統(tǒng)中進(jìn)行功能和時(shí)序模擬。

2012-05-24 09:32:47 27

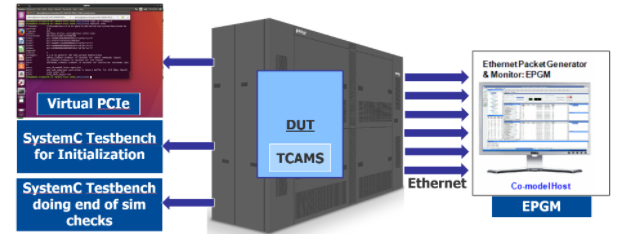

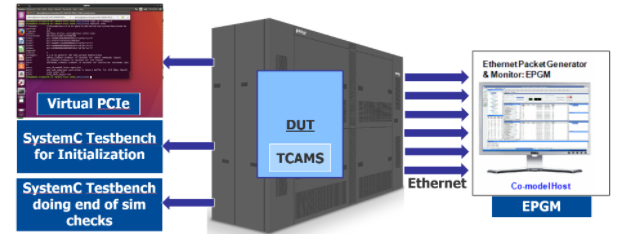

27 Mentor Graphics公司(納斯達(dá)克代碼:MENT)今天宣布推出支持 25G、50G 和 100G 以太網(wǎng)的 Veloce? VirtuaLAB 以太網(wǎng)環(huán)境。這種支持可為目前基于大規(guī)模以太網(wǎng)的設(shè)計(jì)提供高效、基于硬件仿真的驗(yàn)證。

2015-10-30 14:49:27 777

777 ? (EVP) 上提供,設(shè)計(jì)人員在使用 Questa? 仿真軟件和 Veloce? 硬件仿真器對(duì)采用此新規(guī)范的芯片設(shè)計(jì)進(jìn)行驗(yàn)證時(shí),可利用它簡(jiǎn)化并加快驗(yàn)證流程。

2015-11-12 11:28:11 1132

1132 Technologies在其一款支持光線追蹤技術(shù)的圖形處理器 (GPU) PowerVR Wizard GR6500 的內(nèi)部驗(yàn)證流程中,部署了 Veloce? 硬件仿真平臺(tái)的虛擬測(cè)試平臺(tái)加速 (TBX) 技術(shù)。

2015-12-21 16:41:09 1429

1429 俄勒岡州威爾遜維爾,2016 年 2 月 25 日 – Mentor Graphics公司(納斯達(dá)克代碼:MENT)今天宣布,推出用于 Veloce? 硬件仿真平臺(tái)的新型應(yīng)用程序,自此開辟了硬件仿真

2016-02-26 17:50:35 1068

1068 2016 年 3 月 1 日 ─Imagination Technologies 和明導(dǎo)國(guó)際(Mentor Graphics)宣布,雙方已就硬件模擬(emulation)技術(shù)展開合作,以協(xié)助共同客戶加速產(chǎn)品的上市時(shí)間。

2016-03-01 11:38:57 1168

1168 。如此一來(lái),Mentor 將會(huì)把 Ixia 的虛擬版本測(cè)試產(chǎn)品系列 IxNetwork? Virtual Edition (VE) 與 Mentor? Veloce? 硬件加速仿真平臺(tái)進(jìn)行集成,以加速復(fù)雜網(wǎng)絡(luò)芯片的驗(yàn)證。

2016-04-13 11:05:07 1299

1299 俄勒岡州威爾遜維爾,2016 年 4 月 20 日 — Mentor Graphics公司(納斯達(dá)克代碼:MENT)今日宣布,Mentor? 硬件加速仿真服務(wù)采用具有專業(yè)服務(wù)和 IP 的 Veloce? 硬件加速仿真平臺(tái) ,借此加速仿真驗(yàn)證并降低與片上系統(tǒng) (SoC) 設(shè)計(jì)相關(guān)的風(fēng)險(xiǎn)。

2016-04-20 11:22:08 2307

2307 “Veloce 硬件加速仿真平臺(tái)可提供我們所需的容量,以此驗(yàn)證我們可編程、特定于網(wǎng)絡(luò)并以互連為主導(dǎo)的設(shè)計(jì),”Barefoot Networks 工程副總裁 Dan Lenoski 說道。“除了利用

2016-07-20 14:25:20 1262

1262 基于硬件加速的實(shí)時(shí)仿真平臺(tái)構(gòu)建技術(shù)_孔璐

2017-01-03 17:41:58 1

1 航電仿真系統(tǒng)集成驗(yàn)證平臺(tái)設(shè)計(jì)方法的研究_周德新

2017-01-18 20:24:57 0

0 UVM已經(jīng)成為了一種高效率的、從模塊級(jí)到系統(tǒng)級(jí)完整驗(yàn)證環(huán)境開發(fā)標(biāo)準(zhǔn),其中一個(gè)關(guān)鍵的原則是UVM可以開發(fā)出可重用的驗(yàn)證組件。獲得重用動(dòng)力的一個(gè)方面表現(xiàn)為標(biāo)準(zhǔn)的仿真器和硬件加速之間的驗(yàn)證組件和環(huán)境的復(fù)用

2017-09-15 17:08:11 14

14 設(shè)計(jì)了一種基于FPGA的驗(yàn)證平臺(tái)及有效的SoC驗(yàn)證方法,介紹了此FPGA驗(yàn)證軟硬件平臺(tái)及軟硬件協(xié)同驗(yàn)證架構(gòu),討論和分析了利用FPGA軟硬件協(xié)同系統(tǒng)驗(yàn)證SoC系統(tǒng)的過程和方法。利用此軟硬件協(xié)同驗(yàn)證

2017-11-17 03:06:01 13138

13138

高性能硬件與智能應(yīng)用程序的結(jié)合使得硬件仿真器更強(qiáng)大,能夠解決復(fù)雜的系統(tǒng)級(jí)設(shè)計(jì)驗(yàn)證難題。 經(jīng)過三十年緩慢但穩(wěn)定的硬件仿真技術(shù)發(fā)展之后,就進(jìn)步加速和預(yù)期的新發(fā)展而言,其前景一片光明。在過去的 30 年中

2017-11-28 11:09:04 0

0 采用System Verilog語(yǔ)言設(shè)計(jì)了一種具有層次化結(jié)構(gòu)的可重用驗(yàn)證平臺(tái),該平臺(tái)能夠產(chǎn)生各種隨機(jī)、定向、錯(cuò)誤測(cè)試向量,并提供功能覆蓋率計(jì)算。將驗(yàn)證平臺(tái)在Synopsys公司的VCS仿真工具上運(yùn)行

2018-01-12 11:28:24 2379

2379

針對(duì)MD5軟件實(shí)現(xiàn)方法存在占用資源大、安全性差等缺點(diǎn),提出了基于NetMagic平臺(tái)的MD5硬件加速模型設(shè)計(jì)方案,并基于ModelSim和NetMagic平臺(tái)對(duì)提出的非流水線與流水線硬件加速模型進(jìn)行

2018-01-12 16:45:07 0

0 Mentor Graphics公司今天宣布,憶芯科技 (Starblaze Technology) 已成功使用 Veloce 硬件加速仿真平臺(tái)進(jìn)行專業(yè)的高速企業(yè)級(jí)固態(tài)硬盤 (SSD) 存儲(chǔ)

2018-07-12 14:43:00 1619

1619 擁有更多軟件、更嚴(yán)格的功耗預(yù)算的更大、更復(fù)雜的設(shè)計(jì),需要采用新的驗(yàn)證解決方案,以應(yīng)對(duì)相關(guān)的技術(shù)挑戰(zhàn)。本文探討了在驗(yàn)證IoT和網(wǎng)絡(luò)設(shè)計(jì)時(shí),傳統(tǒng)數(shù)字軟件仿真和硬件原型不符標(biāo)準(zhǔn)以及使用硬件仿真對(duì)整個(gè)驗(yàn)證

2018-06-05 17:31:00 3197

3197

很多人認(rèn)為硬件加速器無(wú)非是一種速度更快的仿真器而已。毫無(wú)疑問,由于硬件加速器使用物理硬件進(jìn)行仿真,使用硬件加速器驗(yàn)證復(fù)雜的集成電路和大型片上系統(tǒng)(SoC)能比軟件仿真器快若干數(shù)量級(jí)。與仿真用通用計(jì)算機(jī)相比,仿真用單一功能計(jì)算機(jī)能提供更高容量、更高效的系統(tǒng)。

2018-03-28 14:50:00 3160

3160

使用完全脫節(jié)。本白皮書將解釋說明,使用真實(shí)的有效載荷為何對(duì)于準(zhǔn)確估算功耗和執(zhí)行優(yōu)化任務(wù)而言至關(guān)重要。之后,我們將會(huì)展示Veloce~客戶如何使用硬件加速仿真來(lái)實(shí)現(xiàn)可靠性高得多的使用模型,并且利用這一模型,可以更可靠地

2018-03-01 11:42:42 0

0 個(gè)設(shè)計(jì)時(shí)鐘的速度運(yùn)行相關(guān)設(shè)計(jì)。硬件加速器的運(yùn)行速度則是每秒lM左右個(gè)時(shí)鐘,因此可以將原始性能提高1000倍。原始性能相當(dāng)于硬件加速器在無(wú)需等待驗(yàn)證平臺(tái)或外部事件的條件下自由運(yùn)行時(shí)的性能。 驗(yàn)證平臺(tái)對(duì)硬件加速性能影響很大。

2018-03-05 10:13:13 3

3 寒武紀(jì)云端智能芯片產(chǎn)品MLU100中集成了Cadence Memory interface IP和I/O interface IP,并應(yīng)用了Cadence Palladium Z1企業(yè)級(jí)硬件仿真加速平臺(tái)。

2018-05-08 16:53:28 9829

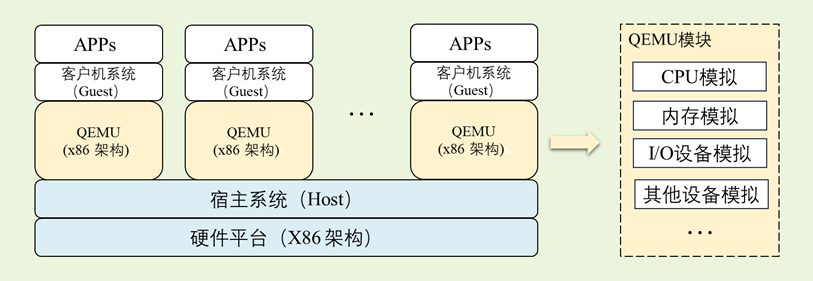

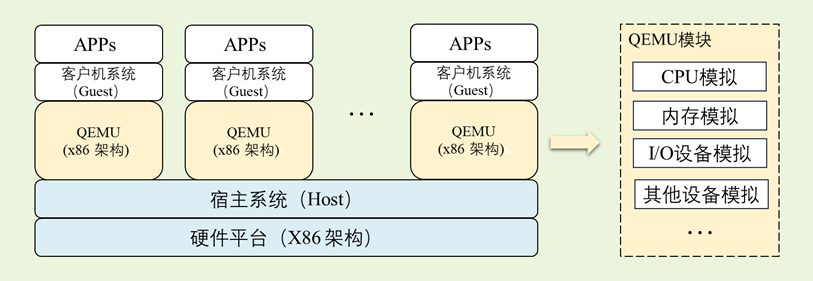

9829 Xilinx針對(duì)Zynq 7000,Zynq Ultrascale + MPSoC和Microblaze的QEMU簡(jiǎn)介。

了解如何使用Xilinx的開源強(qiáng)大仿真平臺(tái)加速您的開發(fā)。

2018-11-21 06:33:00 3325

3325 硬件加速仿真可以實(shí)現(xiàn)寄存器傳輸級(jí)(RTL)和現(xiàn)代SoC設(shè)計(jì)門級(jí)的最佳功耗分析。只有硬件加速仿真才有處理大量邏輯以及產(chǎn)生針對(duì)所有元素的切換活動(dòng)的獨(dú)有能力。

2019-10-11 17:54:29 4550

4550

的3個(gè)主要驗(yàn)證選擇是仿真(emulation)、模擬(simulation)和FPGA原型(prototypes)開發(fā)。隨著FPGA的門數(shù)越來(lái)越高,功能越來(lái)越強(qiáng)大,使其成為了ASIC驗(yàn)證的強(qiáng)有力工具。

2020-10-04 12:48:00 1788

1788

的3個(gè)主要驗(yàn)證選擇是仿真(emulation)、模擬(simulation)和FPGA原型(prototypes)開發(fā)。隨著FPGA的門數(shù)越來(lái)越高,功能越來(lái)越強(qiáng)大,使其成為了ASIC驗(yàn)證的強(qiáng)有力工具。

2020-09-30 17:23:03 879

879

工程師采用了將仿真與仿真相結(jié)合的做法,以改善和加速驗(yàn)證過程。 過去,思科會(huì)為每個(gè)新的IC追求獨(dú)特的驗(yàn)證機(jī)制。為了節(jié)省工作量和時(shí)間,該公司與其工具供應(yīng)商Mentor Graphics合作,對(duì)可應(yīng)用于多種設(shè)計(jì)的方法進(jìn)行了標(biāo)準(zhǔn)化。 思科系統(tǒng)公司

2021-05-02 10:39:00 1199

1199

Cadence Palladium Z1 企業(yè)級(jí)仿真平臺(tái)和 Cadence Protium X1 企業(yè)級(jí)原型驗(yàn)證平臺(tái)來(lái)實(shí)現(xiàn)硬件仿真和原型驗(yàn)證。

2021-03-19 09:37:06 2003

2003 全新Helium Virtual和Hybrid Studio是Cadence驗(yàn)證全流程的組成部分,該流程包括Palladium Z2硬件仿真加速平臺(tái)、Protium X2原型驗(yàn)證平臺(tái)、Xcelium仿真平臺(tái)、JasperGold? 形式化驗(yàn)證平臺(tái)以及vManager? 驗(yàn)證管理平臺(tái)。

2021-09-23 14:30:30 1775

1775 英諾達(dá)EDA硬件驗(yàn)證云服務(wù)平臺(tái)——成都中心被認(rèn)定為『EDA硬件驗(yàn)證服務(wù)公共技術(shù)平臺(tái)』,納入成都市高新區(qū)公共技術(shù)平臺(tái)體系及相關(guān)政策支持范圍。

2021-12-17 13:51:40 1487

1487 歷時(shí)4月,可支持18億門SoC全芯片驗(yàn)證的英諾達(dá)硬件驗(yàn)證云平臺(tái)成都中心一期成功實(shí)現(xiàn)滿載運(yùn)行,圓滿達(dá)成云平臺(tái)一期運(yùn)營(yíng)所有目標(biāo)!英諾達(dá)的云平臺(tái),不同于傳統(tǒng)的IDC機(jī)房,機(jī)器要求高、運(yùn)營(yíng)復(fù)雜、專業(yè)要求極高

2021-12-17 13:54:49 1771

1771 Cadendce 誠(chéng)邀您報(bào)名即將線上舉行的CadenceTECHTALK:使用 Protium X2 加速復(fù)雜 SoC 芯片原型驗(yàn)證。

2022-03-20 15:20:23 1922

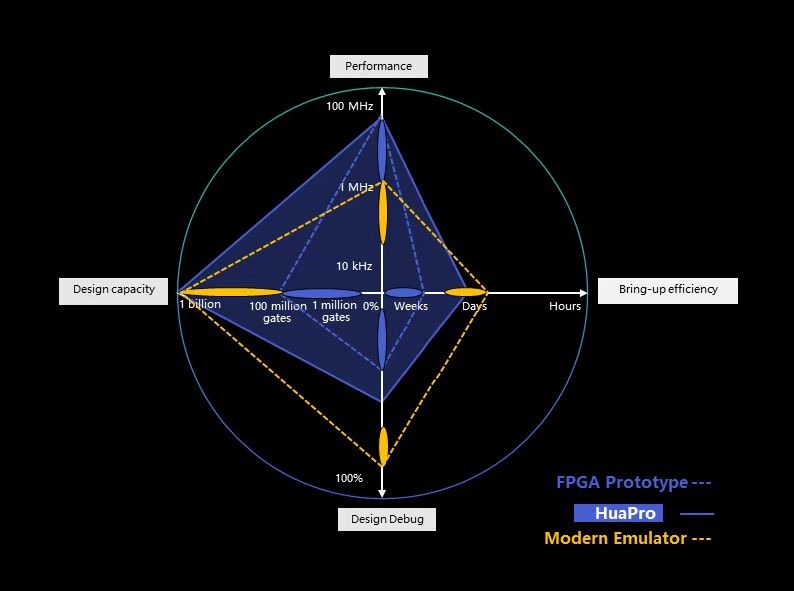

1922 從系統(tǒng)的特性上看,F(xiàn)PGA 原型系統(tǒng)支持多FPGA、自動(dòng)分割;性能較高的情況下運(yùn)行系統(tǒng)軟件;仿真加速器的超大容量可以放全芯片的設(shè)計(jì),進(jìn)行全芯片的系統(tǒng)功能/性能/功耗驗(yàn)證。

2022-05-25 09:35:13 7629

7629 然而,值得注意的是,在某些應(yīng)用程序中仍然需要擁有硬件接口的 ICE 環(huán)境。因此,有多種仿真工具,例如 Mentor 的 Veloce 仿真平臺(tái),它提供了 ICE 和協(xié)同仿真方法的組合。

2022-06-13 10:18:36 910

910

硬件仿真以前僅限于驗(yàn)證超大型設(shè)計(jì),如今已成為所有設(shè)計(jì)驗(yàn)證和確認(rèn)流程的基礎(chǔ)。這種新發(fā)現(xiàn)的流行是日益增長(zhǎng)的硅復(fù)雜性和嵌入式軟件的廣泛使用的結(jié)果。

2022-06-19 16:22:51 1824

1824

Veloce 仿真平臺(tái)使用虛擬原型設(shè)計(jì)和類似虛擬實(shí)驗(yàn)室的環(huán)境,允許 SoC 設(shè)計(jì)人員通過 Codelink 和 WarpCore 等工具執(zhí)行軟件調(diào)試。以 WarpCore 為例,它結(jié)合了虛擬機(jī)和 RTL 執(zhí)行環(huán)境,只有在不涉及太多硬件的情況下才會(huì)發(fā)揮作用。

2022-07-05 09:19:59 626

626 硬件仿真以前僅限于驗(yàn)證超大型設(shè)計(jì),如今已成為所有設(shè)計(jì)驗(yàn)證和確認(rèn)流程的基礎(chǔ)。這種新發(fā)現(xiàn)的流行是日益增長(zhǎng)的硅復(fù)雜性和嵌入式軟件的廣泛使用的結(jié)果。

2022-07-05 09:57:49 1687

1687

ASIC設(shè)計(jì)服務(wù)暨IP研發(fā)銷售廠商智原科技(Faraday Technology Corporation,TWSE:3035)今日發(fā)布FPGA-Go-ASIC驗(yàn)證平臺(tái)。

2022-07-29 10:08:16 784

784 與傳統(tǒng)的云服務(wù)廠商不同,EDA仿真驗(yàn)證的云供應(yīng)商不是簡(jiǎn)單地購(gòu)置通用服務(wù)器后,在上面安裝EDA軟件即可,而是需要基于專用EDA硬件加速器構(gòu)造數(shù)據(jù)中心,比如Cadence的Palladium、Mentor的Veloce或是新思的Zebu等等。

2022-08-05 10:32:11 1182

1182 虛擬數(shù)字機(jī)器人仿真測(cè)試驗(yàn)證平臺(tái),真正提供機(jī)器人控制器檢測(cè)、驗(yàn)證平臺(tái),可檢測(cè)各類工業(yè)機(jī)器人控制器的功能、性能指標(biāo),允許基于EtherCAT總線的機(jī)器人控制器連接,仿真硬件可實(shí)時(shí)吞吐仿真數(shù)據(jù),實(shí)現(xiàn)ms級(jí)的檢測(cè)、驗(yàn)證。

2022-08-31 20:39:09 945

945

軟件仿真(Simulation),F(xiàn)PGA原型驗(yàn)證(FPGA Based Prototyping)和硬件仿真加速(Emulation)這三種有效的功能驗(yàn)證的方法,在驗(yàn)證流程中發(fā)揮著非常重要的作用。

2022-10-10 16:06:53 1189

1189 百度百科對(duì)UVM的釋義如下:通用驗(yàn)證方法學(xué)(Universal Verification Methodology, UVM)是一個(gè)以SystemVerilog類庫(kù)為主體的驗(yàn)證平臺(tái)開發(fā)框架,驗(yàn)證工程師可以利用其可重用組件構(gòu)建具有標(biāo)準(zhǔn)化層次結(jié)構(gòu)和接口的功能驗(yàn)證環(huán)境。

2022-11-30 12:47:00 1060

1060 所以通過專門的設(shè)備在硬件上調(diào)試芯片設(shè)計(jì), 如硬件仿真和原型驗(yàn)證,是其重要的解決方案之一。硬件仿真和原型驗(yàn)證的效率和速度比軟件仿真可要高很多,尤其是硬件仿真,它可以對(duì)完整的芯片設(shè)計(jì)進(jìn)行自動(dòng)化的加速仿真并調(diào)試,多應(yīng)用于芯片設(shè)計(jì)前期的RTL功能驗(yàn)證。

2023-04-21 14:42:08 353

353 手段有三個(gè)——邏輯仿真(Simulation)、硬件加速仿真(Emulation)驗(yàn)證和原型驗(yàn)證(Prototyping)。 邏輯仿真 是傳統(tǒng)驗(yàn)證手段,通過對(duì)模塊級(jí)邏輯的行為進(jìn)行建模,芯片設(shè)計(jì)團(tuán)隊(duì)可以利用仿真軟件分區(qū)塊對(duì)SoC進(jìn)行驗(yàn)證,以此確認(rèn)芯片功能是否符合確定

2023-06-02 15:18:56 1154

1154

面對(duì)復(fù)雜的設(shè)計(jì)代碼,我們?nèi)绾未_保其準(zhǔn)確性?功能驗(yàn)證就是這場(chǎng)戰(zhàn)斗的關(guān)鍵過程。工程師們通常使用的驗(yàn)證方法包括軟件仿真、硬件仿真和原型驗(yàn)證等。這些不同的驗(yàn)證方法都有各自的優(yōu)點(diǎn),也有各自的不足。

2023-06-11 14:24:53 490

490

隨著SOC/ASIC設(shè)計(jì)規(guī)模不斷增大,且結(jié)構(gòu)愈加復(fù)雜,導(dǎo)致驗(yàn)證的復(fù)雜度呈指數(shù)級(jí)增長(zhǎng)。為了縮短芯片的上市周期,在不同設(shè)計(jì)階段工程師們往往選擇不同的仿真驗(yàn)證工具,提高整個(gè)芯片開發(fā)效率。在一個(gè)芯片

2023-01-12 17:11:15 492

492

軟件仿真(Simulation),原型驗(yàn)證(Prototyping),以及硬件仿真 (Emulation),是當(dāng)前主要的三種有效的驗(yàn)證方法,在芯片前端設(shè)計(jì)的功能性驗(yàn)證階段起到了關(guān)鍵的作用。

2023-07-27 09:57:57 349

349

近日,亞科鴻禹新一代硬件仿真加速器HyperSemu成功在北京某領(lǐng)先無(wú)線數(shù)字通信芯片開發(fā)企業(yè)的下一代“Wi-Fi6+藍(lán)牙雙模IoT芯片”項(xiàng)目中完成部署,實(shí)現(xiàn)了對(duì)原有仿真方法200倍的加速,達(dá)到業(yè)內(nèi)

2023-09-13 09:49:29 272

272 面對(duì)復(fù)雜的設(shè)計(jì)代碼,確保其準(zhǔn)確性至關(guān)重要,功能驗(yàn)證就是非常重要的一環(huán)。通常使用的驗(yàn)證方法包括軟件仿真、硬件仿真和原型驗(yàn)證等。雖然軟件仿真易于使用,但一旦碰到大規(guī)模數(shù)字電路設(shè)計(jì),仿真所需要的時(shí)間就越

2023-09-13 08:28:02 393

393

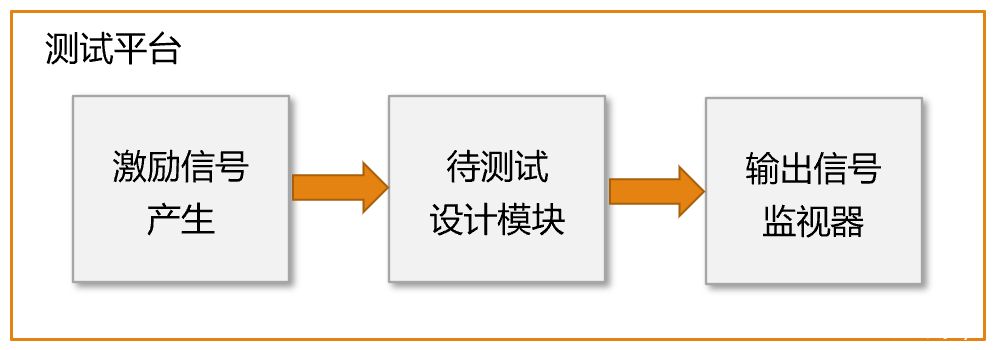

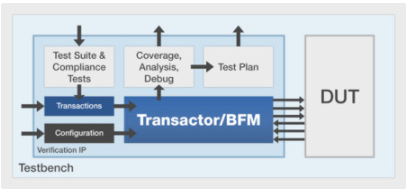

仿真驗(yàn)證主要作用是搭建一個(gè)測(cè)試平臺(tái),測(cè)試和驗(yàn)證程序設(shè)計(jì)的正確性,驗(yàn)證設(shè)計(jì)是否實(shí)現(xiàn)了我們所預(yù)期的功能。其結(jié)構(gòu)如下圖所示。

2023-10-02 16:29:00 660

660

當(dāng)設(shè)計(jì)的規(guī)模動(dòng)輒幾十億門,系統(tǒng)驗(yàn)證時(shí)間不斷的增加,硬件驗(yàn)證系統(tǒng)幾乎是驗(yàn)證工程師不可或缺的利器,因此對(duì)高性能硬件驗(yàn)證系統(tǒng)提出了更多的需求。

2024-01-05 10:06:47 254

254 面向高性能計(jì)算、IoT、無(wú)線接入、音頻、多媒體、消費(fèi)類電子、邊緣計(jì)算等迅速擴(kuò)展的RISC-V使用場(chǎng)景,湯谷智能發(fā)布了基于自研Logic Giant原型驗(yàn)證硬件平臺(tái)的全棧RISC-V硬件仿真加速系統(tǒng)方案。

2024-01-25 10:29:28 283

283

FPGA原型驗(yàn)證平臺(tái)與硬件仿真器在芯片設(shè)計(jì)和驗(yàn)證過程中各自發(fā)揮著獨(dú)特的作用,它們之間存在明顯的區(qū)別。

2024-03-15 15:07:03 131

131

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論