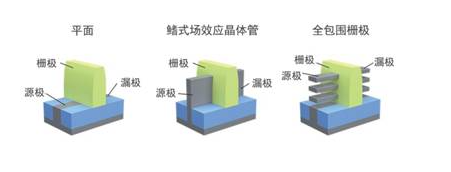

FinFET立體晶體管技術是Intel 22nm率先引用的,這些年一直是半導體制造工藝的根基,接下來在Intel 20A、臺積電2nm、三星3nm上,都將轉(zhuǎn)向全環(huán)繞立體柵極晶體管。

2023-10-23 11:15:08 59

59

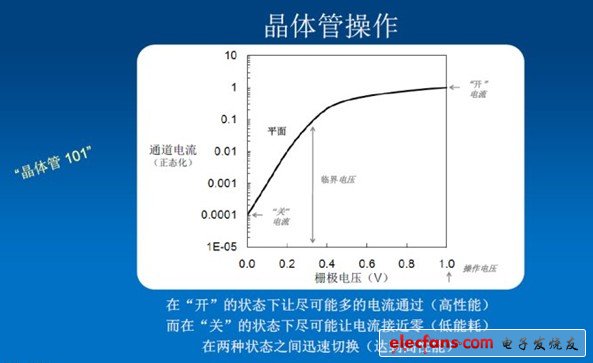

; 晶體管,本名是半導體三極管,是內(nèi)部含有兩個PN結,外部通常為三個引出電極的半導體器件。它對電信號有放大和開關等作用,應用十分廣泛。輸入級和輸出

2010-08-12 13:57:39

最近有許多正在全球范圍內(nèi)研究和開發(fā)的技術,例如晶體管GAA(Gate All around)、背面供電以及3D IC。

2023-07-26 18:21:58 998

998

在半導體行業(yè)的最初幾十年里,新的工藝節(jié)點只需縮小晶體管的物理尺寸并將更多晶體管塞到芯片上即可實現(xiàn)性能、功耗和面積增益,這稱為經(jīng)典縮放。集成電路工作得更好,因為電信號在每個晶體管之間傳播的距離更短。

2023-07-16 15:47:43 253

253 然而,前不久麻省理工學院(MIT)華裔研究生朱家迪突破了常溫條件下由二維(2D)材料制造成功的原子晶體管,每個晶體管只有 3 個原子的厚度,堆疊起來制成的芯片工藝將輕松突破 1nm。

2023-05-31 15:45:29 975

975

然而,前不久麻省理工學院(MIT)華裔研究生朱家迪突破了常溫條件下由二維(2D)材料制造成功的原子晶體管,每個晶體管只有 3 個原子的厚度,堆疊起來制成的芯片工藝將輕松突破 1nm。

2023-05-30 14:24:48 1116

1116

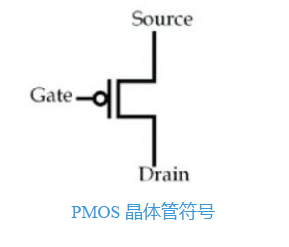

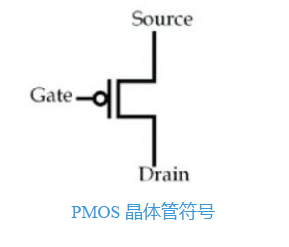

PMOS晶體管,也稱為P溝道金屬氧化物半導體,是一種晶體管形式,其中溝道或柵極區(qū)域使用p型摻雜劑。這個晶體管與NMOS晶體管完全相反。這些晶體管包含三個主要端子:源極、柵極和漏極。晶體管的源極端子由

2023-02-11 16:48:03 8728

8728

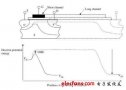

場效應晶體管的源極、漏極和柵極分別相當于晶體管的發(fā)射極、集電極和基極。對應于晶體管放大電路,場效應晶體管放大電路也有三種組態(tài):共源極放大電路、共漏極放大電路和共柵極放大電路,其特點分別和晶體管放大電路中的共射極、共集電極、共基極放大電路類似。

2022-11-30 09:30:00 1635

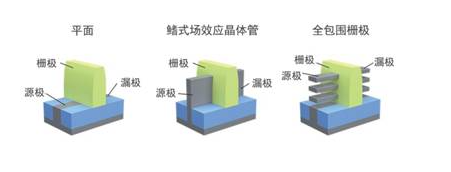

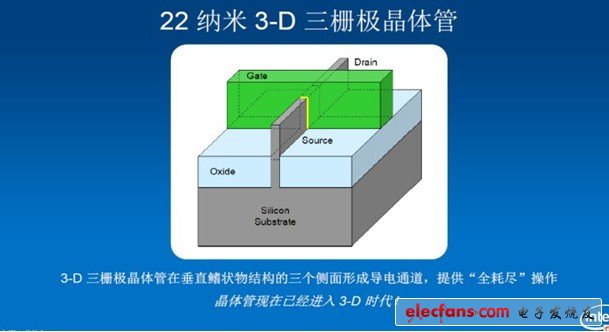

1635 BSPDN可以理解為Chiplet技術的演變(圖自:IMEC) 目前主流的 FinFET(過去被稱為 3D 晶體管)是 10nm 工藝發(fā)展過程中的關鍵芯片設計技術,采用三面包覆式的柵極設計,可以在三個側面圍起電流通道,以此減少漏電流(電子泄露)。

2022-11-11 14:42:53 570

570 在了解mos管柵極電阻的作用之前,我們先了解一下mos管柵極及其他2個極的基礎知識。場效應管根據(jù)三極管的原理開發(fā)出的新一代放大元件,有3個極性,柵極,漏極,源極,它的特點是柵極的內(nèi)阻極高,采用

2022-09-27 15:29:50 5811

5811 FinFET在22nm節(jié)點的首次商業(yè)化為晶體管——芯片“大腦”內(nèi)的微型開關——制造帶來了顛覆性變革。與此前的平面晶體管相比,與柵極三面接觸的“鰭”所形成的通道更容易控制。但是,隨著3nm和5nm技術節(jié)點面臨的難題不斷累積,F(xiàn)inFET的效用已經(jīng)趨于極限。

2022-08-01 15:33:11 799

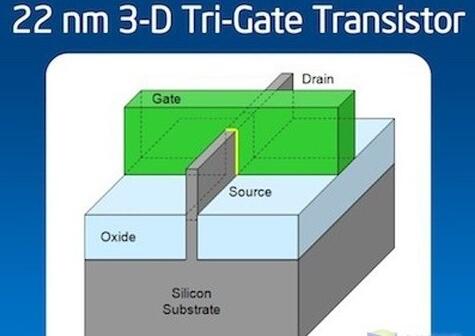

799 FinFET確切的說,是一個技術的代稱。世界上第一個3D三維晶體管是由英特爾在2011年5月宣布研制成功,當時英特爾稱其為 “Tri-Gate”(三柵極晶體管)。

2022-07-08 15:04:26 1549

1549 北斗星通的22nm工藝的全系統(tǒng)全頻厘米級高精度GNSS芯片,在單顆芯片上實現(xiàn)了基帶+射頻+高精度算法一體化。

2022-07-04 15:53:48 1290

1290 現(xiàn)在的芯片技術越來越先進,人們常常能夠聽到某某公司又研發(fā)出5nm、4nm芯片的消息,而目前全球所研發(fā)出的最先進的芯片是IBM公司的2nm芯片,我們都知道芯片內(nèi)部有很多晶體管,那么2nm芯片的晶體管

2022-07-04 09:15:36 3450

3450 日前,三星放出了將在6月30日正式量產(chǎn)3nm芯片的消息,今天上午,三星官方宣布已經(jīng)開始了3nm工藝芯片的量產(chǎn)。 三星官方稱,其采用了GAA晶體管的3nm工藝芯片已經(jīng)在韓國華城工廠開始量產(chǎn)。 現(xiàn)在全球

2022-06-30 16:36:27 1768

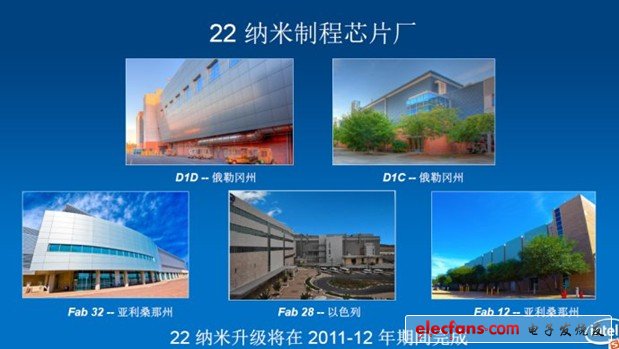

1768 的技術呢? 據(jù)了解,全球芯片巨頭Intel在2011年發(fā)布了22nm工藝,而在2012年第三季度,臺積電也開始了22nmHP制程的芯片研發(fā)工作,因此可得出22nm芯片最早在2011年被發(fā)布出來,是2011年的技術。 不過這并不代表著我國這些22nm芯片就很落后,相反,在導航定位領

2022-06-29 11:06:17 4290

4290 我國在半導體行業(yè)一直都處于落后狀態(tài),不過近幾年已經(jīng)慢慢地開始追趕上來了,在半導體設備這方面,我國的上海微電子已經(jīng)成功研發(fā)出了深紫外光光刻機,這種光刻機能夠進行22nm制程工藝的加工,也就是說在

2022-06-29 10:37:36 1595

1595 之前北斗星通所宣布的22nm定位芯片在業(yè)界引起了巨大的轟動,北斗星通的創(chuàng)始人周儒欣表示:這顆芯片應該是全球衛(wèi)星導航領域最先進的一顆芯片了。 有人就對這句話感到懷疑了,北斗星通22nm芯片先進嗎?臺積

2022-06-29 10:11:40 2297

2297 據(jù)芯片行業(yè)來看,目前22nm和28nm的芯片工藝技術已經(jīng)相當成熟了,很多廠商也使用22nm、28nm的芯片居多,主要原因就是價格便宜,那么這兩個芯片之間有什么性能差異呢?

2022-06-29 09:47:46 7231

7231 在全球范圍內(nèi),目前共有美國、俄羅斯、中國三個國家擁有完整的衛(wèi)星導航系統(tǒng),我們中國的衛(wèi)星導航系統(tǒng)就是大名鼎鼎的北斗導航系統(tǒng),這款導航系統(tǒng)采用了一款北斗22nm芯片,那么這款北斗22nm芯片用途是什么呢

2022-06-27 11:56:36 2559

2559 目前從全球范圍來說,也就只有臺積電和三星這兩家能做到5納米工藝以下了。6月29日晚間,據(jù)外媒報道,三星宣布其基于柵極環(huán)繞型 (Gate-all-around,GAA) 晶體管架構的3nm工藝技術已經(jīng)

2021-07-02 11:21:54 2136

2136 晶體管是器件中提供開關功能的關鍵組件。幾十年來,基于平面晶體管的芯片一直暢銷不衰。走到20nm時,平面晶體管開始出現(xiàn)疲態(tài)。為此,英特爾在2011年推出了22nm的FinFET,之后晶圓廠在16nm/14nm予以跟進。

2021-03-22 11:35:24 1945

1945 作者:泛林Nerissa Draeger博士 FinFET在22nm節(jié)點的首次商業(yè)化為晶體管——芯片“大腦”內(nèi)的微型開關——制造帶來了顛覆性變革。與此前的平面晶體管相比,與柵極三面接觸的“鰭”所形成

2021-01-25 15:25:40 2669

2669

領先的移動和汽車SoC半導體IP提供商Arasan Chip Systems今天宣布,用于臺積公司22nm工藝技術的eMMC PHY IP立即可用 加利福尼亞州圣何塞2021年1月21日 /美通社

2021-01-21 10:18:23 2193

2193 ? ? FinFET晶體管架構是當今半導體行業(yè)的主力軍。但是,隨著器件的持續(xù)微縮,短溝道效應迫使業(yè)界引入新的晶體管架構。在本文中,IMEC的3D混合微縮項目總監(jiān)Julien Ryckaert勾勒出了

2020-12-30 17:45:16 2468

2468 互補場效應晶體管(hCFET)。 由于微加工技術的進步,電場效應晶體管(FET)已實現(xiàn)了高性能和低功耗。 在22nm世代中,它推進到被稱為“ FinFET”的三維柵極結構的FET。此外,GAA(全方位門)結構已作為替代版本出現(xiàn)。 除此之外,還有一種稱為CFET結構的技術,該結構是將

2020-12-21 10:36:58 2844

2844 全環(huán)繞柵極晶體管的出現(xiàn)滿足了以上所有需求,從而允許摩爾定律在5納米之后進一步前進。首先其生產(chǎn)工藝與鰭式晶體管相似,關鍵工藝步驟幾乎一樣(這點我們會在之后的文章中進一步講解)。其次,全環(huán)繞柵極晶體管

2020-09-29 13:54:39 3601

3601 圖片來源:聯(lián)電 12月2日,中國臺灣半導體代工廠聯(lián)電(UMC)宣布,在首次成功使用硅技術之后,其22nm制程技術已準備就緒。 該公司稱,全球面積最小、使用22nm制程技術的USB 2.0通過硅驗證

2019-12-03 09:59:41 4346

4346 在9月的臺灣SEMICON國際半導體展上,臺積電(TSMC)首席執(zhí)行官Mark Lui認為摩爾定律仍然有效。他表示,由于先進工藝技術(如納米片)或3D FinFETS中的全柵晶體管技術的發(fā)展

2019-10-15 15:11:02 5321

5321 今天有多家媒體報道了中國科研人員實現(xiàn)了3nm半導體工藝的突破性進展,香港《南華早報》稱中科院微電子所團隊的殷華湘等人研究出了3nm晶體管,相當于人類DNA鏈條寬度,這種晶體管解決了玻爾茲曼熱力學的限制。

2019-05-29 16:48:09 4236

4236 XX nm制造工藝是什么概念?芯片的制造工藝常常用90nm、65nm、40nm、28nm、22nm、14nm來表示。現(xiàn)在的CPU內(nèi)集成了以億為單位的晶體管,這種晶體管由源極、漏極和位于他們之間的柵極所組成,電流從源極流入漏極,柵極則起到控制電流通斷的作用。

2019-02-20 11:08:02 31585

31585 新的微加工技術可用于生產(chǎn)有史以來最小的3D晶體管,尺寸是目前主流商用產(chǎn)品的三分之一。

2018-12-12 09:40:48 2861

2861 半導體行業(yè)觀察:目前,制造先進芯片離不開晶體管,其核心在于垂直型柵極硅,原理是當設備開關開啟時,電流就會通過該部位,然后讓晶體管運轉(zhuǎn)起來。

2017-12-26 11:50:54 4280

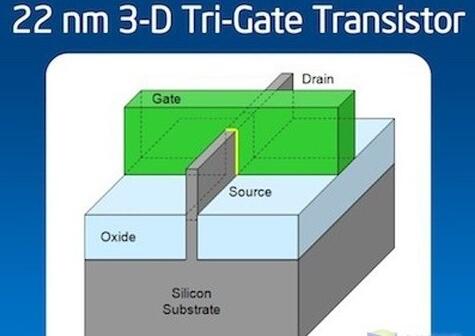

4280 intel的22nm 3D工藝牛,到底牛到什么程度,到底對業(yè)界有神馬影響,俺也搞不太清楚。這不,一封email全搞定了。

2017-02-11 10:47:11 1166

1166 為什么說7nm是物理極限?縮短晶體管柵極的長度可以使CPU集成更多的晶體管或者有效減少晶體管的面積和功耗,并削減CPU的硅片成本。不過這種做法也會使電子移動的距離縮短,容易導致晶體管內(nèi)部電子自發(fā)通過

2016-10-10 16:49:39 5765

5765 目前3D晶體管成為代工產(chǎn)業(yè)重點關注的技術,但很多人關于這個技術的細節(jié)不是很了解,我們在這里介紹一下。

2015-12-28 14:34:12 11367

11367

對于英特爾來說,要想在移動芯片市場多分得一杯羹,就需要借助其更加先進的制造能力的優(yōu)勢。而今日宣布的新款Atom SoCs——舉例來說——即基于22nm的3D或“三柵極晶體管”工藝。與傳統(tǒng)

2014-02-25 09:08:51 930

930 i HD1000是Speedster22i FPGA產(chǎn)品家族的首個成員。該器件采用英特爾領先的22nm 3D Tri-Gate晶體管技術,其功耗是競爭對手同類器件的一半。

2013-03-04 13:47:58 1477

1477 IBM在Common Platform技術論壇上展示了藍色巨人對未來晶圓的發(fā)展預測,Common Platform是IBM、Globalfoundries和Samsung的聯(lián)盟,旨在研究3D晶體管

2013-02-20 23:04:30 7669

7669 英特爾在4月23日正式發(fā)布Ivy Bridge處理器。Ivy Bridge是英特爾首款22nm工藝處理器,采用革命性的三柵極3D晶體管工藝制造。緊隨其后,美國FPGA廠商Achronix在次日便宣布發(fā)布全球首款22nm工藝

2013-01-16 16:55:13 1363

1363 近日消息,英特爾計劃將“3D晶體管”工藝應用到SoC移動芯片上,以獲得產(chǎn)品性能飛躍性提升,但對于“3D晶體管”技術是否適用于SoC芯片的制造,參與舊金山國際電子產(chǎn)品大會的專家們

2012-12-11 09:05:45 1014

1014 裸眼3D顯示技術詳解介紹了3D顯示原理、3D顯示分類、柱狀透鏡技術、視差屏障技術、指向光源技術以及3D顯示技術發(fā)展趨勢。

2012-08-17 13:39:55 143

143 英特爾已經(jīng)準備把第一個3D晶體管結構導入大量生產(chǎn),它將是首款使用3-D Tri-Gate晶體管的量產(chǎn)芯片。22納米處理器,代號為Ivy Bridge。3-D晶體管和2-D平面晶體管有本質(zhì)性的區(qū)別,它不只可

2012-08-15 11:23:24 921

921

英特爾已經(jīng)準備把第一個3D晶體管結構導入大量生產(chǎn),它將是首款使用3-D Tri-Gate晶體管的量產(chǎn)芯片。22納米處理器,代號為Ivy Bridge。3-D晶體管和2-D平面晶體管有本質(zhì)性的區(qū)別,它不只可

2012-08-15 11:23:24 1179

1179 英特爾已經(jīng)準備把第一個3D晶體管結構導入大量生產(chǎn),它將是首款使用3-D Tri-Gate晶體管的量產(chǎn)芯片。22納米處理器,代號為Ivy Bridge。3-D晶體管和2-D平面晶體管有本質(zhì)性的區(qū)別,它不只可

2012-08-15 11:23:24 4748

4748 本文核心議題: 本文是對Intel 22nm三柵技術的后續(xù)追蹤報道,為此,這里搜集了多位業(yè)界觀察家、分析家對此的理解和意見,以便大家I更深入的了解ntel 22nm三柵技術。 鰭數(shù)可按需要進行

2012-08-15 09:46:03 1199

1199

Intel2011年5月6日研制成功的世界上第一個3D晶體管“Tri-Gate”現(xiàn)在已經(jīng)逐步進入大家的視線了,本文將介紹3D晶體管的一些優(yōu)點。

2012-08-08 11:49:46 1736

1736 什么是3D晶體管?3D晶體管,從技術上講,應該是三個門晶體管。傳統(tǒng)的二維門由較薄的三維硅鰭(fin)所取代,硅鰭由硅基垂直伸出。

2012-08-08 11:12:01 2992

2992 本文通過高清圖詳解Intel最新22nm 3D 晶體管 。業(yè)界一直傳說3D三柵級晶體管技術將會用于下下代14nm的半導體制造,沒想到英特爾竟提前將之用于22nm工藝,并且于上周四向全世界表示將在

2012-08-03 17:09:18 70

70 2012年4月23日,英特爾宣布采用3D三柵極晶體管設計,最小線寬為22納米的Ivy Bridge微處理器量產(chǎn)成功,并于4月29日開始全球銷售。

2012-05-13 09:35:43 4558

4558 Achronix 半導體公司今日宣布了其 Speedster22i HD和HP產(chǎn)品系列的細節(jié),它們是將采用英特爾22nm 3D晶體管技術工藝制造的首批現(xiàn)場可編程門陣列(FPGA)產(chǎn)品。Speedster22i FPGA產(chǎn)品是業(yè)內(nèi)唯一

2012-04-25 09:12:05 1138

1138 Intel Ivy Bridge處理器只是一次制程升級,對CPU性能來說沒什么特別的,但是就制造工藝而言,Ivy Bridge不啻于一場革命,因為它不僅是首款22nm工藝產(chǎn)品,更重要的是Intel將從22nm工藝節(jié)點開

2012-04-18 14:02:29 890

890

在22nm,或許是16nm節(jié)點,我們將需要全新的晶體管。而在這其中,爭論的焦點在于究竟該采用哪一種技術。這場比賽將關乎到晶體管的重新定義。在22/20nm邏輯制程的開發(fā)中,業(yè)界都爭先

2012-03-25 10:52:16 1363

1363

在22nm,或許是16nm節(jié)點,我們將需要全新的晶體管。而在這其中,爭論的焦點在于究竟該采用哪一種技術。這場比賽將關乎到晶體管的重新定義。在22/20nm邏輯制程的開發(fā)中,業(yè)界都爭先

2012-03-06 10:08:16 1756

1756 可編程邏輯廠商Tabula 2月21日確認,英特爾將使用最新技術3-D三柵極晶體管技術為其代工22-nm3PLD產(chǎn)品。

2012-02-21 15:07:15 875

875

晶體管是現(xiàn)代電子學的基石,而Intel 此舉堪稱晶體管歷史上最偉大的里程碑式發(fā)明,甚至可以說是重新發(fā)明了晶體管。半個多世紀以來,晶體管一直都在使用2-D 平面結構,現(xiàn)在終于邁入

2012-01-18 15:28:52 146

146 Intel在微處理器晶體管設計上取得重大突破,沿用50多年的傳統(tǒng)硅晶體管將實現(xiàn)3D架構,一款名為Tri-Gate的晶體管技術得到實現(xiàn)。 3D Tri-Gate晶體管使用了一個微薄的三維硅鰭片取代了傳統(tǒng)

2011-10-25 09:35:40 1274

1274 近日公布2011年“科技創(chuàng)新獎”,英特爾的3-D三柵極晶體管設計獲得半導體類別創(chuàng)新大獎。英特爾的3-D三柵極晶體管結構代表著從2-D平面晶體管結構的根本性轉(zhuǎn)變

2011-10-23 01:01:04 867

867 在本周于舊金山召開的英特爾開發(fā)者大會(IDF)中,英特爾將再揭示其采用三柵極(tri-gate)3D晶體管技術的22nm元件細節(jié),并進一步說明超輕薄筆電(Ultrabook)的超薄、超低功耗設計概念。

2011-09-16 09:23:43 811

811 22nm以后的晶體管技術領域,靠現(xiàn)行Bulk MOSFET的微細化會越來越困難的,為此,人們關注的是平面型FD-SOI(完全空乏型SOI)元件與基于立體通道的FinFET。由于這些技術都不需要向通

2010-06-23 08:01:42 496

496 臺積電又跳過22nm工藝 改而直上20nm

為了在競爭激烈的半導體代工行業(yè)中提供最先進的制造技術,臺積電已經(jīng)決定跳過22nm工藝的研

2010-04-15 09:52:16 816

816 Intel 22nm光刻工藝背后的故事

去年九月底的舊金山秋季IDF 2009論壇上,Intel第一次向世人展示了22nm工藝晶圓,并宣布將在2011年下半年發(fā)布相關產(chǎn)品。

2010-03-24 08:52:58 1019

1019 什么是絕緣柵極雙極性晶體管

絕緣柵雙極晶體管(IGBT)本質(zhì)上是一個場效應晶體管,只是在漏極和漏區(qū)之間多了一個P型層.根據(jù)國際電工委員會IEC/TC(CO)1

2010-03-05 15:49:22 3985

3985 臺積電計劃于2012年Q3開始試產(chǎn)22nm HP制程芯片

據(jù)臺積電公司負責開發(fā)的高級副總裁蔣尚義透露,他們計劃于2012年第三季度開始試產(chǎn)22nm HP(高性能)制程的芯片產(chǎn)品,并

2010-02-26 12:07:17 783

783

電子發(fā)燒友App

電子發(fā)燒友App

評論