MotorControl Workbench 5.4.4生成代碼只支持增量編碼器和霍爾編碼器。怎么改絕對值編碼器

?分別需要改哪幾個函數?請問一下,大家有沒有這方面的例子?

2024-03-14 06:21:52

RK3568驅動指南|驅動基礎進階篇-進階8 內核運行ko文件總結

2024-01-31 14:58:59 180

180

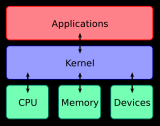

我們常說,看一個系統是不是自研,就看它的內核,常見的內核分為:宏內核和微內核,當然還有兩者結合體,他們到底有什么區別? 白話宏內核和微內核 有一天,你結婚了,你和你的愛人住一套房子,你的父母和你愛人

2024-01-30 16:43:10 145

145

電子發燒友網站提供《使用P4和Vivado工具簡化數據包處理設計.pdf》資料免費下載

2024-01-26 17:49:11 0

0 Linux內核主要由以下幾個部分組成: 進程管理:Linux內核負責管理和調度系統中的進程。它通過進程調度算法來決定哪個進程在什么時間運行以及如何分配系統資源。 內存管理:Linux內核負責管理系統

2024-01-22 14:34:43 636

636 前面我們已經介紹了內核注意到信號的到來,調用相關函數更新進程描述符以便進程接收處理信號。但是,如果目標進程此時沒有運行,內核則推遲傳遞信號。現在,我們看看內核如何處理進程掛起的信號。

2024-01-17 09:51:05 391

391

在Vivado中禁止自動生成BUFG(Buffered Clock Gate)可以通過以下步驟實現。 首先,讓我們簡要了解一下什么是BUFG。BUFG是一個時鐘緩沖器,用于緩沖輸入時鐘信號,使其更穩

2024-01-05 14:31:06 454

454 有些時候在寫完代碼之后呢,Vivado時序報紅,Timing一欄有很多時序問題。

2024-01-05 10:18:36 291

291 Vivado在前一段時間更新了2023.2版本,經過一段時間的使用這個版本還是很絲滑的,用起來挺舒服。

2024-01-02 09:39:41 828

828

vivado出現安裝問題剛開始還以為是安裝路徑包含中文空格了,重裝的注意了一下,發現還是這個問題。。。。后來又一頓操作猛如虎,終于發現了問題。出這個問題的原因是vivado壓縮包解壓的路徑包含中文了把解壓文件放到不含中文的地方,再重新安裝,安裝路徑也不能含中文。然后。。。。。然后就安裝完成了

2023-12-22 10:56:33 0

0 vivado軟件的安裝教程以及license

2023-12-21 19:50:00

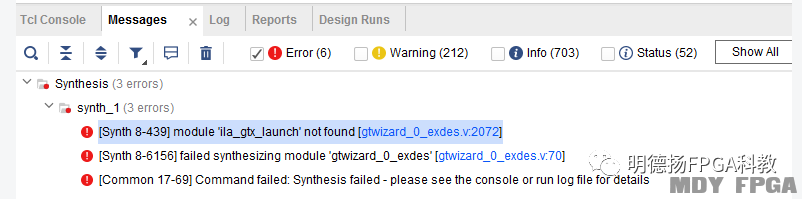

【關鍵問題!!!!重要!!!】VIVADO會在MESSAGE窗口出提示很多錯誤和警告信息!

2023-12-15 10:11:22 666

666

文章是基于Vivado的 2017.1的版本,其他版本都大同小異。 首先在Vivado界面的右側選擇IP Catalog 選項。

2023-12-05 15:05:02 317

317 近幾天調試開發板,主芯片是XC7A100T,用Vivado給開發板下載bit文件,正常工作。

2023-12-04 09:54:28 339

339 請問ADSP21489可運行幾個2000階的FIR濾波器?

2023-11-29 07:01:28

在使用JTAG仿真器在vivado環境下抓信號時,報如下錯誤:

2023-11-14 10:37:20 1052

1052 補丁和不斷完善代碼,BPF程序變成了一個更通用的執行引擎,可以完成多種任務。簡單來說,BPF提供了一種在各種內核時間和應用程序事件發生時運行一小段程序的機制。其允許內核在系統和應用程序事件發生時運行一小段程序,這樣就將內核變得完全可編程,允許用戶定制和控制他們的

2023-11-10 10:34:39 410

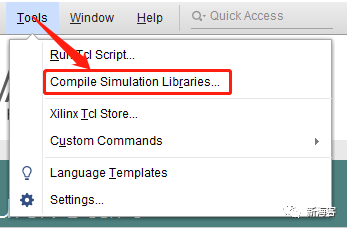

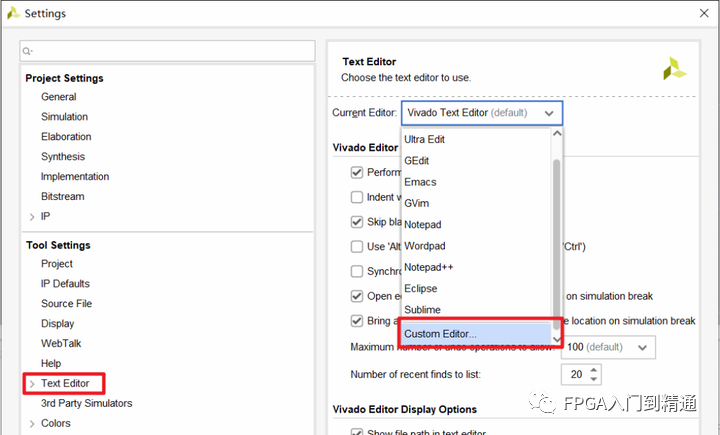

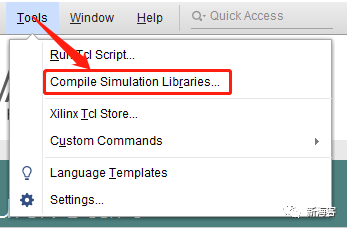

410 Vivado自帶的仿真工具在一些基本功能的仿真測試時是可以滿足的,但如果你的工程較為龐大,那么自帶的仿真工具將有些勉強,除了在數據輸出方面的卡頓,在仿真速度上也可能無法接受,這里可以借助第三方仿真工具進行工程仿真測試,Vivado2018各版本支持的仿真工具見下。

2023-11-08 14:47:30 512

512

stm32f103mini板子芯片改mm32f103不運行是什么原因,是不是硬件還要修改

2023-11-02 07:40:57

《Vivado Design Suite 用戶指南:編程和調試》 文檔涵蓋了以下設計進程: 硬件、IP 和平臺開發 : 為硬件平臺創建 PL IP 塊、創建 PL 內核、功能仿真以及評估 AMD

2023-10-25 16:15:02 352

352

AT32 工程在 M3 內核芯片上運行進入硬件錯誤處理函數(HardFault_Handler)?

2023-10-20 06:48:18

內核是使用Xilinx Vivado設計套件交付的經過全面驗證的解決方案設計。此外,還提供了Verilog示例設計。

2023-10-16 10:57:17 358

358

符合實際情況的,以此進行優化。 加載位置 內核鏡像可以由 kernel 自解壓,也可以由 uboot 進行解壓。 對于 kernel 自解壓的情況,如果壓縮過的 kernel 與解壓后的 kernel

2023-10-04 15:07:00 335

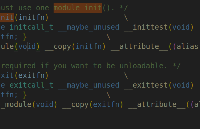

335 ? module ?taints?kernel 幾個可能原因: 模塊沒有聲明 GPL 協議 當前linux內核版本和編譯模塊使用的內核版本不一致 使用內核源代碼未包含的樹外模塊 printk和printf 在內核中的打印函數是 printk , printk 和 printf 的行

2023-09-26 16:58:48 460

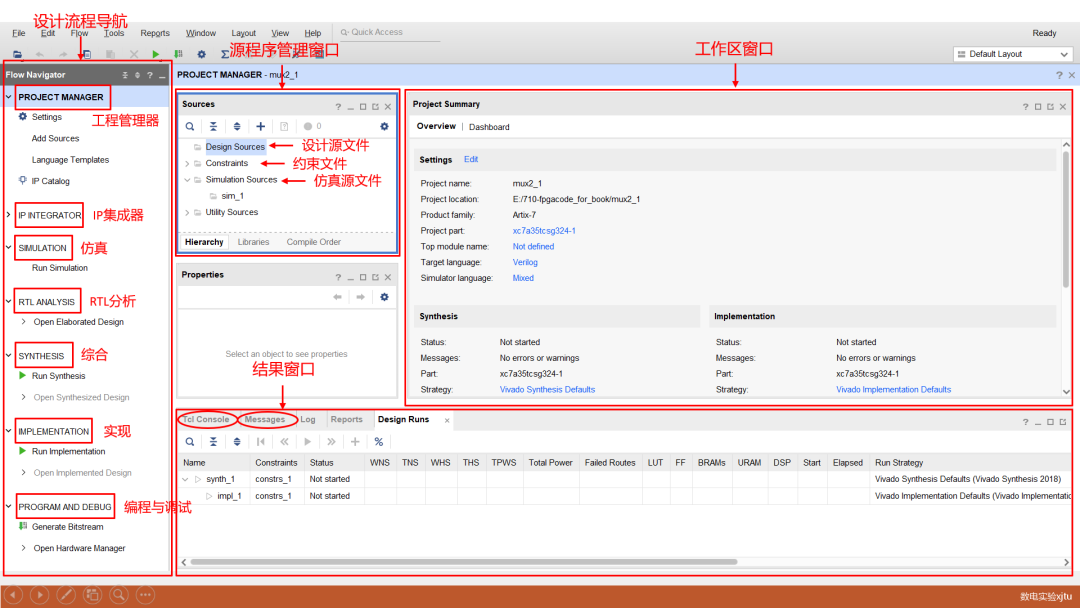

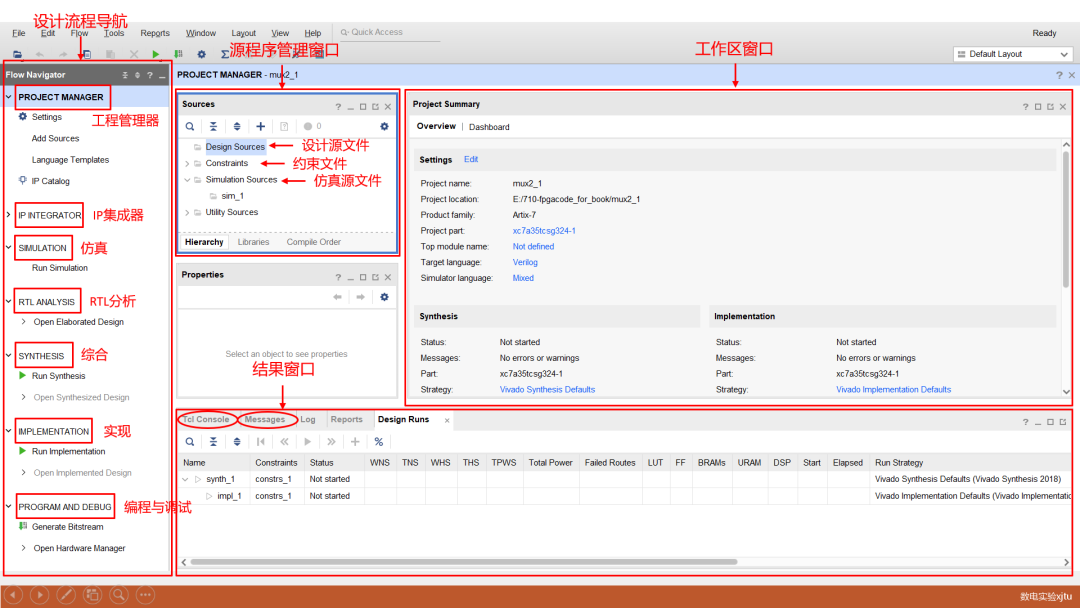

460 Vivado 設計分為 Project Mode 和 Non-project Mode 兩種模式,一般簡單設計中,我們常用的是 Project Mode。在本手冊中,我們將以一個簡單的實驗案例,一步一步的完成 Vivado的整個設計流程。

2023-09-20 07:37:39

想到要寫這一系列關于工具和方法學的小文章是在半年多前,那時候Vivado?已經推出兩年,陸續也接觸了不少客戶和他們的設計。我所在的部門叫做“Tools & Methodology

2023-09-20 06:31:14

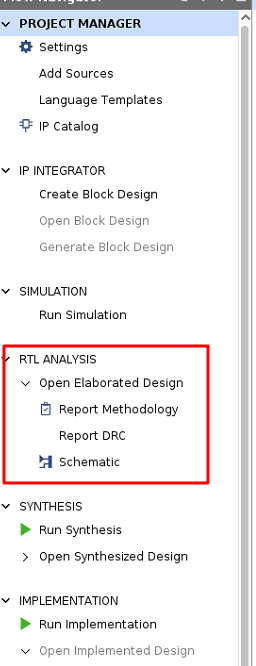

Vivado設計主界面,它的左邊是設計流程導航窗口,是按照FPGA的設計流程設置的,只要按照導航窗口一項一項往下進行,就會完成從設計輸入到最后下載到開發板上的整個設計流程。

2023-09-17 15:40:17 1491

1491

Vivado是Xilinx公司2012年推出的新一代集成開發環境,它強調系統級的設計思想及以IP為核心的設計理念,突出IP核在數字系統設計中的作用。

2023-09-17 15:37:31 1059

1059

電子發燒友網站提供《Vivado設計套件用戶指南(設計流程概述).pdf》資料免費下載

2023-09-15 09:55:07 1

1 電子發燒友網站提供《Vivado Design Suite教程:動態功能交換.pdf》資料免費下載

2023-09-14 15:13:43 0

0 電子發燒友網站提供《Vivado設計套件用戶指南:使用Tcl腳本.pdf》資料免費下載

2023-09-14 14:59:39 0

0 電子發燒友網站提供《Vivado ML版中基于ML的路由擁塞和延遲估計.pdf》資料免費下載

2023-09-14 11:41:08 0

0 電子發燒友網站提供《Vivado設計套件Tcl命令參考指南.pdf》資料免費下載

2023-09-14 10:23:05 1

1 電子發燒友網站提供《Vivado設計套件用戶指南.pdf》資料免費下載

2023-09-14 09:55:18 2

2 電子發燒友網站提供《Vivado Design Suite用戶指南:使用約束.pdf》資料免費下載

2023-09-13 15:48:39 0

0 電子發燒友網站提供《Vivado Design Suite用戶指南:綜合.pdf》資料免費下載

2023-09-13 15:47:40 0

0 電子發燒友網站提供《Vivado設計套件用戶指南:邏輯仿真.pdf》資料免費下載

2023-09-13 15:46:41 0

0 電子發燒友網站提供《Vivado Design Suite用戶指南:使用Tcl腳本.pdf》資料免費下載

2023-09-13 15:26:43 0

0 電子發燒友網站提供《Vivado設計套件用戶:使用Vivado IDE的指南.pdf》資料免費下載

2023-09-13 15:25:36 3

3 電子發燒友網站提供《Vivado Design Suite用戶指南:I/O和時鐘規劃.pdf》資料免費下載

2023-09-13 15:10:58 0

0 電子發燒友網站提供《Vivado Design Suite用戶指南:編程和調試.pdf》資料免費下載

2023-09-13 14:47:21 0

0 電子發燒友網站提供《Vivado設計套件用戶指南:編程和調試.pdf》資料免費下載

2023-09-13 11:37:38 0

0 電子發燒友網站提供《UltraFast Vivado HLS方法指南.pdf》資料免費下載

2023-09-13 11:23:19 0

0 電子發燒友網站提供《Vivado隔離驗證器用戶指南.pdf》資料免費下載

2023-09-13 11:11:15 0

0 電子發燒友網站提供《將VIVADO HLS設計移植到CATAPULT HLS平臺.pdf》資料免費下載

2023-09-13 09:12:46 2

2 Xilinx官網:www.xilinx.com; 2)選中Support菜單下的Downloads&Licensing;3)選擇對應系統;2.2Vivado安裝(2015.4為例)1)運行

2023-09-06 17:55:44

在給Vivado中的一些IP核進行配置的時候,發現有Shared Logic這一項,這里以Tri Mode Ethernet MAC IP核為例,如圖1所示。

2023-09-06 17:05:12 528

528

FPGA開發中使用頻率非常高的兩個IP就是FIFO和BRAM,上一篇文章中已經詳細介紹了Vivado FIFO IP,今天我們來聊一聊BRAM IP。

2023-08-29 16:41:49 2604

2604

:Vivado使用‘/’);

3) 在Tcl命令框中,輸入命令:source ./ Oscilloscope.tcl。輸入完畢按回車,運行Tcl;

4) 等待Tcl綜合、實現、生成比特流文件;

5) 在

2023-08-17 19:31:54

新人小白求助各位大佬,在vivado中配置了e203項目,但是在仿真階段發現,PC值直到仿真結束都是0,x3寄存器的值為X,但是ITCM中讀入了指令,不知道在哪個環節出了問題,希望大佬可以為我指點迷津。

2023-08-12 07:56:14

} [get_drc_checks NSTD-1].NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command), add

2023-08-12 07:54:28

原來仿真使用的是vivado simulator,最近將vivado的仿真器改成modelsim,發現仿真的時候modelsim的transcript沒法打印出e203實時運行的信息。請問要在modelsim中設置什么地方嗎

2023-08-11 09:47:12

幫到不經常看群消息的小伙伴,另一方面也算是我們的技術積累。 Q:Vivado的Implementation階段約束報警告? ? [Vivado?12-627]?No?clocks?matched

2023-08-08 14:10:48 710

710 本文詳細介紹了vivado軟件和modelsim軟件的安裝,以及vivado中配置modelsim仿真設置,每一步都加文字說明和圖片。

2023-08-07 15:48:00 1478

1478

Vivado IP核提供了強大的FIFO生成器,可以通過圖形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 1616

1616

雙擊桌面圖標打開Vivado 2017.2,或者選擇開始>所有程序>Xilinx Design Tools> Vivado 2017.2>Vivado 2017.2;

2023-07-30 09:39:11 399

399

電子發燒友網報道(文/李彎彎)日前,在2023世界半導體大會暨南京國際半導體博覽會上,高通全球副總裁孫剛發表演講時談到,目前高通能夠支持參數超過10億的模型在終端上運行,未來幾個月內超過100億參數

2023-07-26 00:15:00 1058

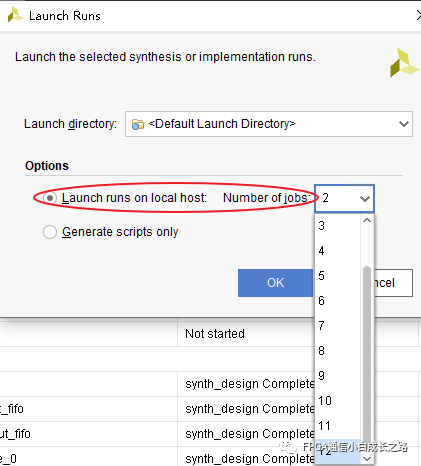

1058 Vivado中對工程進行綜合時,會彈出如下對話框

2023-07-24 15:28:54 489

489

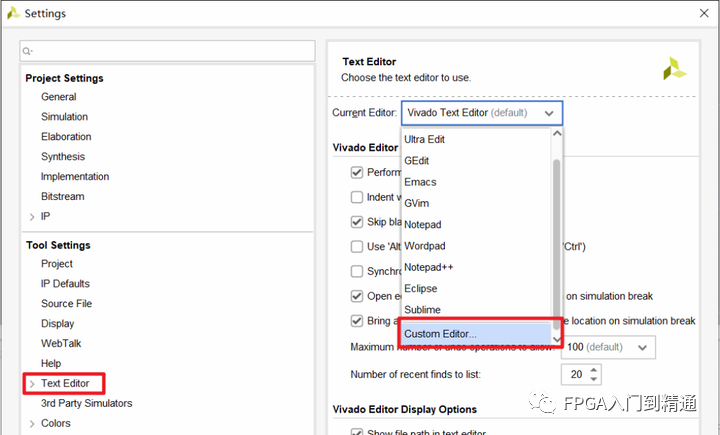

Modelsim是十分常用的外部仿真工具,在Vivado中也可以調用Modelsim進行仿真,下面將介紹如何對vivado進行配置并調用Modelsim進行仿真,在進行仿真之前需要提前安裝Modelsim軟件。

2023-07-24 09:04:43 1817

1817

vivado開發軟件自帶了仿真工具,下面將介紹vivado的仿真流程,方便初學者進行仿真實驗。

2023-07-18 09:06:59 2131

2131

vivado的工程創建流程對于大部分初學者而言比較復雜,下面將通過這篇博客來講解詳細的vivado工程創建流程。幫助自己進行學習回顧,同時希望可以對有需要的初學者產生幫助。

2023-07-12 09:26:57 1098

1098

使用“時鐘校準去歪斜”時,在 Vivado 中會顯示下列消息以指明是否啟用該功能特性

2023-07-07 14:14:50 347

347

Linux操作系統是當今世界上最為廣泛使用的開源操作系統之一,內核則是一個操作系統的核心和靈魂所在。對于一名Linux驅動開發者來說,了解Linux內核的運行機制和Linux內核提供的一些關鍵功能(如虛擬內存管理、進程管理、文件系統、網絡協議棧等)都是我們日常工作和學習的重點。

2023-07-06 11:46:41 1041

1041

Vivado綜合默認是timing driven模式,除了IO管腳等物理約束,建議添加必要的時序約束,有利于綜合邏輯的優化,同時綜合后的design里面可以評估時序。

2023-07-03 09:03:19 414

414 IDE 上運行 Tcl 腳本主要有以下幾個渠道。

Tcl Console

Vivado IDE 的最下方有一個 Tcl Console,在運行過程中允許用戶輸入 Tcl/XDC 命令或是 source

2023-06-28 19:34:58

今天介紹一下,如何在Vivado中添加時序約束,Vivado添加約束的方法有3種:xdc文件、時序約束向導(Constraints Wizard)、時序約束編輯器(Edit Timing Constraints )

2023-06-26 15:21:11 1834

1834

FPGA開發過程中,vivado和quartus等開發軟件都會提供時序報告,以方便開發者判斷自己的工程時序是否滿足時序要求。

2023-06-23 17:44:00 531

531

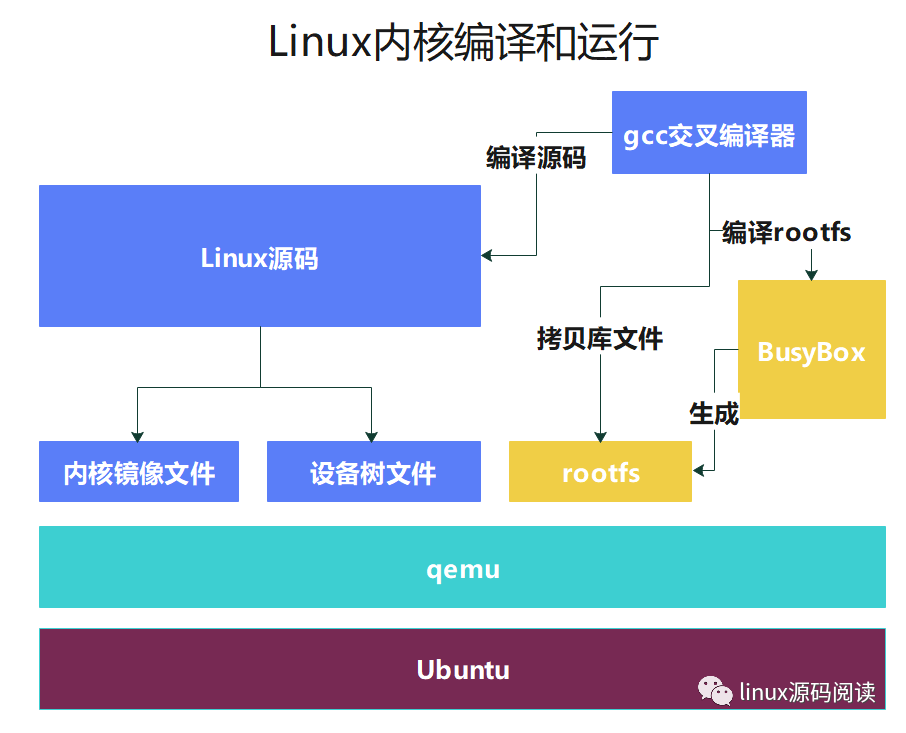

想讓Linux內核代碼跑起來,得先搭建編譯和運行代碼的環境。

2023-06-23 11:56:00 322

322

在仿真Vivado IP核時分兩種情況,分為未使用SECURE IP核和使用了SECURE IP核。

2023-06-20 14:23:57 622

622

Vivado Schematic中的實線和虛線有什么區別?

2023-06-16 16:53:42 698

698

電子發燒友網站提供《為EBAZ4205創建Xilinx Vivado板文件.zip》資料免費下載

2023-06-16 11:41:02 1

1 電子發燒友網站提供《在Artix 7 FPGA上使用Vivado的組合邏輯與順序邏輯.zip》資料免費下載

2023-06-15 09:14:49 0

0 在仿真Vivado IP核時分兩種情況,分為未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 1240

1240

Vivado Schematic中的實線和虛線有什么區別?

2023-06-06 11:13:39 670

670

我目前正在評估 imxrt1170 的新產品,但我無法獲得任何在 m4 內核上運行的示例。所有示例都在 m7 上完美運行,但由于未知原因,它們不會在 m4 上運行。事實上,mculink 沒有連接

2023-05-18 08:09:29

Vivado 軟件提供了HDL編寫中常用的示例,旨在幫助初學者更好地理解和掌握HDL編程,這里分享一下verilog代碼示例。

2023-05-16 16:58:06 627

627 如果你正在使用Vivado開發套件進行設計,你會發現綜合設置中提供了許多綜合選項。這些選項對綜合結果有著潛在的影響,而且能夠提升設計效率。為了更好地利用這些資源,需要仔細研究每一個選項的功能。本文將要介紹一下Vivado的綜合參數設置。

2023-05-16 16:45:50 1856

1856

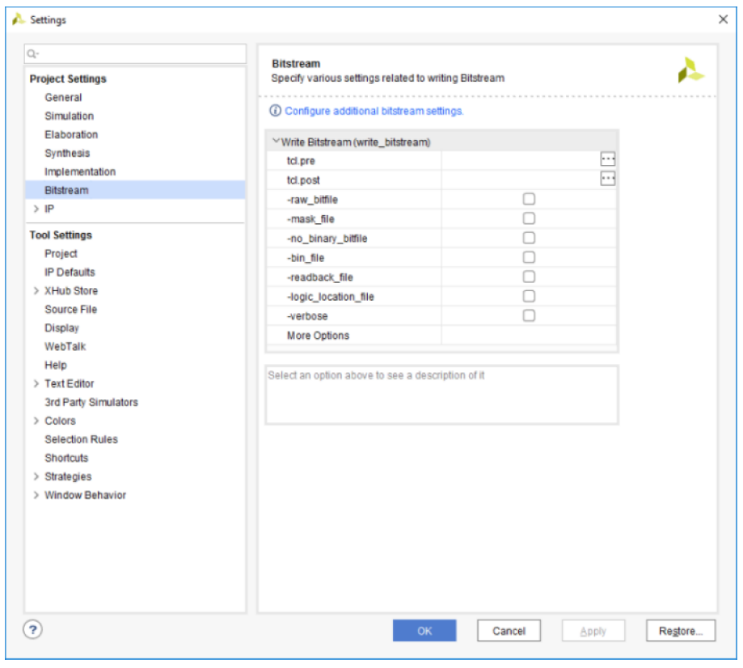

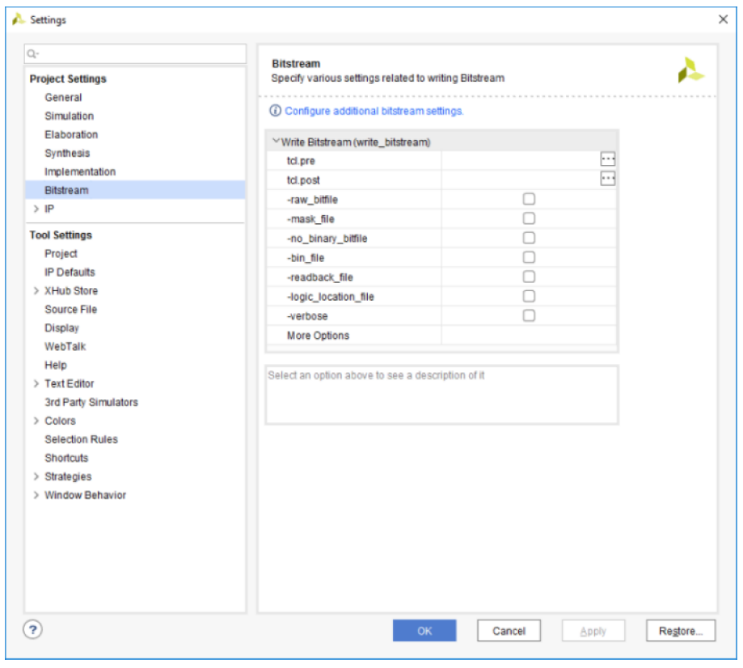

本文主要介紹Vivado布線參數設置,基本設置方式和vivado綜合參數設置基本一致,將詳細說明如何設置布線參數以優化FPGA設計的性能,以及如何設置Vivado壓縮BIT文件。

2023-05-16 16:40:45 2955

2955

Vivado是一個非常強大的工具,但是在一些方面可能不能完全滿足我們的需求,比如代碼編輯器的功能。幸運的是,Vivado允許我們關聯第三方編輯器來擴展其代碼編輯器的功能。本文將介紹如何配置Vivado與第三方編輯器一起使用,并提供一些實用技巧和建議。

2023-05-16 16:36:18 771

771

有一天使用Vivado調用questasim(modelsim估計也一樣),仿真報錯

2023-05-08 17:12:56 1758

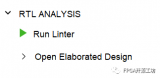

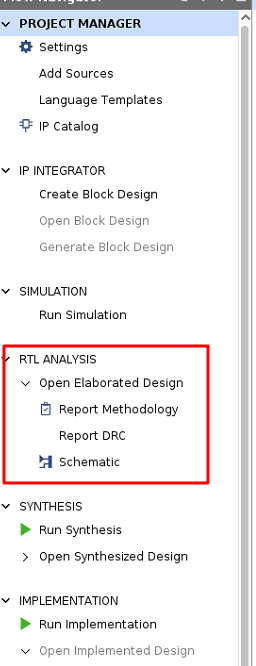

1758 在Vivado的界面中,有個RTL ANALYSIS->Open Elaborated Design的選項,可能很多工程師都沒有使用過。因為大家基本都是從Run Synthesis開始的。

2023-05-05 16:00:18 803

803

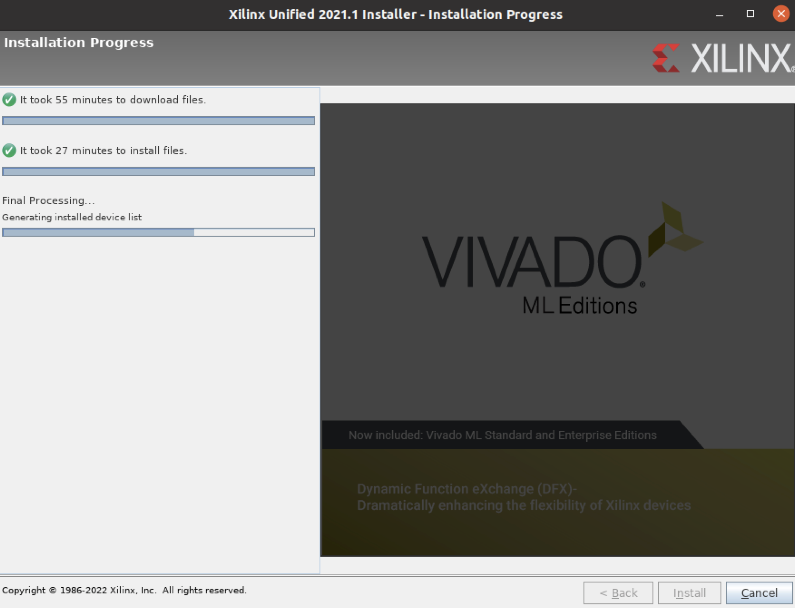

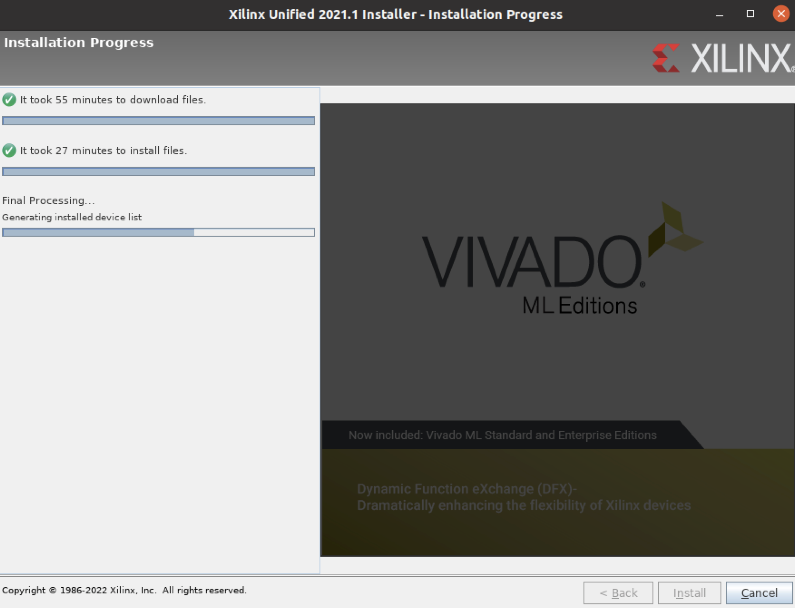

在ubuntu上安裝vivado2021.1時,一直卡在最后一步:generating installed device list

安裝其他版本也出現過該問題。

2023-05-05 15:51:38 1672

1672

關于 Tcl 在 Vivado中的應用文章從 Tcl 的基本語法和在 Vivado 中的 應用展開,繼上篇《用 Tcl 定制 Vivado 設計實現流程》介紹了如何擴展甚 至是定制 FPGA

2023-05-05 15:34:52 1612

1612

今天推出Xilinx已發布的《Vivado使用誤區與進階》系列:用TCL定制Vivado設計實現流程。

2023-05-05 09:44:46 674

674

《XDC 約束技巧》系列中討論了XDC 約束的設置方法、約束思路和一些容易混淆的地方。我們提到過約束是為了設計服務,寫入 Vivado中 的 XDC 實際上就是用戶設定的目標,Vivado

2023-05-04 11:20:31 2368

2368

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸載過Modelsim,用vivado打開過ISE工程,因為工程中很多IP核不能用所以在重新生成過程中發現了這個問題,還請大神告知是怎么回事?

2023-04-24 23:42:21

你好是否有機會讓 busfreq 驅動程序在主線內核上運行?在我看來,如果沒有它,我無法以高于 1M 波特的速度可靠地運行 UART...(我正在尋找 3M 波特串行通信)

2023-04-18 10:30:12

Xilinx的新一代設計套件Vivado相比上一代產品 ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言 XDC 以及腳本語言 Tcl 的引入則成為

2023-04-15 09:43:09 956

956 Vivado是Xilinx推出的可編程邏輯設備(FPGA)軟件開發工具套件,提供了許多TCL命令來簡化流程和自動化開發。本文將介紹在Vivado中常用的TCL命令,并對其進行詳細說明,并提供相應的操作示例。

2023-04-13 10:20:23 1544

1544 ACCYKITZYBOW/VIVADO

2023-03-30 12:05:04

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

今天我要跟大家分享一下Linux內核的重要性。內核就像Linux系統運行的大心臟,對系統的運行起到了至關重要的作用。那么Linux內核到底難不難學呢?今天我就大概和大家科普一下,后期還會向大家

2023-03-24 15:16:40 558

558

內核是與計算機硬件接口的易替換軟件的最低級別。它負責將所有以“用戶模式”運行的應用程序連接到物理硬件,并允許稱為服務器的進程使用進程間通信(IPC)彼此獲取信息。

2023-03-24 11:23:33 1510

1510

電子發燒友App

電子發燒友App

硬聲App

硬聲App

145

145

636

636 391

391

454

454 0

0 317

317 410

410 512

512

352

352

358

358

335

335 460

460 1491

1491

1059

1059

0

0 0

0 2

2 528

528

2604

2604

710

710 1478

1478

399

399

1058

1058 1817

1817

1098

1098

1041

1041

414

414 1834

1834

0

0 1856

1856

2955

2955

771

771

803

803

1672

1672

1612

1612

2368

2368

956

956 1544

1544 558

558

1510

1510

評論