AD783要求一個寬度為150 ns至250 ns的窄正采樣脈沖。為使顯示的波形保持穩定,無來回跳動,采樣脈沖必須非常穩定,抖動很低。這一要求往往將可能的時鐘選擇限定于晶體振蕩器。另一個

2012-04-18 11:54:39 5607

5607

本系列文章共有三部分,第 1 部分重點介紹如何準確地估算某個時鐘源的抖動,以及如何將其與 ADC 的孔徑抖動組合。在第 2 部分中,該組合 抖動 將用于計算 ADC 的 SRN,然后將其與實際

2012-05-07 11:37:30 2668

2668

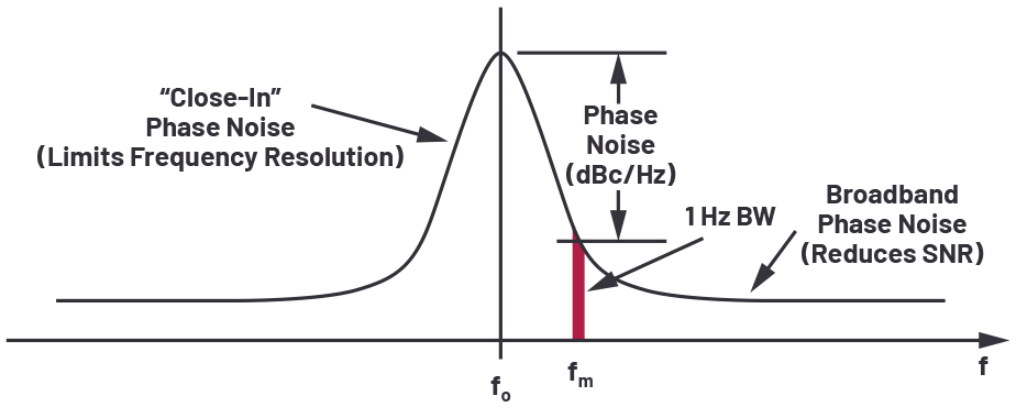

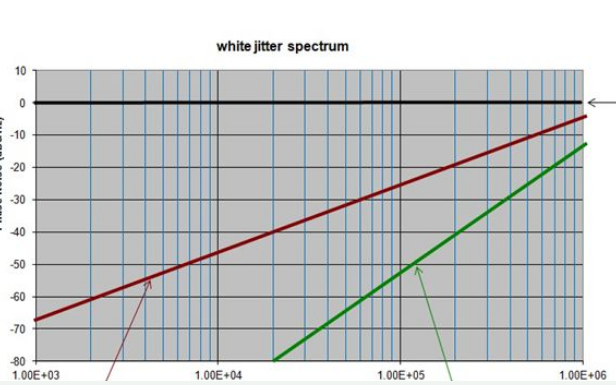

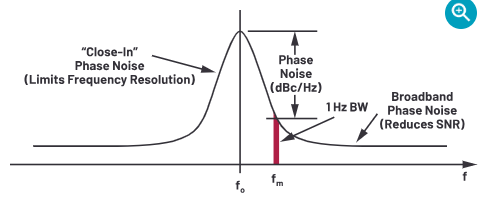

為了正確理解時鐘相關器件的抖動指標規格,同時選擇抖動性能適合系統應用的時鐘解決方案,本文詳細介紹了如何理解兩種類型時鐘驅動器的抖動參數,以及從鎖相環輸出噪聲特性理解時鐘器件作為合成器、抖動濾除功能時的噪聲特性。

2013-06-21 15:40:41 14342

14342

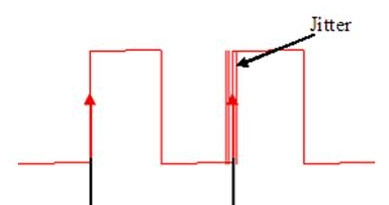

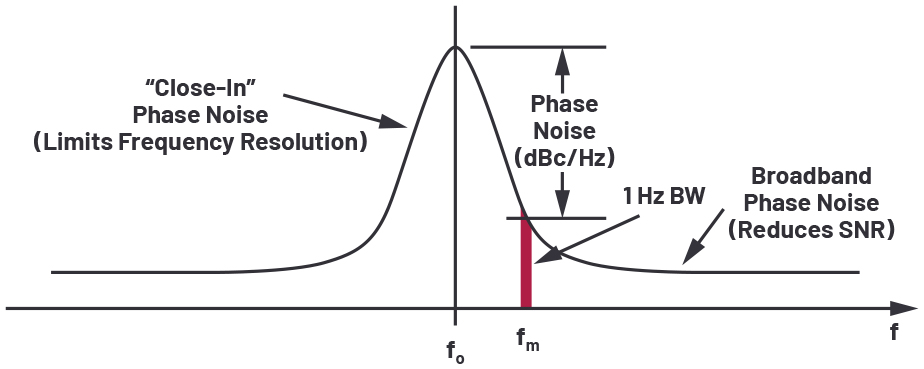

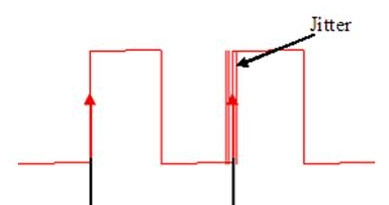

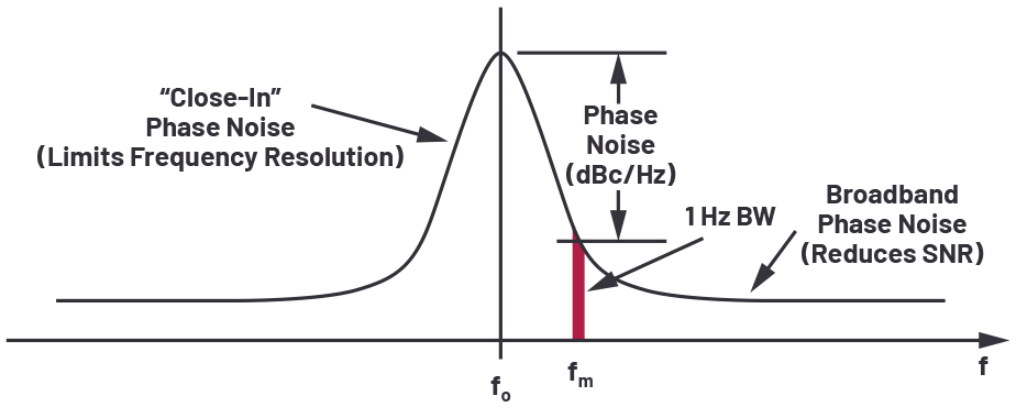

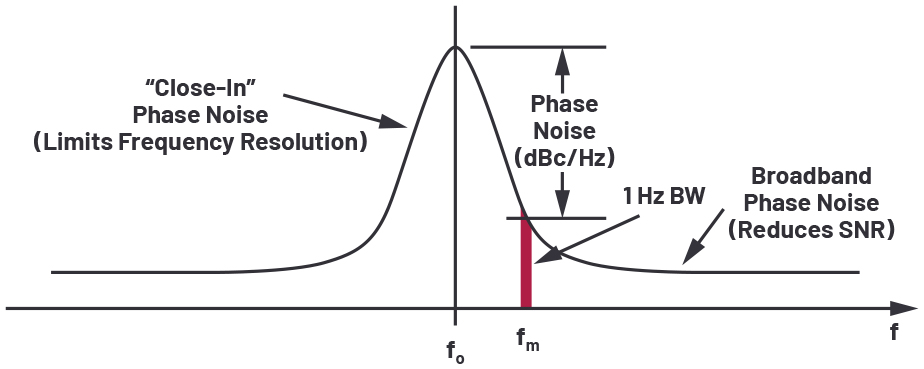

抖動一般定義為信號在某特定時刻相對于其理想位置的短期偏移。這個短期偏移在時域的表現形式為抖動(下文的抖動專指時域抖動),在頻域的表現形式為相噪。本文主要探討下時鐘抖動和相噪以及其測量方法,以及兩者之間的關系。

2016-01-18 10:54:11 24276

24276

-Si539x時鐘提升頻率靈活性和抖動性能--Si56x Ultra Series? XO/VCXO提供最大可達3GHz的任意頻率時鐘-。

2018-06-26 15:19:41 7075

7075 時鐘抖動技術適合于各種周期性的脈沖信號,典型的是電力電子設備中的PWM電壓和數字電路中的時鐘信號。

2023-09-11 10:55:34 503

503

時鐘抖動是相對于理想時鐘沿實際時鐘存在不隨時間積累的、時而超前、時而滯后的偏移稱為時鐘抖動,簡稱抖動

2023-11-08 15:08:01 892

892

當DAQ信號鏈被隔離之后,控制采樣保持開關的信號一般來自進行多通道同步采樣的背板。系統設計人員選擇低抖動數字隔離器至關重要,以使進入ADC的采樣保持開關的控制信號具有低抖動。

2022-03-16 11:53:34 2696

2696

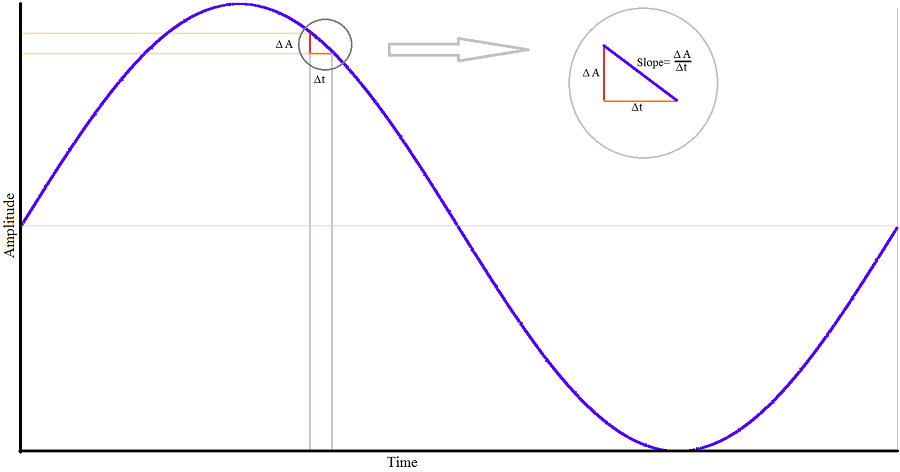

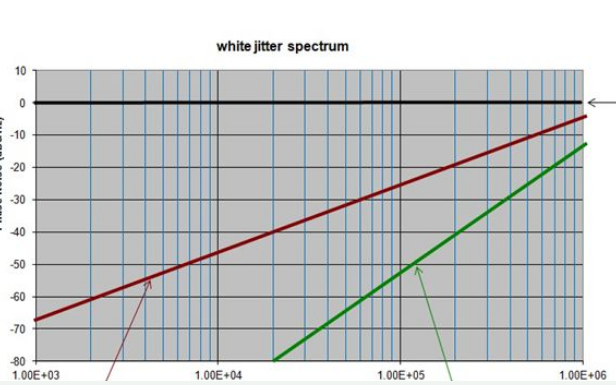

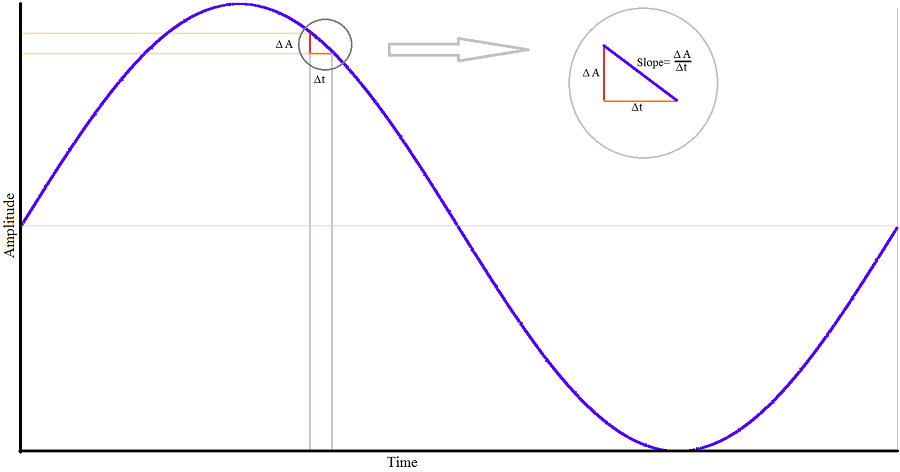

在本文中,我們將討論抖動傳遞及其性能,以及相位噪聲測量技術的局限性。 時鐘抖動和邊沿速率 圖1顯示了由一個通用公式表述的三種波形。該公式包括相位噪聲項“φ(t)”和幅度噪聲項“λ(t)。對評估的三個

2022-11-23 07:59:49

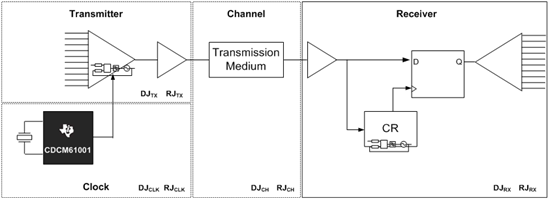

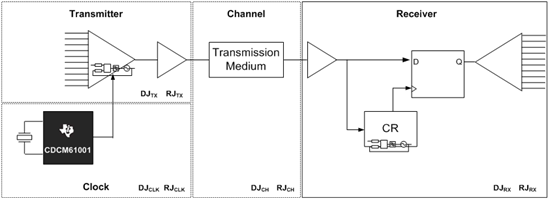

作者:John Johnson,德州儀器 本文介紹時鐘抖動對高速鏈路性能的影響。我們將重點介紹抖動預算基礎。 用于在更遠距離對日益增長的海量數據進行傳輸的一些標準不斷出現。來自各行業的工程師們組成

2018-09-19 14:23:47

本文介紹時鐘抖動對高速鏈路性能的影響。我們將重點介紹抖動預算基礎。 用于在更遠距離對日益增長的海量數據進行傳輸的一些標準不斷出現。來自各行業的工程師們組成了各種委員會和標準機構,根據其開發標準的目標

2022-11-23 06:59:24

轉時鐘抖動的理解

2016-10-05 12:08:25

很多人都知道,抖動(這是時鐘邊沿不確定性)是不好的現象,其不僅可導致噪聲增加,而且還會降低數據轉換器的有效位數 (ENOB)。例如,如果系統需要 100MHz 14(最小值)位的 ENOB,我們

2022-11-21 07:26:27

上升沿。圖1 —LMK03806(具有時鐘發生器、時鐘分頻器和驅動器)的方框圖因此,您下次設計采樣系統時,別忘了考慮時鐘抖動性能,因為這會影響整體動態范圍。其它資源:閱讀我們的最新博客系列《定時決定一切

2018-09-13 14:18:06

采樣時鐘考量在高性能采樣數據系統中,應使用低相位噪聲晶體振蕩器產生ADC(或DAC)采樣時鐘,因為采樣時鐘抖動會調制模擬輸入/輸出信號,并提高噪聲和失真底。采樣時鐘發生器應與高噪聲數字電路隔離

2014-11-20 10:58:30

DN1013- 了解時鐘抖動對高速ADC的影響

2019-07-17 06:41:39

變形。在圖5中,您可以看到時鐘信號電平的切換距離是不均勻的;這就是時鐘的抖動。 盡管上圖抖動較為夸張,但是它說明了抖動的時鐘會導致采樣在不均勻的時間間隔上觸發。 這種不均勻導致要記錄和復制的波形發生

2019-06-12 08:00:00

如何推導ADC的SNR?如何準確地估算某個時鐘源的抖動?如何將其與ADC的孔徑抖動組合?

2021-05-13 06:17:20

采樣時鐘抖動對ADC信噪比的性能有什么影響?如何實現低抖動采樣時鐘電路的設計?

2021-04-14 06:49:20

你知道RMS周期抖動? RMS周期抖動經驗法則是什么? 實驗室測量例子有沒有可以進行參考? 如何知曉估算RMS周期間抖動經驗法則?

2021-03-11 06:58:41

。這工作正常,直到我決定董事會所做的測量不夠準確(在時間軸上)。因此,我將生成的時鐘使能信號(2MHz)輸出到IO-Pin,并使用示波器測量頻率抖動。抖動似乎具有高斯分布,標準偏差約為28ns。我還測量

2020-08-19 06:09:57

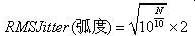

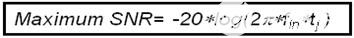

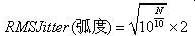

高信噪比=低ADC孔徑抖動嗎?在設計中,為了避免降低ADC的性能,工程師一般會采用抖動極低的采樣時鐘。然而,用于產生采樣時鐘的振蕩器常常用相位噪聲而非時間抖動來描述特性。那么,有木有方法將振蕩器相位噪聲轉換為時間抖動呢?

2019-08-13 06:27:54

變形。在圖5中,您可以看到時鐘信號電平的切換距離是不均勻的;這就是時鐘的抖動。 盡管上圖抖動較為夸張,但是它說明了抖動的時鐘會導致采樣在不均勻的時間間隔上觸發。 這種不均勻導致要記錄和復制的波形發生

2016-01-18 15:31:09

需求。作為該最新博客系列的開篇文章,我將幫助您了解如何正確測量時鐘緩沖器的附加抖動。為什么抖動很重要?在當今數據通信、有線及無線基礎設施以及其它高速應用等高級系統中,時鐘抖動是整體系統性能的關鍵因素。要

2018-09-13 14:38:43

設計采樣系統時,關于時鐘抖動性能如何考慮?抖動對時鐘采樣系統有何影響?

2021-04-06 06:07:38

一塊音視頻處理芯片輸出1080i的數據Data及其同步時鐘Clk,但是時鐘clk的抖動很大,我該如何處理呢?另外,抖動很大的時鐘源能否在后面接入一個模擬鎖相環降低時鐘的抖動呢?

2018-11-12 09:12:43

時鐘抖動或結束時鐘抖動的最佳方法是什么?

2021-03-17 07:04:07

隨著數據速率的提高,時鐘抖動分析的需求也在與日俱增。在高速串行數據鏈路中,時鐘抖動會影響發射機、傳輸線和接收機的數據抖動。保證時鐘質量的測量也在不斷發展

2008-12-27 12:24:05 6

6 隨著數據速率的提高,時鐘抖動分析的需求也在與日俱增。在高速串行數據鏈路中,時鐘抖動會影響發射機、傳輸線和接收機的數據抖動。保證時鐘質量的測量也在不斷發展。目前

2009-07-07 14:01:21 20

20 本文主要討論采樣時鐘抖動對ADC 信噪比性能的影響以及低抖動采樣時鐘電路的設計。

2009-11-27 11:24:07 15

15 本文分析了晶振的漂移對GPS 接收機的影響,從鎖相環理論的角度,重點分析了采樣時鐘抖動對基帶載波跟蹤和偽碼跟蹤性能的影響,并給出一種環路分級降帶寬的方法來消除這種

2009-12-19 13:49:58 19

19 高速互聯鏈路中參考時鐘的抖動分析與測量

在高速互聯鏈路中,發送器的參考工作時鐘的抖動是影響整個

2010-04-15 14:01:39 19

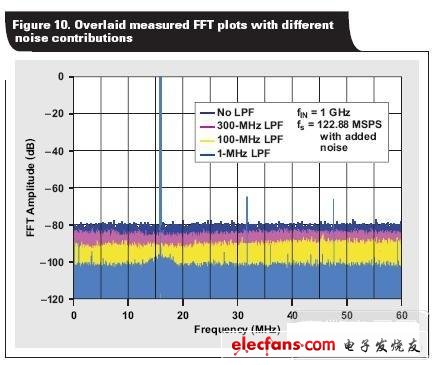

19 隨著支持直接IF采樣的更高分辨率數據轉換器的上市,系統設計師在選擇低抖動時鐘電路時,需要在性能/成本之間做出權衡取舍。許多用于標定時鐘抖動的傳統方法都不適用于數

2010-11-27 17:12:46 32

32

抖動的概念和抖動的測量方法

在數字通信系統,特別是同步系統中,隨著系統時鐘頻率的不斷提高,時間抖動成為影響通

2008-11-27 08:28:11 4050

4050

該應用筆記提出了超低抖動時鐘合成器的一種設計思路,其目標是產生2GHz時鐘時,邊沿之間的抖動< 100fs。分析和仿真結果表明,要達到這一抖動指標,設計難度遠遠高于預期。關

2009-04-21 23:14:05 723

723

摘要:該應用筆記提出了超低抖動時鐘合成器的一種設計思路,其目標是產生2GHz時鐘時,邊沿之間的抖動< 100fs。分析和仿真結果表明,要達到這一抖動指標,設計難度遠遠高于預

2009-04-22 09:35:13 296

296

摘要:這是一篇關于時鐘(CLK)信號質量的應用筆記,介紹如何測量抖動和相位噪聲,包括周期抖動、逐周期抖動和累加抖動。本文還描述了周期抖動和相位噪聲譜之間的關系,并介紹

2009-04-22 10:16:50 3736

3736

摘要:該應用筆記提出了超低抖動時鐘合成器的一種設計思路,其目標是產生2GHz時鐘時,邊沿之間的抖動< 100fs。分析和仿真結果表明,要達到這一抖動指標,設計難度遠遠高于預

2009-04-25 09:54:26 482

482

摘要:該應用筆記提出了超低抖動時鐘合成器的一種設計思路,其目標是產生2GHz時鐘時,邊沿之間的抖動< 100fs。分析和仿真結果表明,要達到這一抖動指標,設計難度遠遠高于預

2009-05-08 10:19:03 431

431

相位噪聲和抖動的概念及其估算方法

時鐘頻率的不斷提高使相位噪聲和抖動在系統時序上占據日益重要的位置。本文介其概念及其對系統性能的影

2009-12-27 13:30:21 2173

2173

理解不同類型的時鐘抖動

抖動定義為信號距離其理想位置的偏離。本文將重點研究時鐘抖動,并探討下面幾種類型的時鐘抖動:相鄰周期抖動、周期抖動、時間間隔誤

2010-01-06 11:48:11 1608

1608

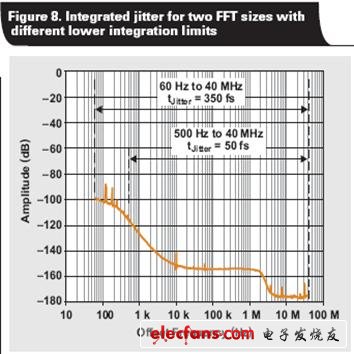

模數和數模轉換器采樣時鐘內的抖動會對可實現的最大信噪比造成限制(參見參考文獻部分van de Plassche著《集成模數和數模轉換器》)。本應用筆記闡述了相位噪聲和抖動的定義,繪制

2011-11-24 14:31:55 75

75 時鐘抖動時域分析(下):

2012-05-08 15:26:25 29

29 如果明智地選擇時鐘,一份簡單的抖動規范幾乎是不夠的。而重要的是,你要知道時鐘噪聲的帶寬和頻譜形狀,才能在采樣過程中適當地將它們考慮進去。很多系統設計師對數據轉換器

2012-05-08 15:29:00 47

47 介紹 此應用筆記側重于不同類型的時鐘抖動。時鐘抖動是從它的時鐘邊沿偏差理想的位置。了解時鐘抖動非常重要在應用中,因為它起著關鍵作用,在時間預算一個系統。 隨著系統數據速率的增加,定時抖動成為關鍵

2017-04-01 16:13:18 6

6 很多人都知道,抖動(這是時鐘邊沿不確定性)是不好的現象,其不僅可導致噪聲增加,而且還會降低數據轉換器的有效位數 (ENOB)。例如,如果系統需要 100MHz 14(最小值)位的 ENOB,我們

2017-04-08 04:51:23 1266

1266

了解高速ADC時鐘抖動的影響將高速信號數字化到高分辨率要求仔細選擇一個時鐘,不會妥協模數轉換器的采樣性能(ADC)。 在這篇文章中,我們希望給讀者一個更好的了解時鐘抖動及其影響高速模數轉換器的性能

2017-05-15 15:20:59 13

13 級,從而降低成本和功耗。在欠采樣接收機設計中必須要特別注意采樣時鐘,因為在一些高輸入頻率下時鐘抖動會成為限制信噪比(SNR) 的主要原因。 本系列文章共有三部分,第1 部分重點介紹如何準確地估算某個時鐘源的抖動,以及如何將其與AD

2017-05-18 09:47:38 1

1 采樣時鐘抖動可對高性能ADCs信噪比性能的災難。雖然信噪比和抖動之間的關系是眾所周知的,但是大多數振蕩器都是根據相位噪聲來指定的。

2017-08-03 10:57:33 13

13 時鐘抖動時域分析,第 2 部分

2017-10-26 16:10:42 6

6 時鐘抖動時域分析 第 3 部分

2017-10-26 16:13:28 4

4 時間域中分析的時鐘抖動,第 1 部分

2017-10-26 16:16:23 4

4 時鐘產生抖動(jitter)會使發生抖動的時鐘信號與未發生抖動的時鐘信號在時域上存在偏差,從而使模數轉換器的采樣頻率發生紊亂,最終導致模數轉換器采樣的不穩定性,使輸出信號存在頻譜毛刺,導致誤碼率上升

2017-11-11 18:22:26 9

9 本文分析了晶振的漂移對 GPS 接收機的影響,從鎖相環理論的角度,重點分析了采樣時鐘抖動對基帶載波跟蹤和偽碼跟蹤性能的影響,并給出一種環路分級降帶寬的方法來消除這種影響。該方法在保證最終偽碼跟蹤精度

2017-11-27 14:45:05 8

8 本文主要討論采樣時鐘抖動對 ADC 信噪比性能的影響以及低抖動采樣時鐘電路的設計。 ADC 是現代數字解調器和軟件無線電接收機中連接模擬信號處理部分和數字信號處理部分的橋梁,其性能在很大程度上決定

2017-11-27 14:59:20 17

17 時鐘接口閾值區間附近的抖動會破壞ADC的時序。例如,抖動會導致確定性抖動由干擾引起,會通過某些方式使閾值發生偏移,通常受器件本身特性限制。查看時鐘信號噪聲通常有三種途徑:時域、頻域、相位域。

2018-03-12 13:39:33 21583

21583 仔細觀察某個采樣點,可以看到計時不準(時鐘抖動或時鐘相位噪聲)是如何形成振幅變化的。由于高 Nyquist 區域(例如,f1 = 10 MHz 到 f2 = 110 MHz)欠采樣帶來輸入頻率的增加,固定數量的時鐘抖動自理想采樣點產生更大數量的振幅偏差(噪聲)。

2018-05-14 08:51:40 3

3 該法則很簡單。如果周期抖動分布是高斯或正態分布,則周期間抖動可以根據周期抖動估算如下

2018-07-12 09:10:07 13939

13939

ADI研討會:高性能時鐘: 解密抖動

2019-08-20 06:05:00 1656

1656 時鐘設計人員通常會提供一個相位噪聲,但不提供抖動規格。相位噪聲規格可以轉換為抖動,首先確定時鐘噪聲,然后通過小角度計算將噪聲與主時鐘噪聲成分進行比較。相位噪聲功率通過計算圖9中的灰色區域積分得出。

2019-08-20 11:06:53 7787

7787

時鐘抖動性能主題似乎是時鐘,ADC和電源的當前焦點供應廠家。理由很清楚;時鐘抖動會干擾包括高速ADC在內的數字電路的性能。高速時鐘可以對它們所接收的功率的“清潔度”非常敏感,盡管量化關系需要一些努力。

2019-09-14 11:24:00 7712

7712

本文針對全方位的信號路徑系統中的高速全差分運放及高頻寬14位模擬/數字轉換器的隨機及固定時鐘抖動,具體分析、研究了超低噪聲兼時鐘抖動濾除技術。研究選用雙級聯PLLatinum架構,配置高性能壓控振蕩器(VCXO),很好地實現了降噪和時鐘抖動濾除的作用。

2020-09-23 10:45:00 2

2 AD9524:帶6路差分或13路LVCMOS輸出的抖動凈化器和時鐘發

2021-03-19 07:03:02 10

10 AN-1221: 使用ADF4002 PLL產生高速模數轉換器所需的極低抖動編碼(采樣)時鐘

2021-03-19 08:59:00 13

13 MT-200:降低ADC時鐘接口抖動

2021-03-21 01:18:30 7

7 AD9525: 8路LVPECL輸出低抖動時鐘發生器

2021-03-21 15:00:20 0

0 電子發燒友網為你提供相位噪聲處理:時鐘抖動或結束時鐘抖動的最佳方法是什么?資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-04 08:49:06 26

26 前言 :本文我們介紹下ADC采樣時鐘的抖動(Jitter)參數對ADC采樣的影響,主要介紹以下內容: 時鐘抖動的構成 時鐘抖動對ADC SNR的影響 如何計算時鐘抖動 如何優化時鐘抖動 1.采樣理論

2021-04-07 16:43:45 7378

7378

超低抖動時鐘的產生與分配

2021-04-18 14:13:51 8

8 AN-1576:采用AD9958 500 MSPS DDS或AD9858 1 GSPS DDS和AD9515時鐘分配IC的高性能ADC的低抖動采樣時鐘發生器

2021-04-30 09:48:42 13

13 ADC時鐘接口中的最小抖動

2021-05-09 12:19:40 6

6 DN1013-了解時鐘抖動對高速ADC的影響

2021-05-11 18:22:19 0

0 作者:John Johnson,德州儀器?

?

本文介紹時鐘抖動對高速鏈路性能的影響。我們將重點介紹抖動預算基礎。

?

用于在更遠距離對日益增長的海量數據進行傳輸的一些標準不斷出現。來自

2021-11-22 15:52:21 1284

1284

MSP430或STM32,在使用內部ADC出現的采樣數據異常抖動問題采樣設計:用于檢測供電線路電流及電壓。產品運行在兩種模式下,1、低功耗靜態模式(倉儲態),2、全功能全速運行模式(工作態)。在倉儲

2021-12-08 09:06:10 12

12 PCIe 和網絡時鐘抖動測量之間的另一個顯著差異在圖 2 中并不明顯。數字采樣示波器 (DSO) 用于獲取時鐘周期或波形文件以計算 PCIe 時鐘抖動,而不是 PNA。造成這種情況的主要原因是 PCIe 時鐘支持擴頻,而網絡時鐘不支持,而且從歷史上看,PNA 一直無法使用正在擴頻的時鐘。

2022-05-05 15:50:44 4513

4513

高 AC 和 DC 精度,而無需犧牲 DC 精度以獲得更高的采樣率。然而,為了實現高 AC 性能,例如信噪比 (SNR),系統設計人員需要考慮采樣時鐘信號或控制采樣和轉換的轉換啟動信號上的抖動引入的誤差

2022-07-19 16:37:37 1518

1518

時鐘抖動、采樣率和量化噪聲是影響 ADC 中 SNR 和 SFDR 的最關鍵因素

2022-08-11 14:26:08 2684

2684

時鐘采樣系統最大限度減少抖動

2022-11-04 09:52:12 0

0 時鐘抖動使隨機抖動和相位噪聲不再神秘

2022-11-07 08:07:29 4

4 時鐘抖動解秘—高速鏈路時鐘抖動規范基礎知識

2022-11-07 08:07:30 1

1 精度,無需犧牲直流精度來換取更高的采樣速率。然而,為實現高交流性能,如信噪比(SNR),系統設計人員必須考慮采樣時鐘信號或控制ADC中采樣保持(SH)開關的轉換啟動信號上的抖動所帶來的誤差。隨著目標信號和采樣速率的增加,控制采樣保持開

2022-11-13 11:25:11 473

473 對于頻率成分相對較低的輸入信號,例如在1MHz以下,時鐘抖動變得不那么重要,但是當輸入信號的頻率為幾百兆赫茲時,時鐘上的抖動將成為誤差的主要來源,并且將成為SNR的限制因素。

2023-01-03 14:35:04 823

823

1.1.1.??抖動定義和分類 ITU-T G.701對抖動的定義為:“抖動是指數字信號在短期內相對于理想位置發生的偏移重大影響的短時變化”。 對于真實物理世界中的時鐘源,比如晶振、DLL、PLL,它們的時鐘輸出周期都不可能是一個單點的固定值,而是隨時間而變化的

2023-03-10 14:54:32 657

657

系統時序設計中對時鐘信號的要求是非常嚴格的,因為我們所有的時序計算都是以恒定的時鐘信號為基準。但實際中時鐘信號往往不可能總是那么完美,會出現抖動(Jitter)和偏移(Skew)問題。

2023-04-04 09:20:56 1637

1637 首先,我們需要理解什么是時鐘抖動。簡而言之,時鐘抖動(Jitter)反映的是時鐘源在時鐘邊沿的不確定性(Clock Uncertainty)。

2023-06-02 09:09:06 1026

1026

先來聊一聊什么是時鐘抖動。時鐘抖動實際上是相比于理想時鐘的時鐘邊沿位置,實際時鐘的時鐘邊沿的偏差,偏差越大,抖動越大。實際上,時鐘源例如PLL是無法產生一個絕對干凈的時鐘。這就意味著時鐘邊沿出現在

2023-06-09 09:40:50 1128

1128

精度,無需犧牲直流精度來換取更高的采樣速率。然而,為實現高交流性能,如信噪比(SNR),系統設計人員必須考慮采樣時鐘信號或控制ADC中采樣保持(S&H)開關的轉換啟動信號上的抖動所帶來的誤差。隨著目標信號和采樣速率的增加,控制采樣保持開關的信號抖動會成為主要誤差源。

2023-06-15 16:30:12 381

381

本文主要介紹了時鐘偏差和時鐘抖動。

2023-07-04 14:38:28 960

960

電子發燒友網站提供《時鐘抖動對ADC性能有什么影響.pdf》資料免費下載

2023-11-28 10:24:10 1

1 抖動是相位抖動的主要原因之一。在通信系統中,時鐘扮演著非常重要的角色,它確定了信號的采樣時間和傳輸速率。然而,由于各種原因,包括晶體振蕩器的溫度變化、電力供應的不穩定、電磁干擾等,時鐘信號會產生偏移和抖動,導

2024-01-25 15:29:28 171

171

電子發燒友App

電子發燒友App

評論