在友晶LabCloud平臺(tái)上使用PipeCNN實(shí)現(xiàn)ImageNet圖像分類

利用深度卷積神經(jīng)網(wǎng)絡(luò)(CNN)進(jìn)行圖像分類是通過使用多個(gè)卷積層來從輸入數(shù)據(jù)中提取特征,最后通過分類層....

SDRAM控制器設(shè)計(jì)之signaltap調(diào)試

Signal Tap Logic Analyzer是Intel Quartus Prime設(shè)計(jì)軟件中....

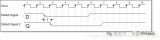

SDRAM控制器設(shè)計(jì)之按鍵的處理

邊沿檢測(cè)經(jīng)常用于按鍵輸入檢測(cè)電路中,按鍵按下時(shí)輸入信號(hào) key 變?yōu)榈碗娖剑存I抬起變?yōu)楦唠娖健.?dāng)輸....

友晶科技攜手中國地質(zhì)大學(xué)舉辦FPGA硬件在線實(shí)驗(yàn)云平臺(tái)公開課

近日,友晶科技攜手中國地質(zhì)大學(xué),成功舉辦了一場(chǎng)FPGA硬件在線實(shí)驗(yàn)云平臺(tái)公開課。

SDRAM控制器的設(shè)計(jì)——Sdram_Control.v代碼解析(異步FIFO讀寫模塊、讀寫SDRAM過程)

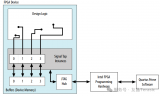

前言 SDRAM控制器里面包含5個(gè)主要的模塊,分別是PLL模塊,異步FIFO 寫模塊,異步FIFO讀....

SDRAM控制器設(shè)計(jì)之異步FIFO的調(diào)用

為了加深讀者對(duì) FPGA 端控制架構(gòu)的印象,在數(shù)據(jù)讀取的控制部分,首先我們可以將SDRAM 想作是一....

SDRAM控制器設(shè)計(jì)之command.v代碼解析

command.v文件對(duì)應(yīng)圖中SDRAM指令執(zhí)行模塊,它會(huì)從SDRAM接口控制模塊接收指令,然后產(chǎn)生....

SDRAM控制器設(shè)計(jì)之control_interface.v代碼解析

control_interface.v文件里已經(jīng)寫了非常詳盡的代碼備注。本文繼續(xù)對(duì)該文件代碼進(jìn)行講解....

解讀IS42R16320D的數(shù)據(jù)手冊(cè)

想用FPGA去控制一個(gè)器件,首先要學(xué)會(huì)閱讀器件的數(shù)據(jù)手冊(cè),去了解器件的功能和使用方法。下面就來梳理一....

基于互聯(lián)網(wǎng)的攝像測(cè)量系統(tǒng)(三)

使用HDMI線將三個(gè)HDMI顯示器分別連接到攝像節(jié)點(diǎn)A、B和終端節(jié)點(diǎn)DE10-Nano開發(fā)板上的HD....

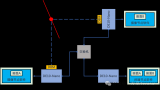

基于互聯(lián)網(wǎng)的攝像測(cè)量系統(tǒng)(二)

攝像節(jié)點(diǎn)由一個(gè)DE10-Nano開發(fā)板和一個(gè)D8M攝像頭實(shí)現(xiàn),DE10-Nano開發(fā)板的HDMI接口....

基于互聯(lián)網(wǎng)的攝像測(cè)量系統(tǒng)(一)

采用GPIO接口的D8M攝像頭,直接與DE10-Nano開發(fā)板連接,可通過FPGA進(jìn)行算法加速,CP....

如何將SD卡眾多文件打包成一個(gè).img文件方便一鍵燒寫呢?

相信不少SOC FPGA用戶在第一次設(shè)計(jì)SD卡image時(shí)都參考過Intel的經(jīng)典教程 Embedd....

街機(jī)彈球機(jī)的模擬設(shè)計(jì)實(shí)現(xiàn)

該項(xiàng)目是實(shí)現(xiàn)經(jīng)典的街機(jī)游戲——彈球機(jī)。使用DE1-SOC開發(fā)板上的滑動(dòng)開關(guān),玩家可以設(shè)置球的初始速度....

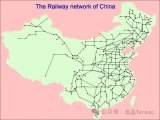

中國鐵路網(wǎng)的Dijkstra算法實(shí)現(xiàn)案例

該項(xiàng)目分別在DE1-SOC開發(fā)板的FPGA和HPS上實(shí)現(xiàn)了Dijkstra算法,能在中國鐵路網(wǎng)中找到....

用DE1-SOC進(jìn)行硬件加速的2D N-Body重力模擬器設(shè)計(jì)

該項(xiàng)目的目標(biāo)是創(chuàng)建一個(gè)用DE1-SOC進(jìn)行硬件加速的2D N-Body重力模擬器。

基于FPGA加速的bird-oid object算法實(shí)現(xiàn)

Bird-oid object 簡(jiǎn)稱Boids模型,是美國的一個(gè)圖形計(jì)算機(jī)科學(xué)家Craig Reyn....

基于FPGA加速的熱擴(kuò)散模擬器

這個(gè)項(xiàng)目的目標(biāo)是創(chuàng)建一個(gè)交互式的熱擴(kuò)散模擬器,它使用離散域上的熱方程,允許用戶在VGA屏幕上選擇熱源....

基于DE1-SOC的String Art實(shí)現(xiàn)

String Art起源于19世紀(jì)的數(shù)學(xué)家Mary Everest Boole的設(shè)計(jì),隨后發(fā)展成一種....

基于FPGA的貪吃蛇游戲設(shè)計(jì)

食物產(chǎn)生模塊完成的任務(wù)是:每次初始化就給定一個(gè)食物坐標(biāo)比如(24,10),然后蛇運(yùn)動(dòng)的過程中用蛇頭坐....