完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > SDRAM

SDRAM:Synchronous Dynamic Random Access Memory,同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器,同步是指內(nèi)存工作需要同步時(shí)鐘,內(nèi)部的命令的發(fā)送與數(shù)據(jù)的傳輸都以它為基準(zhǔn)

SDRAM:Synchronous Dynamic Random Access Memory,同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器,同步是指內(nèi)存工作需要同步時(shí)鐘,內(nèi)部的命令的發(fā)送與數(shù)據(jù)的傳輸都以它為基準(zhǔn);動(dòng)態(tài)是指存儲(chǔ)陣列需要不斷的刷新來(lái)保證數(shù)據(jù)不丟失;隨機(jī)是指數(shù)據(jù)不是線性依次存儲(chǔ),而是自由指定地址進(jìn)行數(shù)據(jù)讀寫(xiě)。

SDRAM:Synchronous Dynamic Random Access Memory,同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器,同步是指內(nèi)存工作需要同步時(shí)鐘,內(nèi)部的命令的發(fā)送與數(shù)據(jù)的傳輸都以它為基準(zhǔn);動(dòng)態(tài)是指存儲(chǔ)陣列需要不斷的刷新來(lái)保證數(shù)據(jù)不丟失;隨機(jī)是指數(shù)據(jù)不是線性依次存儲(chǔ),而是自由指定地址進(jìn)行數(shù)據(jù)讀寫(xiě)。

演變

SDRAM從發(fā)展到現(xiàn)在已經(jīng)經(jīng)歷了五代,分別是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM,第五代,DDR4 SDRAM。

第一代SDRAM采用單端(Single-Ended)時(shí)鐘信號(hào),第二代、第三代與第四代由于工作頻率比較快,所以采用可降低干擾的差分時(shí)鐘信號(hào)作為同步時(shí)鐘。

SDR SDRAM的時(shí)鐘頻率就是數(shù)據(jù)存儲(chǔ)的頻率,第一代內(nèi)存用時(shí)鐘頻率命名,如pc100,pc133則表明時(shí)鐘信號(hào)為100或133MHz,數(shù)據(jù)讀寫(xiě)速率也為100或133MHz。

之后的第二,三,四代DDR(Double Data Rate)內(nèi)存則采用數(shù)據(jù)讀寫(xiě)速率作為命名標(biāo)準(zhǔn),并且在前面加上表示其DDR代數(shù)的符號(hào),PC-即DDR,PC2=DDR2,PC3=DDR3。如PC2700是DDR333,其工作頻率是333/2=166MHz,2700表示帶寬為2.7G。

DDR的讀寫(xiě)頻率從DDR200到DDR400,DDR2從DDR2-400到DDR2-800,DDR3從DDR3-800到DDR3-1600。

很多人將SDRAM錯(cuò)誤的理解為第一代也就是 SDR SDRAM,并且作為名詞解釋,皆屬誤導(dǎo)。

SDR不等于SDRAM。

Pin:模組或芯片與外部電路連接用的金屬引腳,而模組的pin就是常說(shuō)的“金手指”。

SIMM:Single In-line Memory Module,單列內(nèi)存模組。內(nèi)存模組就是我們常說(shuō)的內(nèi)存條,所謂單列是指模組電路板與主板插槽的接口只有一列引腳(雖然兩側(cè)都有金手指)。

DIMM:Double In-line Memory Module,雙列內(nèi)存模組。是我們常見(jiàn)的模組類型,所謂雙列是指模組電路板與主板插槽的接口有兩列引腳,模組電路板兩側(cè)的金手指對(duì)應(yīng)一列引腳。

RIMM:registered DIMM,帶寄存器的雙線內(nèi)存模塊,這種內(nèi)存槽只能插DDR或Rambus內(nèi)存。

SO-DIMM:筆記本常用的內(nèi)存模組。

工作電壓:

SDRAM:3.3V

DDR:2.5V

DDR2:1.8V

DDR3:1.5V

DDR4:1.2V

SDRSDRAM內(nèi)存條的金手指通常是168線,而DDR SDRAM內(nèi)存條的金手指通常是184線的。

幾代產(chǎn)品金手指的缺口數(shù)及缺口位置也不同有效防止反插與錯(cuò)插,SDR SDRAM有兩個(gè)缺口,DDR只有一個(gè)缺口。

關(guān)系

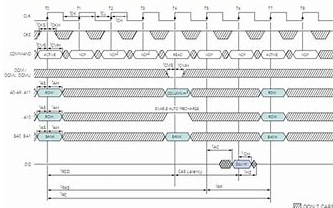

結(jié)構(gòu)、時(shí)序與性能的關(guān)系一、影響性能的主要時(shí)序參數(shù)所謂的影響性能是并不是指SDRAM的帶寬,頻率與位寬固定后,帶寬也就不可更改了。但這是理想的情況,在內(nèi)存的工作周期內(nèi),不可能總處于數(shù)據(jù)傳輸?shù)臓顟B(tài),因?yàn)橐忻睢ぶ返缺匾倪^(guò)程。但這些操作占用的時(shí)間越短,內(nèi)存工作的效率越高,性能也就越好。非數(shù)據(jù)傳輸時(shí)間的主要組成部分就是各種延遲與潛伏期。通過(guò)上文的講述,大家應(yīng)該很明顯看出有三個(gè)參數(shù)對(duì)內(nèi)存的性能影響至關(guān)重要,它們是tRCD、CL和tRP。每條正規(guī)的內(nèi)存模組都會(huì)在標(biāo)識(shí)上注明這三個(gè)參數(shù)值,可見(jiàn)它們對(duì)性能的敏感性。以內(nèi)存最主要的操作——讀取為例。tRCD決定了行尋址(有效)至列尋址(讀/寫(xiě)命令)之間的間隔,CL決定了列尋址到數(shù)據(jù)進(jìn)行真正被讀取所花費(fèi)的時(shí)間,tRP則決定了相同L-Bank中不同工作行轉(zhuǎn)換的速度。現(xiàn)在可以想象一下讀取時(shí)可能遇到的幾種情況(分析寫(xiě)入操作時(shí)不用考慮CL即可):1.要尋址的行與L-Bank是空閑的。也就是說(shuō)該L-Bank的所有行是關(guān)閉的,此時(shí)可直接發(fā)送行有效命令,數(shù)據(jù)讀取前的總耗時(shí)為tRCD+CL,這種情況我們稱之為頁(yè)命中(PH,Page Hit)。2.要尋址的行正好是前一個(gè)操作的工作行,也就是說(shuō)要尋址的行已經(jīng)處于選通有效狀態(tài),此時(shí)可直接發(fā)送列尋址命令,數(shù)據(jù)讀取前的總耗時(shí)僅為CL,這就是所謂的背靠背(Back to Back)尋址,我們稱之為頁(yè)快速命中(PFH,Page Fast Hit)或頁(yè)直接命中(PDH,Page Direct Hit)。3.要尋址的行所在的L-Bank中已經(jīng)有一個(gè)行處于活動(dòng)狀態(tài)(未關(guān)閉),這種現(xiàn)象就被稱作尋址沖突,此時(shí)就必須要進(jìn)行預(yù)充電來(lái)關(guān)閉工作行,再對(duì)新行發(fā)送行有效命令。結(jié)果,總耗時(shí)就是tRP+tRCD+CL,這種情況我們稱之為頁(yè)錯(cuò)失(PM,Page Miss)。顯然,PFH是最理想的尋址情況,PM則是最糟糕的尋址情況。上述三種情況發(fā)生的機(jī)率各自簡(jiǎn)稱為PHR——PH Rate、PFHR——PFH Rate、PMR——PM Rate。因此,系統(tǒng)設(shè)計(jì)人員(包括內(nèi)存與北橋芯片)都盡量想提高PHR與PFHR,同時(shí)減少PMR,以達(dá)到提高內(nèi)存工作效率的目的。二、增加PHR的方法顯然,這與預(yù)充電管理策略有著直接的關(guān)系,目前有兩種方法來(lái)盡量提高PHR。自動(dòng)預(yù)充電技術(shù)就是其中之一,它自動(dòng)的在每次行操作之后進(jìn)行預(yù)充電,從而減少了日后對(duì)同一L-Bank不同行尋址時(shí)發(fā)生沖突的可能性。但是,如果要在當(dāng)前行工作完成后馬上打開(kāi)同一L-Bank的另一行工作時(shí),仍然存在tRP的延遲。怎么辦? 此時(shí)就需要L-Bank交錯(cuò)預(yù)充電了。VIA的4路交錯(cuò)式內(nèi)存控制就是在一個(gè)L-Bank工作時(shí),對(duì)下一個(gè)要工作的L-Bank進(jìn)行預(yù)充電。這樣,預(yù)充電與數(shù)據(jù)的傳輸交錯(cuò)執(zhí)行,當(dāng)訪問(wèn)下一個(gè)L-Bank時(shí),tRP已過(guò),就可以直接進(jìn)入行有效狀態(tài)了。目前VIA聲稱可以跨P-Bank進(jìn)行16路內(nèi)存交錯(cuò),并以LRU算法進(jìn)行預(yù)充電管理。有關(guān)L-Bank交錯(cuò)預(yù)充電(存取)的具體執(zhí)行在本刊2001年第2期已有詳細(xì)介紹,這里就不再重復(fù)了。L-Bank交錯(cuò)自動(dòng)預(yù)充電/讀取時(shí)序圖(可點(diǎn)擊放大):L-Bank 0與L-Bank 3實(shí)現(xiàn)了無(wú)間隔交錯(cuò)讀取,避免了tRP對(duì)性能的影響。三、增加PFHR的方法無(wú)論是自動(dòng)預(yù)充電還是交錯(cuò)工作的方法都無(wú)法消除tRCD所帶來(lái)的延遲。要解決這個(gè)問(wèn)題,就要盡量讓一個(gè)工作行在進(jìn)行預(yù)充電前盡可能多的接收多個(gè)工作命令,以達(dá)到背靠背的效果,此時(shí)就只剩下CL所造成的讀取延遲了(寫(xiě)入時(shí)沒(méi)有延遲)。如何做到這一點(diǎn)呢?這就是北橋芯片的責(zé)任了。在上文的時(shí)序圖中有一個(gè)參數(shù)tRAS(Active to Precharge Command,行有效至預(yù)充電命令間隔周期)。它有一個(gè)范圍,對(duì)于PC133標(biāo)準(zhǔn),一般是預(yù)充電命令至少要在行有效命令5個(gè)時(shí)鐘周期之后發(fā)出,最長(zhǎng)間隔視芯片而異(基本在120000ns左右),否則工作行的數(shù)據(jù)將有丟失的危險(xiǎn)。那么這也就意味著一個(gè)工作行從有效(選通)開(kāi)始,可以有120000ns的持續(xù)工作時(shí)間而不用進(jìn)行預(yù)充電。顯然,只要北橋芯片不發(fā)出預(yù)充電(包括允許自動(dòng)預(yù)充電)的命令,行打開(kāi)的狀態(tài)就會(huì)一直保持。在此期間的對(duì)該行的任何讀寫(xiě)操作也就不會(huì)有tRCD的延遲。可見(jiàn),如果北橋芯片在能同時(shí)打開(kāi)的行(頁(yè))越多,那么PFHR也就越大。需要強(qiáng)調(diào)的是,這里的同時(shí)打開(kāi)不是指對(duì)多行同時(shí)尋址(那是不可能的),而是指多行同時(shí)處于選通狀態(tài)。我們可以看到一些SDRAM芯片組的資料中會(huì)指出可以同時(shí)打開(kāi)多少個(gè)頁(yè)的指標(biāo),這可以說(shuō)是決定其內(nèi)存性能的一個(gè)重要因素。Intel 845芯片組MCH的資料:其中表明它可以支持24個(gè)頁(yè)面同時(shí)處于打開(kāi)狀態(tài)但是,可同時(shí)打開(kāi)的頁(yè)數(shù)也是有限制的。從SDRAM的尋址原理講,同一L-Bank中不可能有兩個(gè)打開(kāi)的行(S-AMP只能為一行服務(wù)),這就限制了可同時(shí)打開(kāi)的頁(yè)面總數(shù)。以SDRAM有4個(gè)L-Bank,北橋最多支持8個(gè)P-Bank為例,理論上最多只能有32個(gè)頁(yè)面能同時(shí)處于打開(kāi)的狀態(tài)。而如果只有一個(gè)P-Bank,那么就只剩下4個(gè)頁(yè)面,因?yàn)橛袔讉€(gè)L-Bank才能有同時(shí)打開(kāi)幾個(gè)行而互不干擾。Intel 845的MHC雖然可以支持24個(gè)打開(kāi)的頁(yè)面,那也是指6個(gè)P-Bank的情況下(845MCH只支持6個(gè)P-Bank)。可見(jiàn)845已經(jīng)將同時(shí)打開(kāi)頁(yè)數(shù)發(fā)揮到了極致。不過(guò),同時(shí)打開(kāi)頁(yè)數(shù)多了,也對(duì)存取策略提出了一定的要求。理論上,要盡量多地使用已打開(kāi)的頁(yè)來(lái)保證最短的延遲周期,只有在數(shù)據(jù)不存在(讀取時(shí))或頁(yè)存滿了(寫(xiě)入時(shí))再考慮打開(kāi)新的指定頁(yè),這也就是變向的連續(xù)讀/寫(xiě)。而打開(kāi)新頁(yè)時(shí)就必須要關(guān)閉一個(gè)打開(kāi)的頁(yè),如果此時(shí)打開(kāi)的頁(yè)面已是北橋所支持的最大值但還不到理論極限的話,就需要一個(gè)替換策略,一般都是用LRU算法來(lái)進(jìn)行,這與VIA的交錯(cuò)控制大同小異。

SDRAM基礎(chǔ)知識(shí)

在學(xué)習(xí)SDRAM之前,必須先了解“SDRAM”這個(gè)概念性的東西,并有感性的認(rèn)識(shí)轉(zhuǎn)變到一種理性的認(rèn)識(shí),所謂理性的認(rèn)識(shí)就是實(shí)質(zhì)性的東西……。不多說(shuō),相信你已經(jīng)迫不急待了。那我們就開(kāi)始了。

初識(shí)SDRAM

SDRAM的全稱是:Synchronous Dynamic Random Access Memory,同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器,同步是指 Memory工作需要同步時(shí)鐘,內(nèi)部的命令的發(fā)送與數(shù)據(jù)的傳輸都以它為基準(zhǔn);動(dòng)態(tài)是指存儲(chǔ)陣列需要不斷的刷新來(lái)保證數(shù)據(jù)不丟失;隨機(jī)是指數(shù)據(jù)不是線性依次存儲(chǔ),而是自由指定地址進(jìn)行數(shù)據(jù)讀寫(xiě)。

相信通過(guò)這段話,你已經(jīng)知道什么是SDRAM了,這里面有幾個(gè)概念性的東西需要我們好好了解:同步、動(dòng)態(tài)、隨機(jī)。

同步:這個(gè)詞在FPGA設(shè)計(jì)之中我們經(jīng)常會(huì)遇到它,它反映了驅(qū)動(dòng)sdram必須遵守一種時(shí)序原則,就是數(shù)據(jù)/命令和時(shí)鐘在時(shí)間上同時(shí)的概念,也是在驅(qū)動(dòng)sdram時(shí)要十分注意的一點(diǎn)。

動(dòng)態(tài):RAM這中存儲(chǔ)結(jié)構(gòu)會(huì)掉電丟失,在上電的時(shí)候也會(huì)丟失。為什么?因?yàn)镾DRAM內(nèi)部存儲(chǔ)的數(shù)據(jù)是二進(jìn)制數(shù)據(jù),非0則1。用來(lái)存儲(chǔ)該二進(jìn)制數(shù)據(jù)的電路是由電容構(gòu)成的,由于電容這種器件會(huì)隨著時(shí)間而慢慢放電,就像人的記憶一樣,有些記憶會(huì)隨著時(shí)間的流逝而淡忘了。很簡(jiǎn)單,如果你不想讓某些事某些人淡忘,怎么辦?就只有時(shí)不時(shí)地去回憶。那SDRAM不想“忘”了它的數(shù)據(jù),怎么辦,一樣,也只有不斷地回憶,就是不斷地去刷新里面的存儲(chǔ)電路。

隨機(jī):隨機(jī)就是不指定為一次連續(xù),也就是可以對(duì)SDRAM里面的隨意地址進(jìn)行讀寫(xiě)操作。

SDRAM的歷史

SDRAM從發(fā)展到現(xiàn)在已經(jīng)經(jīng)歷了四代,分別是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM.

第一代SDRAM采用單端(Single-Ended)時(shí)鐘信號(hào),第二代、第三代與第四代由于工作頻率比較快,所以采用可降低干擾的差分時(shí)鐘信號(hào)作為同步時(shí)鐘。

SDR SDRAM的時(shí)鐘頻率就是數(shù)據(jù)存儲(chǔ)的頻率,第一代內(nèi)存用時(shí)鐘頻率命名,如pc100,pc133則表明時(shí)鐘信號(hào)為100或133MHz,數(shù)據(jù)讀寫(xiě)速率也為100或133MHz。

之后的第二,三,四代DDR(Double Data Rate)內(nèi)存則采用數(shù)據(jù)讀寫(xiě)速率作為命名標(biāo)準(zhǔn),并且在前面加上表示其DDR代數(shù)的符號(hào),PC-即DDR,PC2=DDR2,PC3=DDR3。如PC2700是DDR333,其工作頻率是333/2=166MHz,2700表示帶寬為2.7G。

DDR的讀寫(xiě)頻率從DDR200到DDR400,DDR2從DDR2-400到DDR2-800,DDR3從DDR3-800到DDR3-1600。

實(shí)驗(yàn)中要操作的SDRAM就是第一代SDRAM,雖然SDRAM經(jīng)歷了這么多次的更新?lián)Q代,但其內(nèi)部的架構(gòu)還是相差無(wú)幾,更多的是在速率和存儲(chǔ)數(shù)量上的不同。

實(shí)驗(yàn)的SDRAM介紹

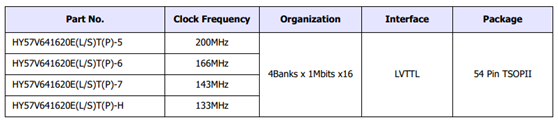

通過(guò)上面的兩節(jié),相信你已經(jīng)對(duì)SDRAM已經(jīng)有了大致的了解。現(xiàn)在就以實(shí)驗(yàn)中用到的SDRAM--HY57V641620ET-H(海力士的SDRAM)為一個(gè)例子對(duì)SDRAM的內(nèi)部結(jié)果進(jìn)行一個(gè)詳細(xì)的介紹

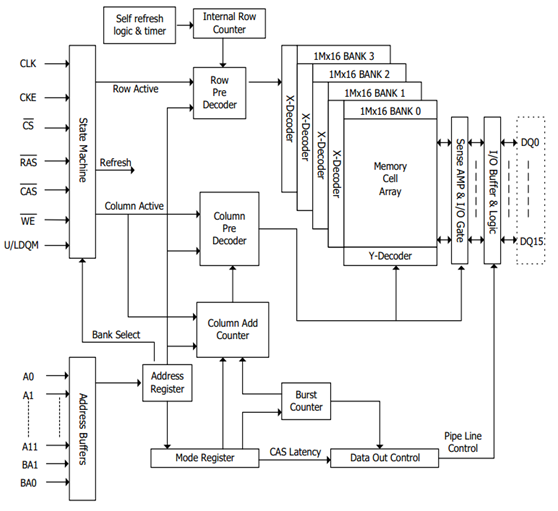

HY57V641620ET-H的內(nèi)部結(jié)構(gòu)

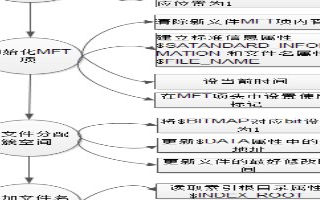

通過(guò)上圖可以看到SDRAM的“五臟六腑”,下面就來(lái)一一剖析:

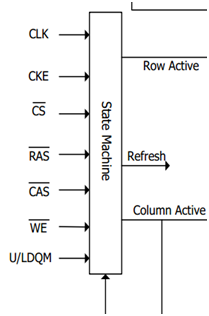

SDRAM指令接口模塊,這些信號(hào)組成了SDRAM的控制指令,控制指令通過(guò)“state machine”進(jìn)行譯碼,由此產(chǎn)生了一系列的控制動(dòng)作。

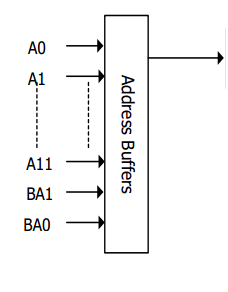

SDRAM地址線,其中包括塊地址線、行地址線、列地址線,至于會(huì)有這么多線,是因?yàn)橛玫搅丝偩€復(fù)用,其行線和列線分時(shí)復(fù)用,從而節(jié)省了總線資源,又可以操作到SDRAM的全部存儲(chǔ)單元。至于塊地址線,下面會(huì)講到。

SDRAM存儲(chǔ)塊和數(shù)據(jù)接口:HY57V641620ET-H內(nèi)部存儲(chǔ)由四個(gè)一模一樣的存儲(chǔ)塊組成,至于怎么識(shí)別這四個(gè)存儲(chǔ)塊,必須要有兩條地址線,所以就用到了上面的那兩條地址線。

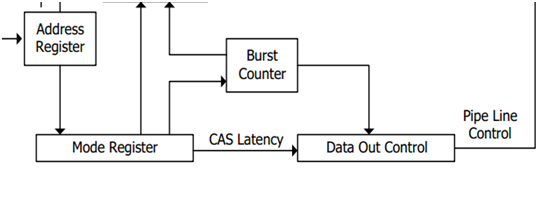

動(dòng)作電路模塊:這幾個(gè)模塊主要是根據(jù)“state machine”的譯碼結(jié)果進(jìn)行工作的、包括行列地址的編碼、自刷新定時(shí)和自刷新操作。

模式寄存器解碼和突發(fā)操作模塊:在對(duì)SDRAM的寄存器進(jìn)行配置的時(shí)候,是通過(guò)地址線對(duì)SDRAM進(jìn)行配置的,SDRAM中有一種突發(fā)操作模式,該模式由寄存器進(jìn)行配置,所以該電路中包含一個(gè)突發(fā)操作的計(jì)數(shù)器。至于突發(fā)操作的原理下面會(huì)涉及到。

相信看到這里,你已經(jīng)對(duì)SDRAM由感性的認(rèn)識(shí)升級(jí)到實(shí)質(zhì)性的認(rèn)識(shí),恭喜你,哈哈…。

HY57V641620ET-H的存儲(chǔ)量

看到這之前相信你應(yīng)該了解過(guò)不少SDRAM的資料,也相信很多資料中從未講過(guò)SDRAM名稱的問(wèn)題,現(xiàn)在我就來(lái)幫你解析這個(gè)SDRAM

HY:代表是海力士的SDRAM存儲(chǔ)器

57:代表這是SDRAM芯片

V:代表這個(gè)SDRAM芯片工作電壓是3.3V

641620:代表這個(gè)SDRAM芯片的存儲(chǔ)容量

ET:代表SDRAM的塊反應(yīng)時(shí)間和封裝

H:代表SDRAM的速度等級(jí)

下面我們來(lái)計(jì)算下這個(gè)芯片的存儲(chǔ)容量:

存儲(chǔ)容量由存儲(chǔ)深度和存儲(chǔ)寬度決定,這是任何存儲(chǔ)芯片存儲(chǔ)容量的定義;

存儲(chǔ)深度:HY57V641620ET-H內(nèi)部有4個(gè)塊,每個(gè)塊有行地址12bit,列地址8bit

所以每個(gè)塊就有2^12*2^8 = 4096*256=1048576個(gè)存儲(chǔ)單元,4個(gè)塊就有4*1048576=4194304個(gè)存儲(chǔ)單元。

存儲(chǔ)寬度:該SDRAM的數(shù)據(jù)位寬為16bit

存儲(chǔ)容量:4194304*16bit = 67108864bit,就是64M

DRAM (動(dòng)態(tài)隨機(jī)訪問(wèn)存儲(chǔ)器)對(duì)設(shè)計(jì)人員特別具有吸引力,因?yàn)樗峁┝藦V泛的性能,用于各種計(jì)算機(jī)和嵌入式系統(tǒng)的存儲(chǔ)系統(tǒng)設(shè)計(jì)中。本文概括闡述了DRAM ...

本文主要介紹的是ARM里的RAM和SDRAM有什么區(qū)別,首先介紹了RAM的類別及特點(diǎn),其次對(duì)SDRAM做了詳細(xì)闡述,最后介紹了RAM和SDRAM的區(qū)別是什么。

DDR4技術(shù)有什么特點(diǎn)?如何采用ANSYS進(jìn)行DDR4仿真?

本文介紹了DDR4技術(shù)的特點(diǎn),并簡(jiǎn)單介紹了ANSYS工具用來(lái)仿真DDR4的過(guò)程。文章中主要介紹的對(duì)象為DDR4 3200MHz內(nèi)存,因?yàn)橛布O客對(duì)DDR...

什么是 DDR5?SDRAM 技術(shù)發(fā)展歷程

英特爾和 AMD 的核戰(zhàn)爭(zhēng)越演愈烈,現(xiàn)在的臺(tái)式機(jī)開(kāi)始 6 核起跳,可以預(yù)見(jiàn),馬上內(nèi)存的性能又將成為新的瓶頸。

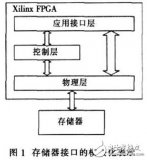

基于Xilinx FPGA實(shí)現(xiàn)的DDR SDRAM控制器工作過(guò)程詳解

在高速信號(hào)處理系統(tǒng)中, 需要緩存高速、大量的數(shù)據(jù), 存儲(chǔ)器的選擇與應(yīng)用已成為系統(tǒng)實(shí)現(xiàn)的關(guān)鍵所在。DDR SDRAM是一種高速CMOS、動(dòng)態(tài)隨機(jī)訪問(wèn)存儲(chǔ)...

RAM包括SRAM和DRAM,前者是靜態(tài)隨機(jī)存儲(chǔ)器,主要是依靠觸發(fā)器存儲(chǔ)數(shù)據(jù),無(wú)需刷新,而后者是動(dòng)態(tài)隨機(jī)存儲(chǔ)器,依靠MOSFET中柵電容存儲(chǔ)數(shù)據(jù),需不斷...

如何操作SDRAM的自刷新命令而不影響正常讀寫(xiě)操作?

問(wèn):如何操作SDRAM的自刷新命令而不影響正常讀寫(xiě)操作? 眾所周知,SDRAM從開(kāi)始工作伊始,一直伴隨著64ms刷新一遍的最基本規(guī)定(假設(shè)該SDRAM有...

2018-06-20 標(biāo)簽:SDRAM 1.1萬(wàn) 0

RAM RAM是指通過(guò)指令可以隨機(jī)的、個(gè)別的對(duì)各個(gè)存儲(chǔ)單元進(jìn)行訪問(wèn)的存儲(chǔ)器,一般訪問(wèn)時(shí)間基本固定,而與存儲(chǔ)單元地址無(wú)關(guān)。RAM的速度比較快,但其保存的信...

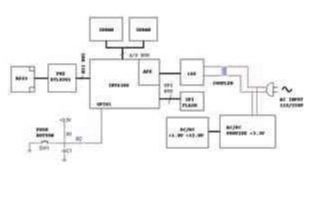

基于INT6300芯片實(shí)現(xiàn)HomePlug AV電力線調(diào)制解調(diào)器的設(shè)計(jì)

從硬件框圖我們可以看出,此方案是一個(gè)單芯片的方案。INT6300為INTELLON公司生產(chǎn)的內(nèi)核為ARM926EJ-S 32位RISC處理器。系統(tǒng)的軟件...

2020-01-08 標(biāo)簽:芯片sdram調(diào)制解調(diào)器 1.0萬(wàn) 0

0

2

大拇指FPGA開(kāi)發(fā)板(Anlogic EG4S20BG256版本)相關(guān)資料介紹

標(biāo)簽:SDRAMUSB接口FPGA開(kāi)發(fā)板 62622 0

12

2

stm32F103+CPLD+SDRAM驅(qū)動(dòng)OV5640自動(dòng)對(duì)焦500w像素拍攝模塊,任何單片機(jī)都能拍超清大圖

標(biāo)簽:SDRAM 16157 12

鎂光MT48LC16M16A2P-6AIT 256M SDRAM立即下載

類別:芯片說(shuō)明書(shū) 2015-12-22 標(biāo)簽:SDRAMMT48LC64M4A2

DDR2_DDR3_SDRAM的PCB布線規(guī)則指導(dǎo)立即下載

類別:嵌入式開(kāi)發(fā) 2012-05-06 標(biāo)簽:SDRAM

H5TQ4G43AFR和H5TQ4G83AFR及H5TQ4G63AFR DDR3 SDRAM的數(shù)據(jù)手冊(cè)立即下載

類別:IC datasheet pdf 2020-12-09 標(biāo)簽:CMOSSDRAMDDR3

動(dòng)態(tài)隨即存儲(chǔ)器HY57V641620基本知識(shí)立即下載

類別:電子教材 2016-07-13 標(biāo)簽:SDRAM存儲(chǔ)器HY57V641620

DDR2 SDRAM的K4T1G164QE和K4T1G084QE及K4T1G164QE數(shù)據(jù)手冊(cè)免費(fèi)下載立即下載

類別:IC中文資料 2018-11-01 標(biāo)簽:驅(qū)動(dòng)器SDRAMDDR2

DDR3 SDRAM的JESD79-3D標(biāo)準(zhǔn)免費(fèi)下載立即下載

類別:規(guī)則標(biāo)準(zhǔn) 2019-11-04 標(biāo)簽:SDRAMDDR3寄存器

DDR2_DDR3_SDRAM,PCB布線規(guī)則指導(dǎo)立即下載

類別:嵌入式開(kāi)發(fā) 2017-10-31 標(biāo)簽:PCBSDRAM

DRAM,動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器,需要不斷的刷新,才能保存數(shù)據(jù)。而且是行列地址復(fù)用的,許多都有頁(yè)模式。 SRAM,靜態(tài)的隨機(jī)存取存儲(chǔ)器,加電情況下,不需要刷...

DDR3的工作原理及DDR3 SDRAM控制器設(shè)計(jì)與結(jié)果分析

DDR3 SDRAM 是第二代雙倍數(shù)據(jù)傳輸速率同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器, 以其大容量、 高速率和良好的兼容性得到了廣泛應(yīng)用。 文中介紹了 DDR3 的特點(diǎn)和操...

SDRAM,DDR3,DDR2,DDR4,DDR1的區(qū)別對(duì)比及其特點(diǎn)分析

DDR3 SDRAM(Double Data Rate Three SDRAM):為雙信道三次同步動(dòng)態(tài)隨機(jī)存取內(nèi)存。 DDR4 SDRAM(Doubl...

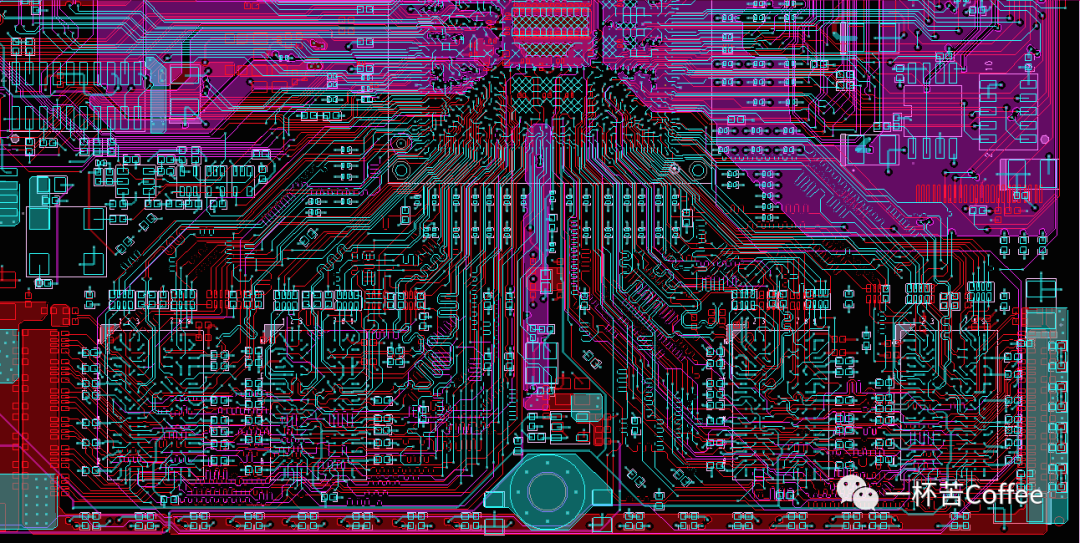

硬件電路設(shè)計(jì)之DDR電路設(shè)計(jì)(2)

本文主要講述一下DDR從0到1設(shè)計(jì)的整個(gè)設(shè)計(jì)的全過(guò)程。

2023-11-27 標(biāo)簽:SDRAM存儲(chǔ)器電路設(shè)計(jì) 1.3萬(wàn) 0

SDRAM從SDR到DDR再到DDR2一路走來(lái),又都產(chǎn)生了什么樣的變化,又都在哪些方面進(jìn)行了改進(jìn),帶來(lái)了速度性能的進(jìn)一步提升呢?

DIMM SDRAM 168線內(nèi)存條引腳定義 正面,左方: Pin

零基礎(chǔ)學(xué)FPGA - SDRAM(理論篇)

一、從結(jié)構(gòu)說(shuō)起: 1、P-bank SDRAM,也即我們的內(nèi)存,我們的電腦,手機(jī)等設(shè)備都離不開(kāi)我們的內(nèi)存。一個(gè)設(shè)備運(yùn)行速度的快慢,內(nèi)存起到關(guān)鍵性的作用,...

推薦一款比較適合做GUI的國(guó)產(chǎn)MCU!

前兩天收到了華芯微特提供的一塊開(kāi)發(fā)板,今天抽時(shí)間測(cè)試了一下,感覺(jué)效果還不錯(cuò),分享給大家。 之前做了一個(gè)7寸觸摸屏控制器的項(xiàng)目,用的STM32F429IG...

固態(tài)硬盤(pán)由于必須使用FTL做邏輯地址和物理地址之間的轉(zhuǎn)換,如果在SSD讀、寫(xiě)、刪除等正常工作的情況下出現(xiàn)異常掉電,有可能會(huì)導(dǎo)致mapping table...

2021-03-31 標(biāo)簽:SDRAMSSD固態(tài)硬盤(pán) 5865 0

SRAM是靠雙穩(wěn)態(tài)觸發(fā)器來(lái)記憶信息的;SDRAM是靠MOS電路中的柵極電容來(lái)記憶信息的。由于電容上的電荷會(huì)泄漏,需要定時(shí)給與補(bǔ)充,所以動(dòng)態(tài)RAM需要設(shè)置...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無(wú)刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺(jué) | 無(wú)人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹(shù)莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |