概述

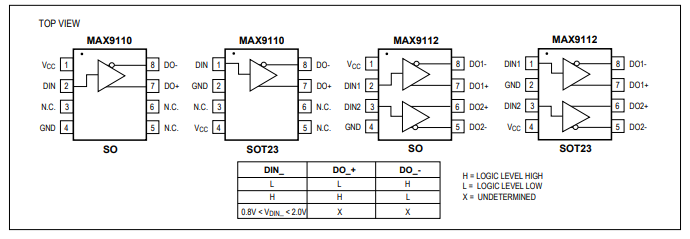

MAX9171/MAX9172單/雙路低壓差分信號(LVDS)接收器設計用于那些要求高數據速率、低功耗、小尺寸和低噪聲的應用。兩種器件都支持超過500Mbps的轉換速率,工作于3.3V單電源。

MAX9171是單路LVDS接收器,而MAX9172是雙路LVDS接收器。兩種器件都符合ANSI TIA/EIA-644 LVDS標準,將LVDS信號轉換為LVTTL/LVCMOS兼容的輸出。當輸入處于無驅動的開路、終端匹配或短路時,安全失效特性設置輸出為高電平。MAX9171/MAX9172有8引腳SO封裝和節省空間的薄型DFN和SOT23封裝。

數據表:*附件:MAX9171 MAX9172單 雙路LVDS線接收器,帶有通道失效保護技術手冊.pdf

特性

- 輸入接收LVDS和LVPECL信號

- 通道內安全失效電路

- 省空間的8引腳TDFN和SOT23封裝

- 在輸入處于無驅動的開路、短路或終端匹配時,安全失效電路設置輸出為高電平

- 流通引腳排列簡化了PCB設計

- 保證500Mbps數據速率

- DS90LV018A和DS90LV028A (僅SO封裝)的代用產品

- 符合ANSI TIA/EIA-644標準

- 3.3V電源電壓

- -40°C至+85°C工作溫度范圍

- 低功耗

應用

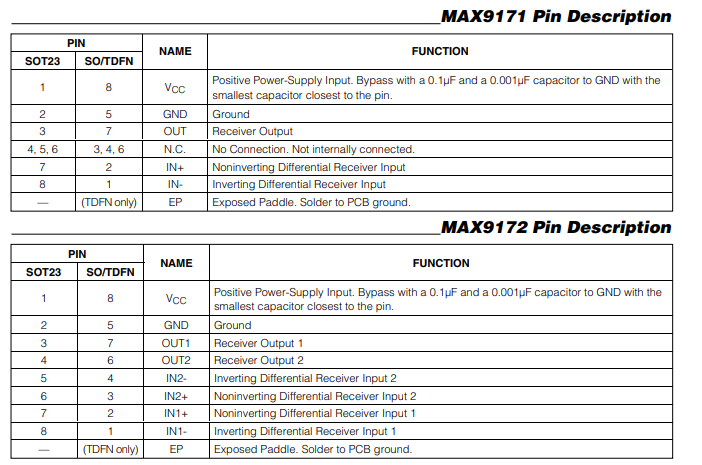

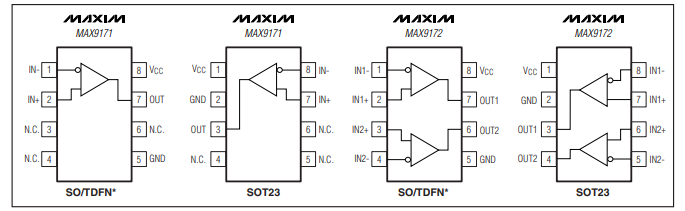

引腳配置描述

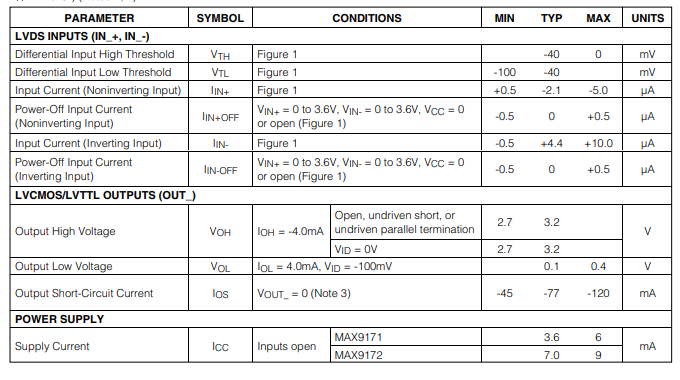

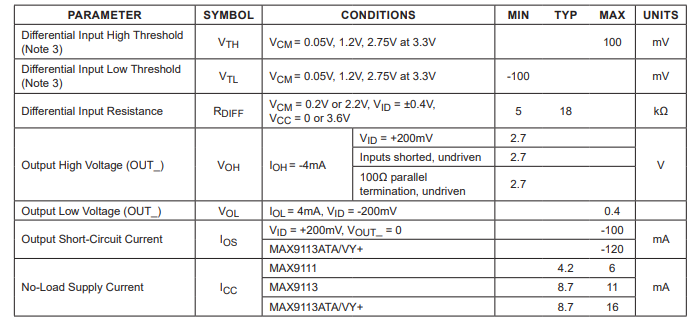

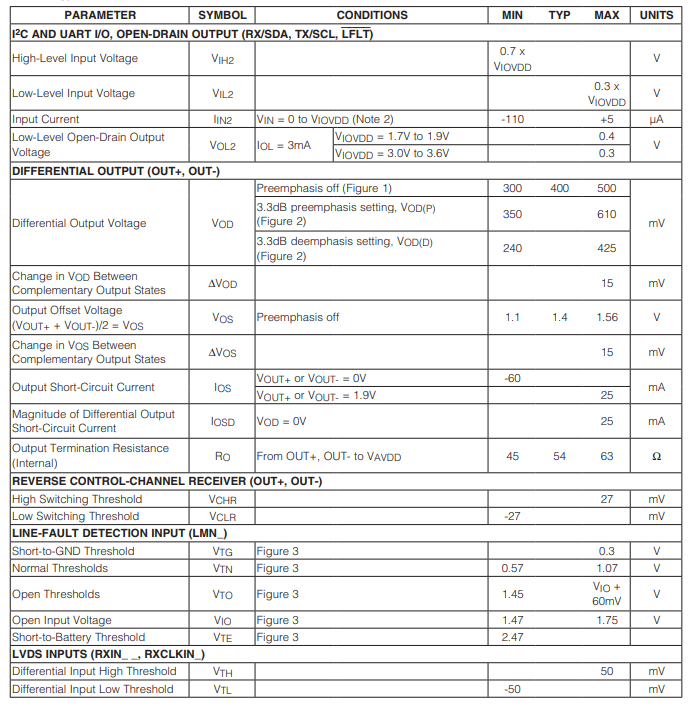

電特性

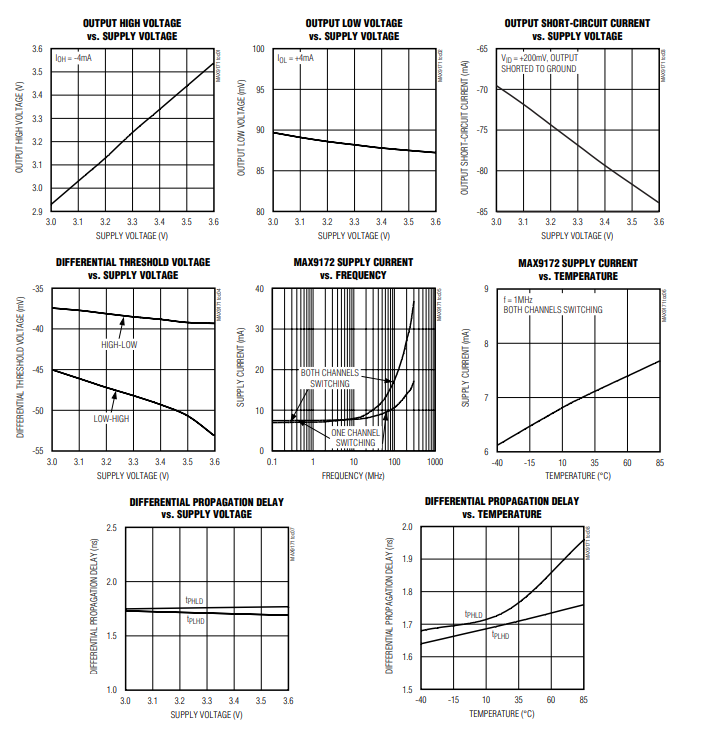

典型操作特性

靜電放電(ESD)保護

所有引腳均集成了ESD保護結構,以防范在處理和組裝過程中遇到的靜電放電。MAX9171/MAX9172的接收器輸入引腳具有額外的保護,可承受 ±13kV 的靜電放電而不損壞。這些結構在正常工作以及器件斷電時均可抵御ESD。

這些器件的接收器輸入按照人體模型(Human Body Model)進行了 ±13kV 保護特性測試。

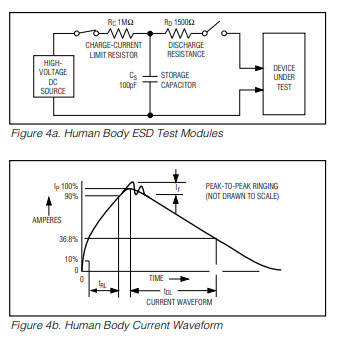

人體模型

圖4a展示了人體模型,圖4b展示了其放電時產生的電流波形。該模型由一個100pF的電容組成,充電至ESD測試電壓后,通過一個1.5kΩ的電阻向被測器件放電。

應用信息

電源去耦

使用0.1μF和0.001μF的高頻表面貼裝陶瓷電容對Vcc進行去耦,盡可能將較小值的0.001μF電容靠近器件安裝。為實現額外的電源去耦,在電源進入電路的位置放置一個10μF的鉭電容或陶瓷電容。

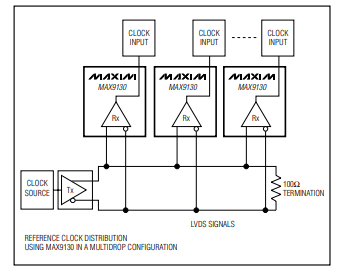

差分走線

輸入走線特性會影響MAX9171/MAX9172的性能。使用受控阻抗的PCB走線來匹配電纜特性阻抗,以消除反射并確保噪聲以共模方式耦合。將差分走線緊密排布在一起。通過匹配走線的電氣長度來減少偏移。

每個通道的差分信號應彼此靠近布線,以抵消外部磁場。在差分走線之間保持恒定距離,以避免差分阻抗出現不連續性。避免90°轉彎,并盡量減少過孔數量,以進一步防止阻抗不連續性。

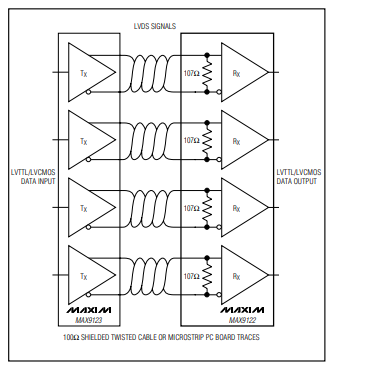

電纜和連接器

傳輸介質通常具有約100Ω的受控差分阻抗。使用具有匹配差分阻抗的電纜和連接器,以最大限度地減少阻抗不連續性。平衡電纜往往會拾取共模噪聲,而LVDS接收器會拒絕共模噪聲。

端接

MAX9171/MAX9172需要一個外部端接電阻。端接電阻應與傳輸線的差分阻抗匹配。端接電阻值在90Ω至132Ω之間,具體取決于傳輸介質的特性阻抗。

使用MAX9171/MAX9172時,盡量縮短輸入端接電阻與MAX9171/MAX9172接收器輸入之間的距離。使用單個精度為1%的表面貼裝電阻。

電路板布局

對于LVDS應用,建議使用四層PCB,分別用于電源、接地、LVDS輸入信號和輸出信號。將輸入LVDS信號與輸出信號分開,以防止串擾。將TDFN封裝上的裸露焊盤通過大量過孔連接到PCB接地層。連接裸露焊盤不能替代連接接地引腳。始終將TDFN封裝上的引腳5連接到地。

-

接收器

+關注

關注

15文章

2568瀏覽量

73803 -

lvds

+關注

關注

2文章

1126瀏覽量

67401

發布評論請先 登錄

MAX3280E/MAX3281E/MAX3283E/MAX3284E 真失效保護接收器

MAX13080E ESD保護的RS-485/RS-422收發器

MAX9172ESA+ 接口 - 驅動器,接收器,收發器

MAX9171EKA+T 接口 - 驅動器,接收器,收發器

MAX9172EKA+T 接口 - 驅動器,接收器,收發器

MAX202 具有±15kV ESD 保護功能的 5V 雙路 RS-232 線路驅動器和接收器數據表

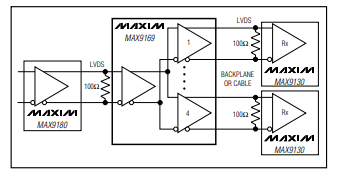

MAX9169/MAX9170 4端口LVDS和LVTTL至LVDS轉發器技術手冊

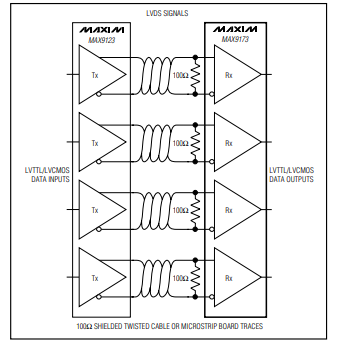

MAX9173四路LVDS線接收器,引腳按信號流向排列,帶有通道失效保護技術手冊

MAX9121/MAX9122四路LVDS線接收器,內部端接,引腳按信號流向排列技術手冊

MAX9171/MAX9172單/雙路LVDS線接收器,帶有通道失效保護技術手冊

MAX9171/MAX9172單/雙路LVDS線接收器,帶有通道失效保護技術手冊

評論