先進(jìn)IC封裝是超越摩爾時(shí)代的一大技術(shù)亮點(diǎn)。當(dāng)芯片在每個(gè)工藝節(jié)點(diǎn)上的縮小越來越困難、也越來越昂貴之際,工程師們將多個(gè)芯片放入先進(jìn)的封裝中,就不必再費(fèi)力縮小芯片了。 然而,先進(jìn)IC封裝技術(shù)發(fā)展十分迅速

2020-11-19 16:00:58 5863

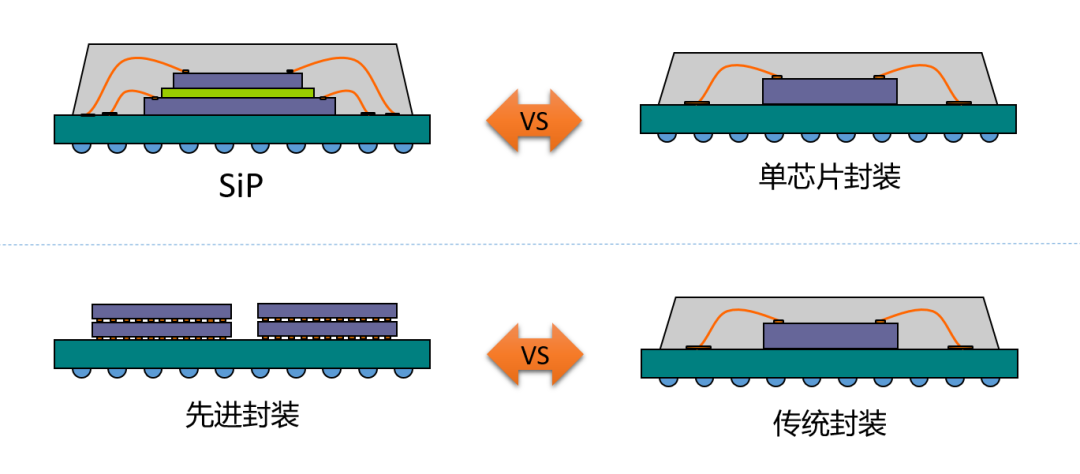

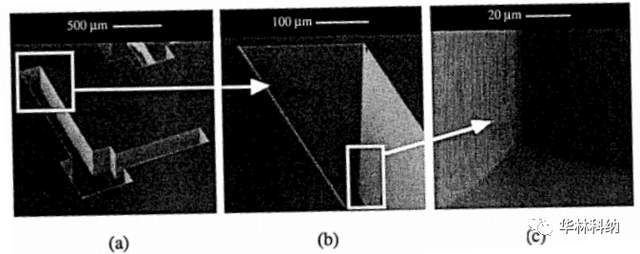

5863 SiP的關(guān)注點(diǎn)在于:系統(tǒng)在封裝內(nèi)的實(shí)現(xiàn),所以系統(tǒng)是其重點(diǎn)關(guān)注的對(duì)象,和SiP系統(tǒng)級(jí)封裝對(duì)應(yīng)的為單芯片封裝;先進(jìn)封裝的關(guān)注點(diǎn)在于:封裝技術(shù)和工藝的先進(jìn)性,所以先進(jìn)性的是其重點(diǎn)關(guān)注的對(duì)象,和先進(jìn)封裝對(duì)應(yīng)的是傳統(tǒng)封裝。

2021-03-15 10:31:53 8490

8490

芯片升級(jí)的兩個(gè)永恒主題:性能、體積/面積。芯片技術(shù)的發(fā)展,推動(dòng)著芯片朝著高性能和輕薄化兩個(gè)方向提升。而先進(jìn)制程和先進(jìn)封裝的進(jìn)步,均能夠使得芯片向著高性能和輕薄化前進(jìn)。

2023-02-14 10:43:02 1538

1538

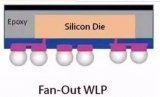

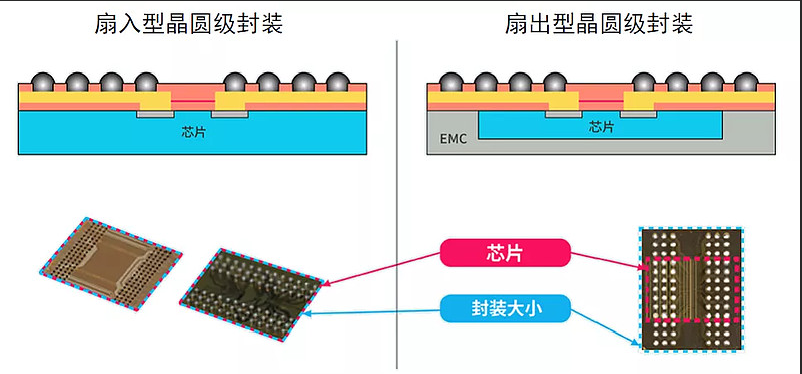

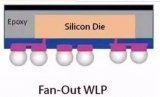

進(jìn)人芯片的線路更短,也具有更好的電性能。圓片級(jí)封裝可以通過采用比傳統(tǒng)封裝更細(xì)的線路實(shí)現(xiàn)高密度的封裝再布線,因此能夠在實(shí)現(xiàn)封裝小型化的同時(shí),提供更高的帶寬,從而更加適應(yīng)先進(jìn)技術(shù)節(jié)點(diǎn)芯片的封裝。

2023-05-08 10:33:17 1071

1071

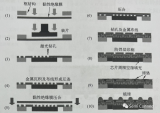

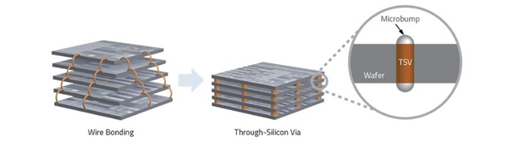

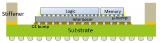

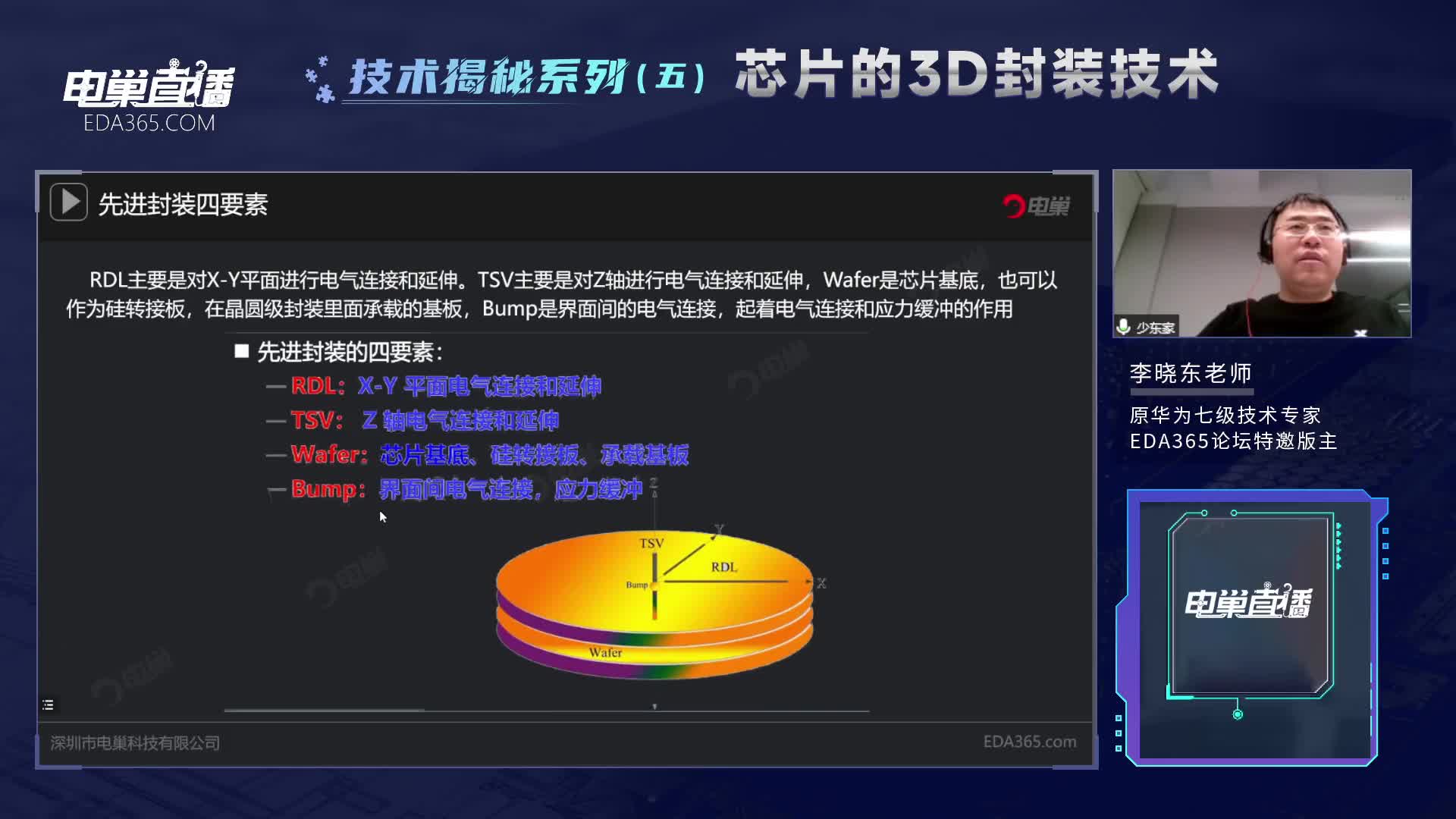

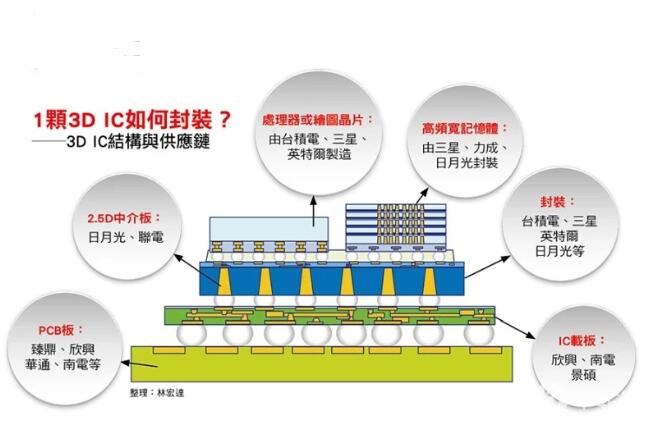

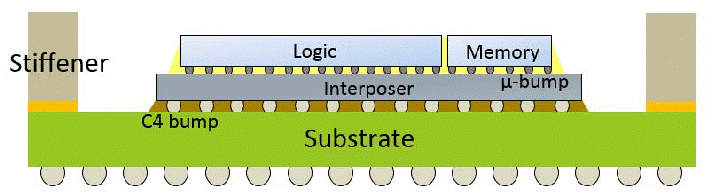

硅通孔(TSV) 是當(dāng)前技術(shù)先進(jìn)性最高的封裝互連技術(shù)之一。基于 TSV 封裝的核心工藝包括 TSV 制造、RDL/微凸點(diǎn)加工、襯底減薄、圓片鍵合與薄圓片拿持等。

2023-05-08 10:35:24 2025

2025

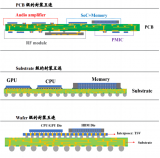

板級(jí)埋人式封裝是一種在基板制造工藝的基礎(chǔ)上融合芯片封裝工藝及 SMT工藝的集成封裝技術(shù),既可以是單芯片封裝、多芯片封裝,也可以是模組封裝、堆疊封裝。與傳統(tǒng)封裝中在基板表面貼裝芯片或元件不同,板級(jí)埋人式封裝直接將芯片或元件嵌人基板中間,因此它具有更短的互連路徑、更小的體積、更優(yōu)的電熱性能及更高的集成度。

2023-05-09 10:21:53 833

833

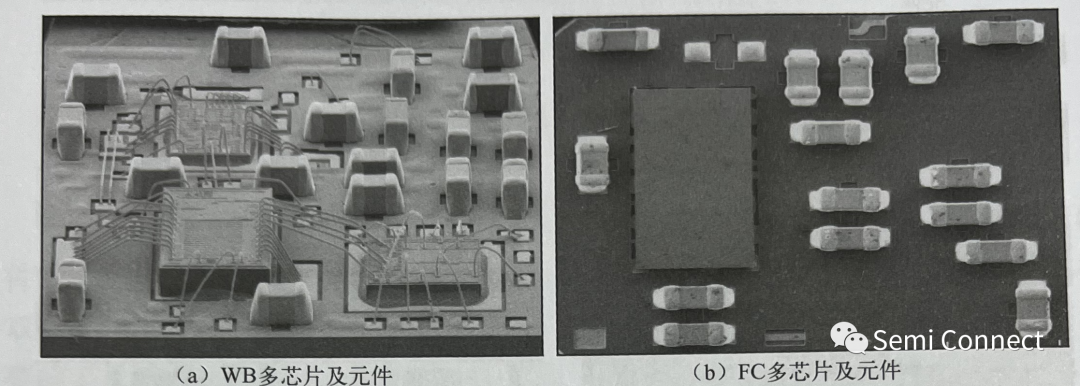

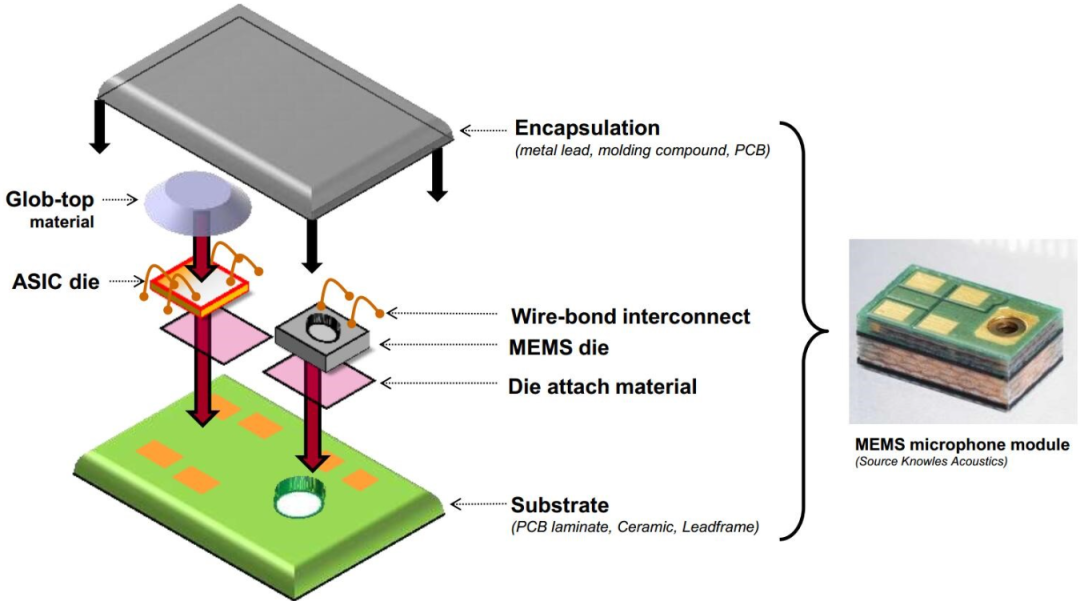

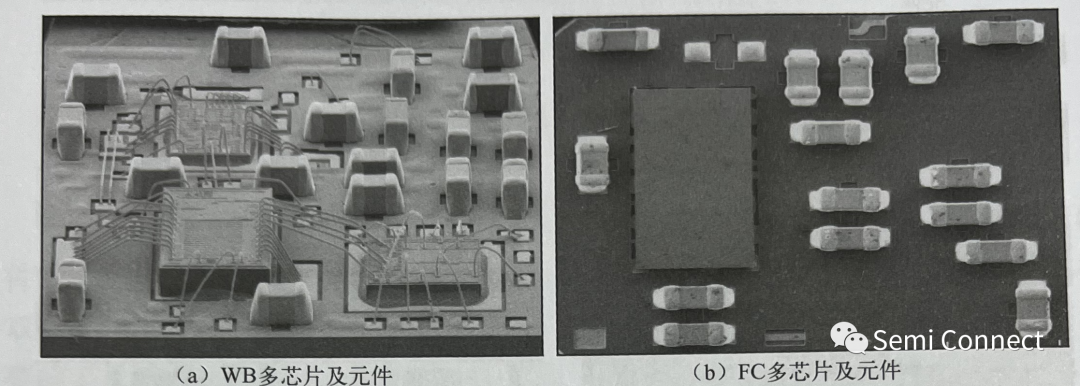

系統(tǒng)級(jí)封裝 (System in Package, SiP)是指將單個(gè)或多個(gè)芯片與各類元件通過系統(tǒng)設(shè)計(jì)及特定的封裝工藝集成于單一封裝體或模塊,從而實(shí)現(xiàn)具完整功能的電路集成,如圖 7-115 所示

2023-05-10 16:54:32 829

829

先進(jìn)封裝是“超越摩爾”(More than Moore)時(shí)代的一大技術(shù)亮點(diǎn)。當(dāng)芯片在每個(gè)工藝節(jié)點(diǎn)上的微縮越來越困難、也越來越昂貴之際,工程師們將多個(gè)芯片放入先進(jìn)的封裝中,就不必再費(fèi)力縮小芯片了。本文將對(duì)先進(jìn)封裝技術(shù)中最常見的10個(gè)術(shù)語進(jìn)行簡(jiǎn)單介紹。

2023-07-12 10:48:03 625

625

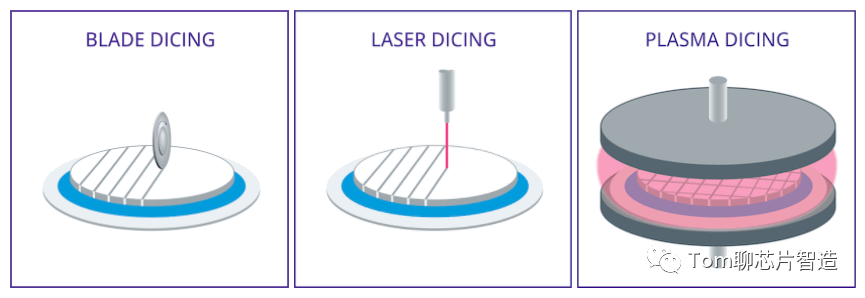

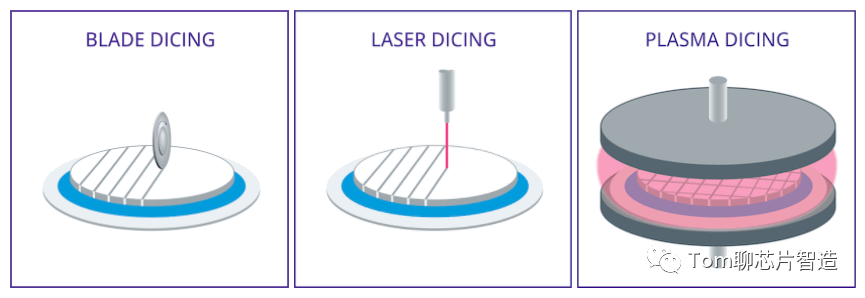

先進(jìn)封裝處于晶圓制造與封測(cè)的交叉區(qū)域 先進(jìn)封裝處于晶圓制造與封測(cè)制程中的交叉區(qū)域,涉及IDM、晶圓代工、封測(cè)廠商。先進(jìn)封裝要求在晶圓劃片前融入封裝工藝步驟,具體包括應(yīng)用晶圓研磨薄化、重布線(RDL

2023-08-07 10:59:46 852

852

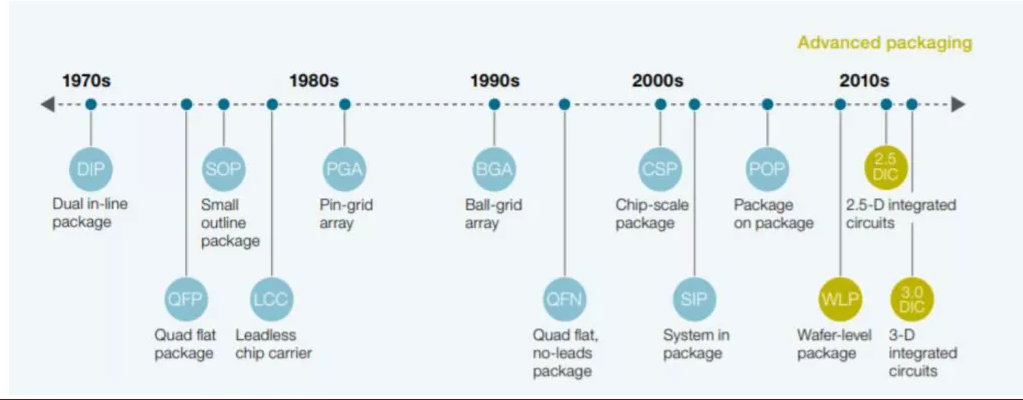

? 半導(dǎo)體器件有許多封裝形式,按封裝的外形、尺寸、結(jié)構(gòu)分類可分為引腳插入型、表面貼裝型和高級(jí)封裝三類。從DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技術(shù)指標(biāo)一代比一代先進(jìn)。總體說來

2023-08-28 09:37:11 1072

1072

隨著晶圓級(jí)封裝技術(shù)的不斷提升,眾多芯片設(shè)計(jì)及封測(cè)公司開始思考并嘗試采用晶圓級(jí)封裝技術(shù)替代傳統(tǒng)封裝。其中HRP(Heat?Re-distribution?Packaging)晶圓級(jí)先進(jìn)封裝工藝

2023-11-30 09:23:24 1124

1124

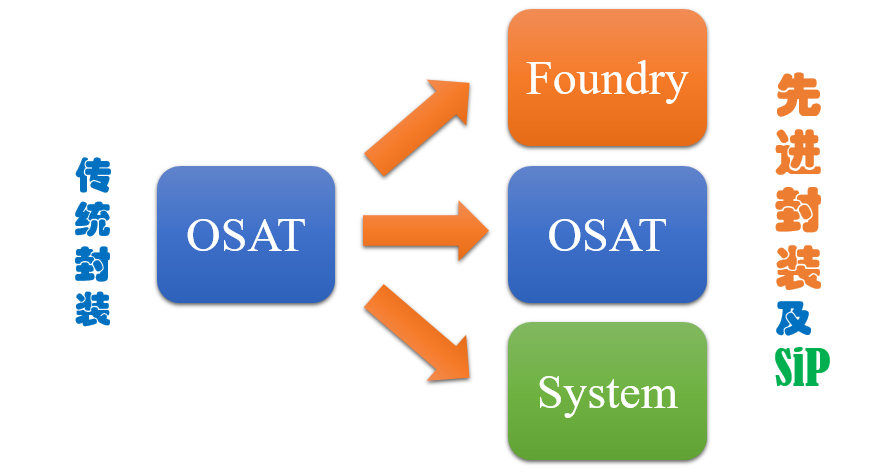

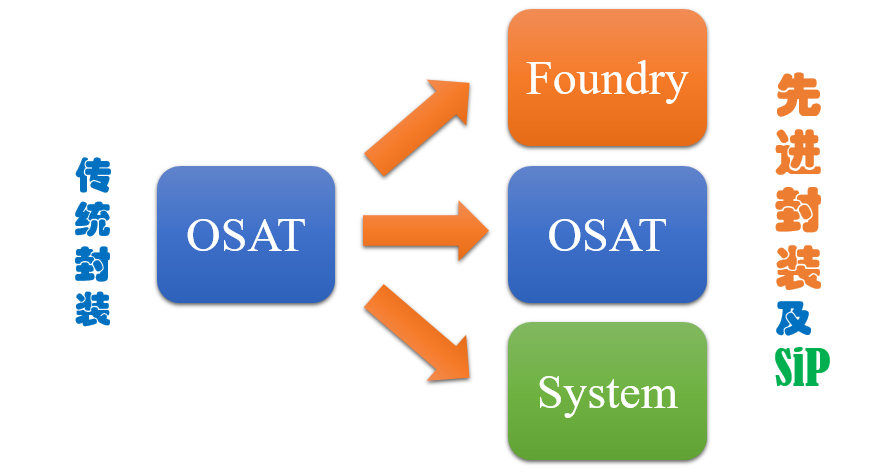

說起傳統(tǒng)封裝,大家都會(huì)想到日月光ASE,安靠Amkor,長電JCET,華天HT,通富微電TF等這些封裝大廠OSAT;說起先進(jìn)封裝,當(dāng)今業(yè)界風(fēng)頭最盛的卻是臺(tái)積電TSMC,英特爾Intel,三星SAMSUNG等這些頂尖的半導(dǎo)體晶圓廠IC Foundry,這是為何呢?

2023-12-21 09:32:02 474

474

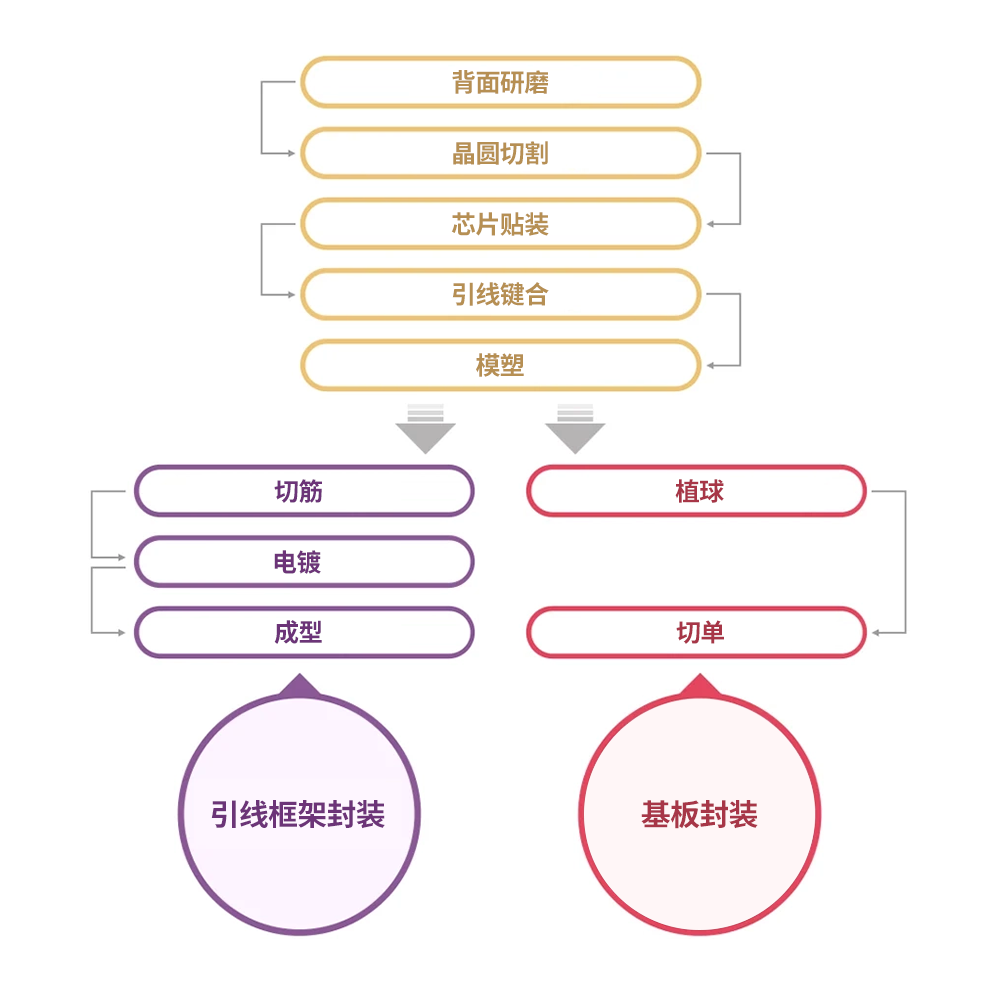

在晶圓制作完成后,會(huì)出貨給封裝廠,封裝廠再將一粒粒的芯片封裝起來。我這里所說的傳統(tǒng)封裝是指以打線為主的封裝方式,比如DIP,QFP,SOP,QFN等,不包括倒裝。這里就簡(jiǎn)單介紹一下傳統(tǒng)封裝的工藝流程及工藝特點(diǎn)。

2024-01-05 09:56:11 630

630

半導(dǎo)體器件有許多封裝形式,按封裝的外形、尺寸、結(jié)構(gòu)分類可分為引腳插入型、表面貼裝型和高級(jí)封裝三類。從DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技術(shù)指標(biāo)一代比一代先進(jìn)。總體說來,半導(dǎo)體

2024-01-16 09:54:34 606

606

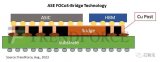

最近,在先進(jìn)封裝領(lǐng)域又出現(xiàn)了一個(gè)新的名詞“3.5D封裝”,以前聽?wèi)T了2.5D和3D封裝,3.5D封裝又有什么新的特點(diǎn)呢?還是僅僅是一個(gè)吸引關(guān)注度的噱頭?

2024-01-23 16:13:29 496

496

摘 要:先進(jìn)封裝技術(shù)不斷發(fā)展變化以適應(yīng)各種半導(dǎo)體新工藝和材料的要求和挑戰(zhàn)。在半導(dǎo)體封裝外部形式變遷的基礎(chǔ)上,著重闡述了半導(dǎo)體后端工序的關(guān)鍵一封裝內(nèi)部連接方式的發(fā)展趨勢(shì)。分析了半導(dǎo)體前端制造工藝的發(fā)展

2018-11-23 17:03:35

和基板介質(zhì)間還要具有較高的粘附性能。 BGA封裝技術(shù)通常采用引線鍵合、等離子清洗、模塑封裝、裝配焊料球、回流焊等工藝流程。引線鍵合PBGA的封裝工藝流程包括PBGA基板的制備和封裝工藝

2023-04-11 15:52:37

芯片封裝工藝流程IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right

2008-05-26 14:08:14

天線在分切過程中放卷復(fù)卷造成的損傷,這對(duì)比較敏感的銀漿印制天線尤其重要,同時(shí)生產(chǎn)速度也高很多。等產(chǎn)品從該生產(chǎn)線上下來,RFID標(biāo)簽的整套工藝就結(jié)束了。二、標(biāo)簽封裝流程1、涉及集成電路封裝技術(shù),比較特殊

2008-05-26 14:21:40

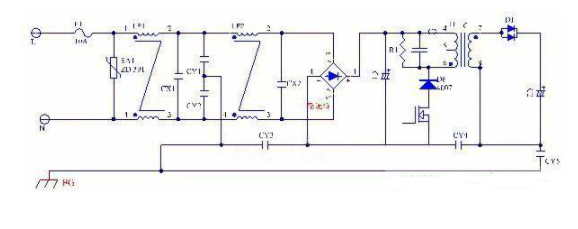

pcb電路板封裝工藝大全

2012-03-14 20:46:16

(1.5~40bar)將熱熔膠材料注入模具并快速固化成型(幾秒~幾分鐘)的封裝工藝方法。非常適合應(yīng)用于PCB印刷線路板封裝。 低溫低壓注塑封裝工藝優(yōu)勢(shì): 環(huán)保阻燃(UL 94 V-0)防塵防水級(jí)別

2018-01-03 16:30:44

的尺寸穩(wěn)定性和低的吸潮性,具有較好的電氣性能和高可靠性。金屬薄膜、絕緣層和基板介質(zhì)間還要具有較高的粘附性能。三大BGA封裝工藝及流程一、引線鍵合PBGA的封裝工藝流程1、PBGA基板的制備在BT樹脂

2018-09-18 13:23:59

論壇里好像沒有關(guān)于超薄封裝的問題~有沒有大神來介紹一下超薄封裝的工藝流程、前景、用途、材料等。如果能有有關(guān)的文獻(xiàn)就更好了~謝謝

2012-02-29 16:28:39

。基于散熱的要求,封裝越薄越好。 隨著芯片集成度的提高,芯片的發(fā)熱量也越來越大。除了采用更為精細(xì)的芯片制造工藝以外,封裝設(shè)計(jì)的優(yōu)劣也是至關(guān)重要的因素。設(shè)計(jì)出色的封裝形式可以大大的增加芯片的各項(xiàng)電器性能

2011-10-28 10:51:06

與工藝開發(fā)等技術(shù)工作;7. 完成領(lǐng)導(dǎo)安排的其他日常工作。封裝工藝/設(shè)備工程師崗位要求:1. 3年以上半導(dǎo)體行業(yè)封裝設(shè)備工作經(jīng)驗(yàn);2. 熟悉大功率半導(dǎo)體器件封裝關(guān)鍵工藝流程;3. 大學(xué)本科及以上學(xué)歷,電氣

2022-02-22 11:15:35

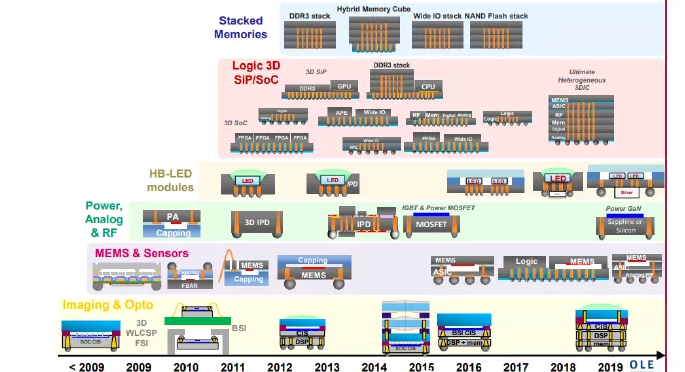

先進(jìn)封裝發(fā)展背景晶圓級(jí)三維封裝技術(shù)發(fā)展

2020-12-28 07:15:50

板上芯片封裝的焊接方法及工藝流程簡(jiǎn)述

2012-08-20 21:57:02

的主要制造技術(shù)。內(nèi)容包括電子制造技術(shù)概述、集成電路基礎(chǔ)、集成電路制造技術(shù)、元器件封裝工藝流程、元器件封裝形式及材料、光電器件制造與封裝、太陽能光伏技術(shù)、印制電路板技術(shù)以及電子組裝技術(shù)。書中簡(jiǎn)要介紹了

2017-03-23 19:39:21

本文簡(jiǎn)單講解芯片封裝工藝!

2016-06-16 08:36:25

與技術(shù)、陶瓷封裝、塑料封裝、氣密性封裝、封裝可靠性工程、封裝過程中的缺陷分析和先進(jìn)封裝技術(shù)。第1章 集成電路芯片封裝概述 第2章 封裝工藝流程 第3章 厚/薄膜技術(shù) 第4章 焊接材料 第5

2012-01-13 13:59:52

芯片封裝工藝流程,整個(gè)流程都介紹的很詳細(xì)。FOL,EOL。

2008-05-26 15:18:28 386

386 論文綜述了自 1990 年以來迅速發(fā)展的先進(jìn)封裝技術(shù),包括球柵陣列封裝(BGA)、芯片尺寸封裝(CSP)、圓片級(jí)封裝(WLP)、三維封裝(3D)和系統(tǒng)封裝(SiP)等項(xiàng)新技術(shù);同時(shí),敘述了我國封

2009-12-14 11:14:49 28

28 IC封裝工藝流程圖:貼膜,磨片,貼片,裝片,鍵合,電鍍,打印,切筋等流程。

2010-07-18 10:35:26 439

439 BGA的封裝工藝流程基本知識(shí)簡(jiǎn)介

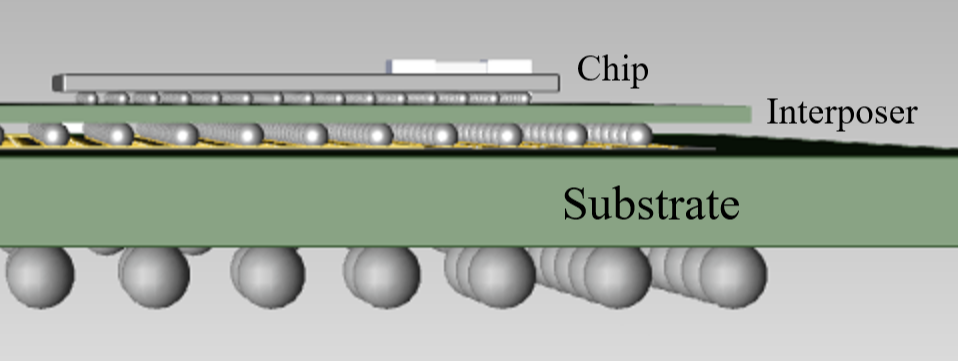

基板或中間層是BGA封裝中非常重要的部分,除了用于互連布線以外,還可用于阻抗控制及用于電感/電阻/電容的集成。因此要求

2010-03-04 13:44:06 6591

6591 LAMP-LED封裝工藝流程圖

2010-03-29 09:29:52 3545

3545 文章介紹了幾種新的封裝工藝,如新型圓片級(jí)封裝工藝OSmium 圓片級(jí)封裝工藝,它能夠把裸片面積減少一半;新型SiP封裝工藝Smafti封裝工藝,它改進(jìn)了傳統(tǒng)SiP封裝工藝,把傳輸速度提高了

2011-12-29 15:34:45 82

82 Siemens 業(yè)務(wù)部門 Mentor 今天宣布推出業(yè)內(nèi)最全面和高效的針對(duì)先進(jìn) IC 封裝設(shè)計(jì)的解決方案 — Xpedition 高密度先進(jìn)封裝 (HDAP) 流程。

2017-06-27 14:52:20 1777

1777 一、什么是COB封裝? COB封裝,是英語Chip On Board的縮寫,直譯就是芯片放在板上。 是一種區(qū)別于DIP和SMD封裝技術(shù)的新型封裝方式。如圖所示 在LED顯示技術(shù)領(lǐng)域,COB封裝工藝

2017-09-30 11:10:25 95

95 由于晶圓級(jí)封裝不需要中介層、填充物與導(dǎo)線架,并且省略黏晶、打線等制程,能夠大幅減少材料以及人工成本;已經(jīng)成為強(qiáng)調(diào)輕薄短小特性的可攜式電子產(chǎn)品 IC 封裝應(yīng)用的之選。FuzionSC貼片機(jī)能應(yīng)對(duì)這種先進(jìn)工藝。

2018-05-11 16:52:52 51899

51899

芯片封裝測(cè)試的流程你了解嗎IC封裝工藝詳細(xì)PPT簡(jiǎn)介

2019-05-12 09:56:59 28447

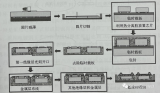

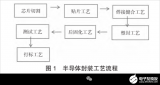

28447 等工藝。典型的封裝工藝流程為:劃片 裝片 鍵合 塑封 去飛邊 電鍍 打印 切筋和成型 外觀檢查 成品測(cè)試包裝出貨。 半導(dǎo)體封裝是指將通過測(cè)試的晶圓按照產(chǎn)品型號(hào)及功能需求加工得到獨(dú)立芯片的過程。封裝過程為:來自晶圓前道工藝的晶圓通過劃片工藝后被切割為小的晶片(Die),然后

2020-03-27 16:40:06 8086

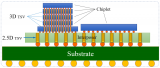

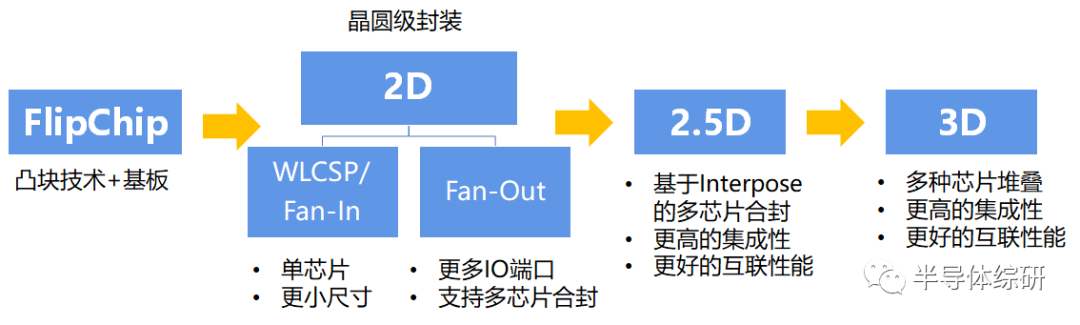

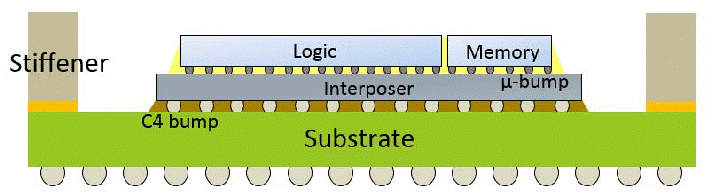

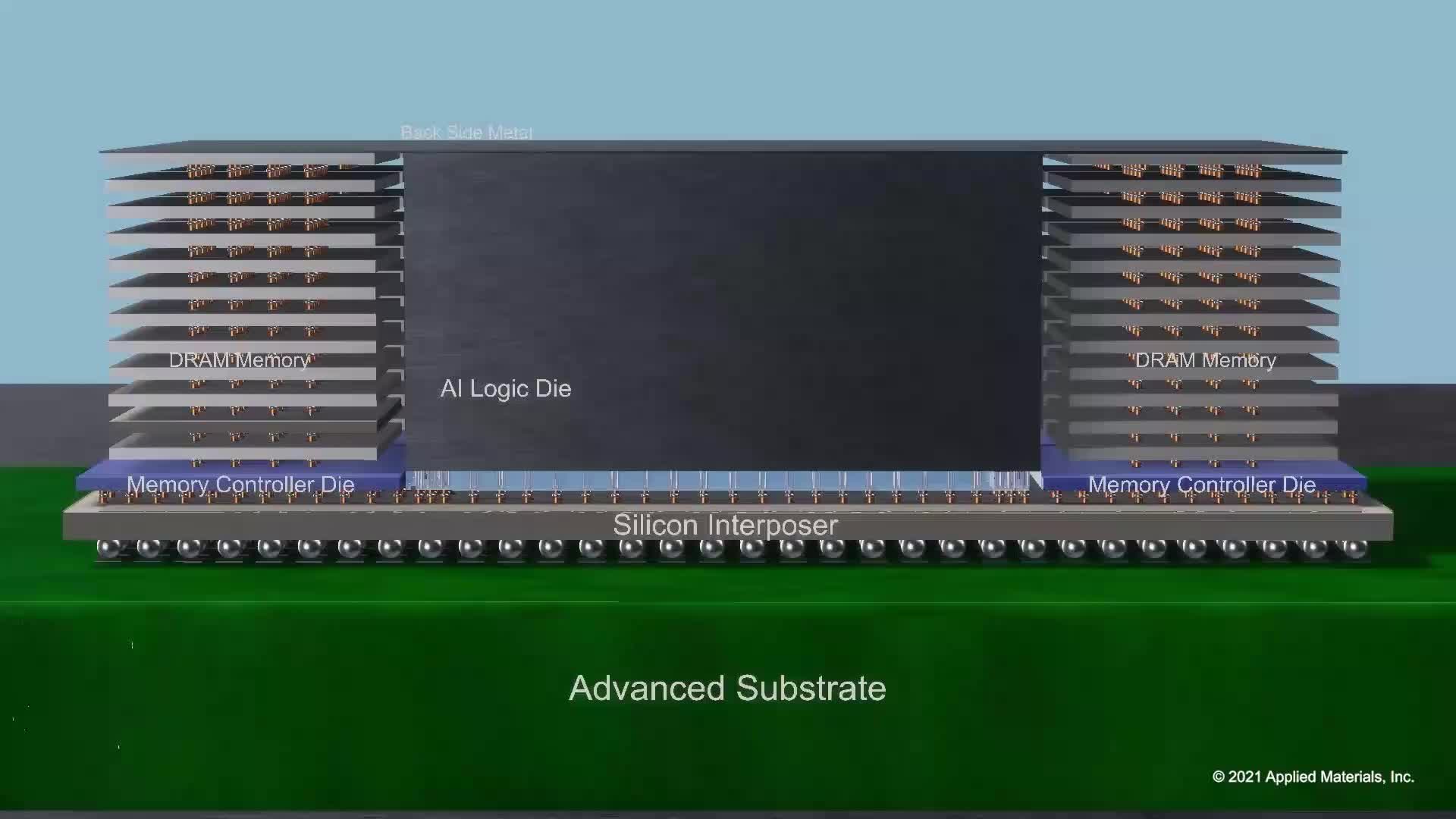

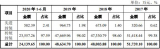

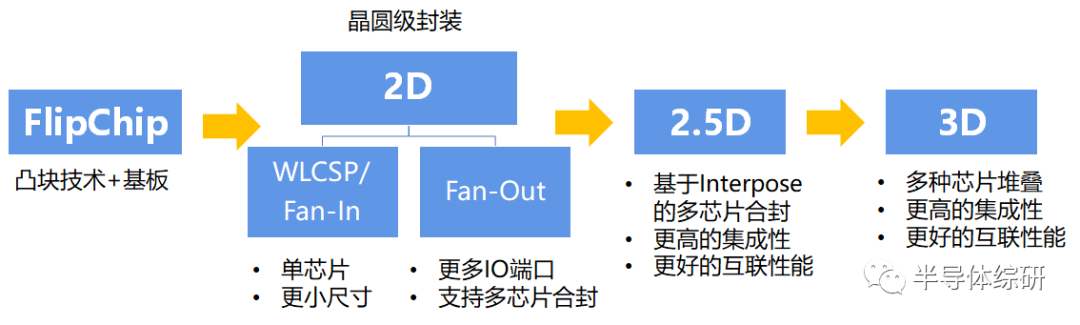

8086 再就是2.5D/3D先進(jìn)封裝集成,新興的2.5D和3D技術(shù)有望擴(kuò)展到倒裝(FC)芯片和晶圓級(jí)封裝(WLP)工藝中。通過使用內(nèi)插器(interposers)和硅通孔(TSV)技術(shù),可以將多個(gè)芯片進(jìn)行垂直堆疊。據(jù)報(bào)道,與傳統(tǒng)包裝相比,使用3D技術(shù)可以實(shí)現(xiàn)40~50倍的尺寸和重量減少。

2020-10-10 16:09:18 3741

3741 (Waferlevelpackage),2.5D封裝(interposer,RDL等),3D封裝(TSV)等先進(jìn)封裝技術(shù)。 ▌ SoC vs.SiP ?SoC:全稱System-on-chip,系統(tǒng)級(jí)芯片

2020-10-21 11:03:11 28156

28156

據(jù)筆者查詢發(fā)現(xiàn),前不久藍(lán)箭電子科創(chuàng)板IPO已經(jīng)獲得第二輪問詢,主要是圍繞先進(jìn)封裝工藝展開,同時(shí)質(zhì)疑藍(lán)箭科技在傳統(tǒng)封裝業(yè)務(wù)方面的發(fā)展。那么,藍(lán)箭電子目前的技術(shù)水平如何?與A股同行公司相比有多大的技術(shù)差距?

2020-12-03 16:30:55 3669

3669

芯片封裝早已不再僅限于傳統(tǒng)意義上為獨(dú)立芯片提供保護(hù)和I/O擴(kuò)展接口,如今有越來越多的封裝技術(shù)能夠?qū)崿F(xiàn)多種不同芯片之間的互聯(lián)。先進(jìn)封裝工藝能提高器件密度并由此減小空間占用,這一點(diǎn)對(duì)于手機(jī)和自動(dòng)駕駛汽車等電子設(shè)備的功能疊加來說至關(guān)重要

2020-12-24 14:23:09 528

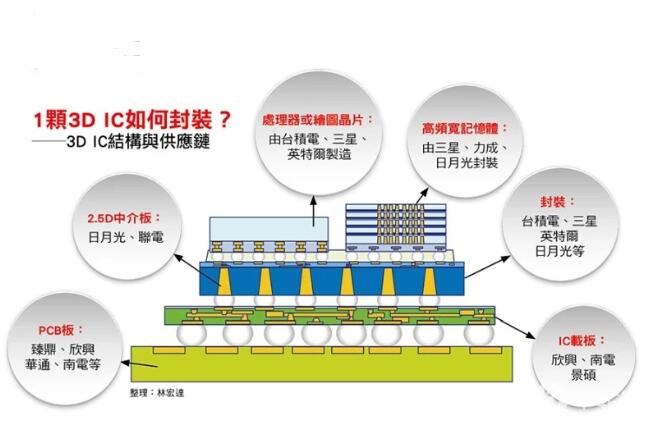

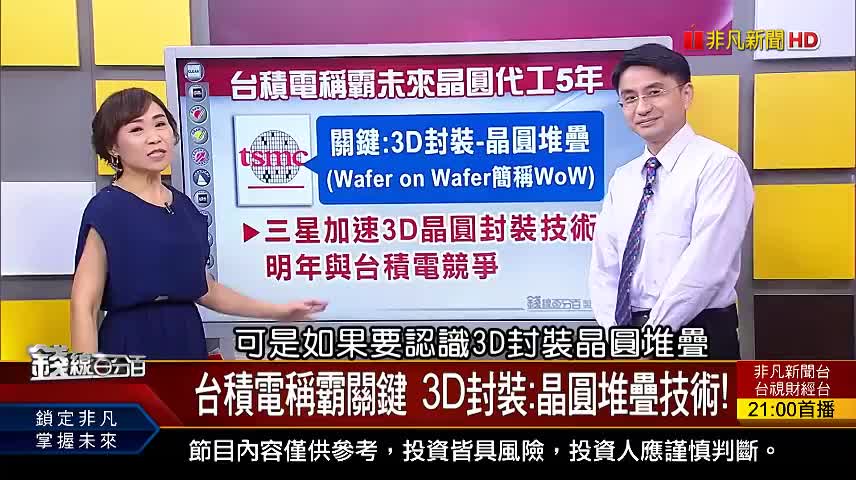

528 臺(tái)積電和三星于先進(jìn)封裝的戰(zhàn)火再起。2020年,三星推出3D封裝技術(shù)品牌X-Cube,宣稱在7納米芯片可直接堆上SRAM內(nèi)存,企圖在先進(jìn)封裝拉近與臺(tái)積電的距離。幾天之后,臺(tái)積電總裁魏哲家現(xiàn)身,宣布推出自有先進(jìn)封裝品牌3D Fabric,臺(tái)積電最新的SoIC(系統(tǒng)集成芯片)備受矚目。

2021-01-04 10:37:09 1269

1269

和電路板技術(shù),即集成芯片;半導(dǎo)體主要芯片已不再掌握在少數(shù)廠商;以及中芯國際先進(jìn)工藝和先進(jìn)封裝都會(huì)發(fā)展、半導(dǎo)體產(chǎn)業(yè)需建立完整的生態(tài)環(huán)境才能在全球市場(chǎng)競(jìng)爭(zhēng)中取勝等。 蔣尚義指出,先進(jìn)工藝研發(fā)是基石,因應(yīng)摩爾定律

2021-01-19 10:25:02 2859

2859 先進(jìn)封裝大部分是利用「晶圓廠」的技術(shù),直接在晶圓上進(jìn)行,由于這種技術(shù)更適合晶圓廠來做,因此臺(tái)積電大部分的先進(jìn)封裝都是自己做的。

2021-02-22 11:45:21 2200

2200

說,我的i Watch采用了SiP技術(shù),SiP從此廣為人知;臺(tái)積電說,除了先進(jìn)工藝,我還要搞先進(jìn)封裝,先進(jìn)封裝因此被業(yè)界提到了和先進(jìn)工藝同等重要的地位。 近些年,先進(jìn)封裝技術(shù)不斷涌現(xiàn),新名詞也層出不窮,讓人有些眼花繚亂,目前可以列出的先進(jìn)封裝相關(guān)的名

2021-04-01 16:07:24 32556

32556

集成電路芯片封裝工藝流程有哪些?

2021-07-28 15:28:16 12132

12132 芯片封裝工藝流程是什么 在電子產(chǎn)品中,芯片是非常重要的,缺少芯片的話,很多產(chǎn)品都制作不了,那么芯片封裝工藝流程是什么呢?下面我們就來了解一下芯片封裝工藝流程。 芯片封裝是指芯片在框架或基板上布局

2021-08-09 11:53:54 64837

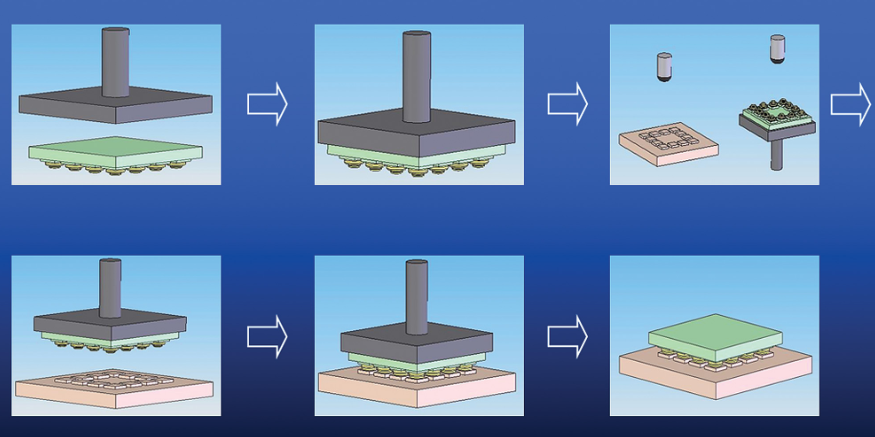

64837 Chip First工藝 自從Fan-Out封裝問世以來,經(jīng)過多年的技術(shù)發(fā)展,扇出式封裝已經(jīng)形成了多種封裝流程、封裝結(jié)構(gòu)以適應(yīng)不同產(chǎn)品需要,根據(jù)工藝流程,可以分為先貼芯片后加工RDL的Chip

2021-10-12 10:17:51 10046

10046 先進(jìn)封裝技術(shù)FC/WLCSP的應(yīng)用與發(fā)展分析。

2022-05-06 15:19:12 24

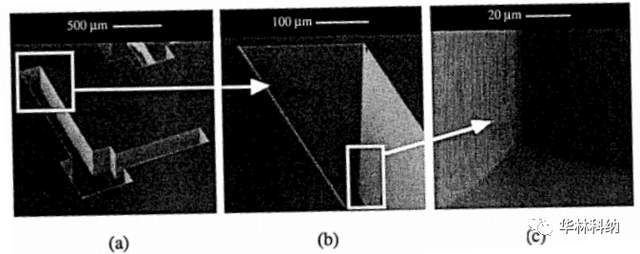

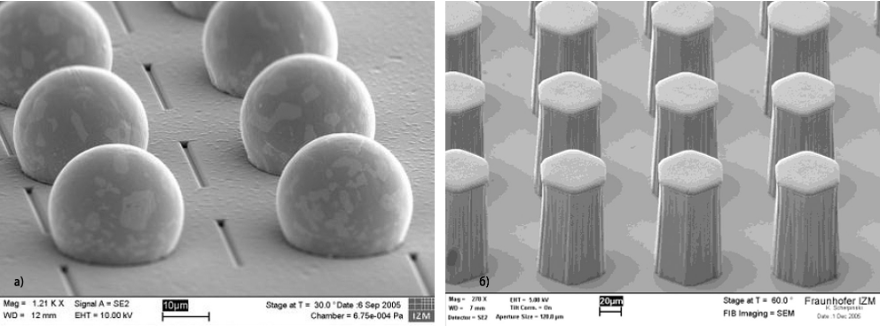

24 在本文中講述了HARSE的工藝條件,其產(chǎn)生超過3微米/分鐘的蝕刻速率和控制良好的、高度各向異性的蝕刻輪廓,還將成為展示先進(jìn)封裝技術(shù)的潛在應(yīng)用示例。

2022-05-09 15:11:45 443

443

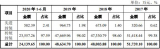

2021年對(duì)于先進(jìn)封裝行業(yè)來說是豐收一年,現(xiàn)在包括5G、汽車信息娛樂/ADAS、人工智能、數(shù)據(jù)中心和可穿戴應(yīng)用在內(nèi)的大趨勢(shì)繼續(xù)迫使芯片向先進(jìn)封裝發(fā)展。2021年先進(jìn)封裝市場(chǎng)總收入為321億美元,預(yù)計(jì)

2022-06-13 14:01:24 2047

2047 芯片封裝的目的在于確保芯片經(jīng)過封裝之后具有較強(qiáng)的機(jī)械性能、良好的電氣性能和散熱性能,可以對(duì)芯片起到機(jī)械和環(huán)境保護(hù)的作用,保證芯片能夠保持高效穩(wěn)定的正常工作。那么,芯片封裝工藝流程是什么呢?

2022-10-31 10:14:25 9918

9918 封裝工藝流程--芯片互連技術(shù)

2022-12-05 13:53:52 1719

1719 近年來,先進(jìn)封裝技術(shù)的內(nèi)驅(qū)力已從高端智能手機(jī)領(lǐng)域演變?yōu)楦咝阅苡?jì)算和人工智能等領(lǐng)域,涉及高性能處理器、存儲(chǔ)器、人工智能訓(xùn)練和推理等。當(dāng)前集成電路的發(fā)展受“四堵墻”(“存儲(chǔ)墻”“面積墻”“功耗

2022-12-28 14:16:29 3295

3295 采用了先進(jìn)的設(shè)計(jì)思路和先進(jìn)的集成工藝、縮短引線互連長度,對(duì)芯片進(jìn)行系統(tǒng)級(jí)封裝的重構(gòu),并且能有效提高系統(tǒng)功能密度的封裝。現(xiàn)階段的先進(jìn)封裝是指:倒裝焊(FlipChip)、晶圓級(jí)封裝(WLP)、2.5D封裝(Interposer、RDL)、3D封裝(TSV)

2023-01-13 10:58:41 1220

1220 芯片組裝工藝。由于采用了中介轉(zhuǎn)接層,其表面金屬層的布線可以使用與芯片表面布線相同的工藝,使產(chǎn)品在容量及性能上比2D結(jié)構(gòu)得到巨大提升。

2023-02-20 10:44:49 4446

4446 SiP是一個(gè)非常寬泛的概念,廣義上看,它囊括了幾乎所有多芯片封裝技術(shù),但就最先進(jìn)SiP封裝技術(shù)而言,主要包括 2.5D/3D Fan-out(扇出)、Embedded、2.5D/3D Integration,以及異構(gòu)Chiplet封裝技術(shù)。

2023-03-20 09:51:54 1037

1037

芯片升級(jí)的兩個(gè)永恒主題:性能、體積/面積。芯片技術(shù)的發(fā)展,推動(dòng)著芯片朝著高性能和輕薄化兩個(gè)方向提升。而先進(jìn)制程和先進(jìn)封裝的進(jìn)步,均能夠使得芯片向著高性能和輕薄化前進(jìn)。面對(duì)美國的技術(shù)封裝,華為

2023-04-15 09:48:56 1953

1953 SiP系統(tǒng)級(jí)封裝(System in Package),先進(jìn)封裝HDAP(High Density Advanced Package),兩者都是當(dāng)今芯片封裝技術(shù)的熱點(diǎn),受到整個(gè)半導(dǎo)體產(chǎn)業(yè)鏈的高度關(guān)注

2023-05-19 09:54:26 1326

1326

先進(jìn)封裝是對(duì)應(yīng)于先進(jìn)圓晶制程而衍生出來的概念,一般指將不同系統(tǒng)集成到同一封裝內(nèi)以實(shí)現(xiàn)更高效系統(tǒng)效率的封裝技術(shù)。

2023-06-13 11:33:24 282

282

一、核心結(jié)論 ?1、先進(jìn)制程受限,先進(jìn)封裝/Chiplet提升算力,必有取舍。在技術(shù)可獲得的前提下,提升芯片性能,先進(jìn)制程升級(jí)是首選,先進(jìn)封裝則錦上添花。 2、大功耗、高算力的場(chǎng)景,先進(jìn)封裝

2023-06-13 11:38:05 747

747

緊密相連。在業(yè)界,先進(jìn)封裝技術(shù)與傳統(tǒng)封裝技術(shù)以是否焊線來區(qū)分。先進(jìn)封裝技術(shù)包括FCBGA、FCQFN、2.5D/3D、WLCSP、Fan-Out等非焊線形式。先進(jìn)

2022-04-08 16:31:15 641

641

當(dāng)我們購買電子產(chǎn)品時(shí),比如手機(jī)、電視或計(jì)算機(jī),這些設(shè)備內(nèi)部都有一個(gè)重要的組成部分,那就是半導(dǎo)體芯片。半導(dǎo)體芯片是由許多微小的電子元件組成的,為了保護(hù)和使用這些芯片,它們需要經(jīng)過一個(gè)被稱為封裝的工藝流程。下面是半導(dǎo)體芯片封裝的通俗易懂的工藝流程。

2023-06-26 13:50:43 1572

1572 在異質(zhì)異構(gòu)的世界里,chiplet是“生產(chǎn)關(guān)系”,是決定如何拆分及組合芯粒的方式與規(guī)則;先進(jìn)封裝技術(shù)是“生產(chǎn)力”,通過堆疊、拼接等方法實(shí)現(xiàn)不同芯粒的互連。先進(jìn)封裝技術(shù)已成為實(shí)現(xiàn)異質(zhì)異構(gòu)的重要前提。

2023-06-26 17:14:57 601

601 AI訂單激增,影響傳至先進(jìn)封裝市場(chǎng)。

2023-07-05 18:19:37 776

776

1. 先進(jìn)制程受限,先進(jìn)封裝/Chiplet提升算力,必有取舍。

2023-07-07 09:42:04 1693

1693

Chiplet技術(shù)是一種利用先進(jìn)封裝方法將不同工藝/功能的芯片進(jìn)行異質(zhì)集成的技術(shù)。這種技術(shù)設(shè)計(jì)的核心思想是先分后合,即先將單芯片中的功能塊拆分出來,再通過先進(jìn)封裝模塊將其集成為大的單芯片。

2023-07-17 09:21:50 2309

2309

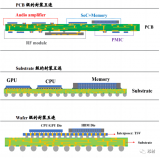

level package),2.5D封裝(interposer,RDL等),3D封裝(TSV)等先進(jìn)封裝技術(shù)。

2023-08-05 09:54:29 398

398

先進(jìn)封裝處于晶圓制造與封測(cè)制程中的交叉區(qū)域,涉及IDM、晶圓代工、封測(cè)廠商,市場(chǎng)格局較為集中,前6 大廠商份額合計(jì)超過80%。全球主要的 6 家廠商,包括 2 家 IDM 廠商(英特爾、三星),一家

2023-08-11 09:11:48 456

456

半導(dǎo)體器件有許多封裝形式,按封裝的外形、尺寸、結(jié)構(gòu)分類可分為引腳插入型、表面貼裝型和高級(jí)封裝三類。從DIP、SOP、QFP、PGA、BGA到CSP再到SIP,技術(shù)指標(biāo)一代比一代先進(jìn)。

2023-08-14 09:59:17 1086

1086

來源:ACT半導(dǎo)體芯科技 隨著中國半導(dǎo)體產(chǎn)業(yè)的不斷升級(jí),國內(nèi)的傳統(tǒng)封裝工藝繼續(xù)保持優(yōu)勢(shì),同時(shí)先進(jìn)封裝技術(shù)在下游應(yīng)用需求驅(qū)動(dòng)下快速發(fā)展。特別是超算、物聯(lián)網(wǎng)、智能終端產(chǎn)品等對(duì)芯片體積和功耗的苛求,這些

2023-08-18 17:57:49 775

775

隨著芯片制造持續(xù)往更小的制程節(jié)點(diǎn)邁進(jìn),晶圓代工廠利用先進(jìn)封裝技術(shù)直接封裝晶片的模式乃應(yīng)運(yùn)而生。不過,此模式也意味著晶圓代工廠將攫取傳統(tǒng)封測(cè)廠的部分業(yè)務(wù),所以自從臺(tái)積電于 2011 年宣布進(jìn)軍先進(jìn)封裝領(lǐng)域之后,其對(duì)于傳統(tǒng)封測(cè)廠的“威脅論”就不曾間斷,那么此說法是否屬實(shí)呢?

2023-08-23 16:33:57 613

613

來源:ACT半導(dǎo)體芯科技 隨著中國半導(dǎo)體產(chǎn)業(yè)的不斷升級(jí),國內(nèi)的傳統(tǒng)封裝工藝繼續(xù)保持優(yōu)勢(shì),同時(shí)先進(jìn)封裝技術(shù)在下游應(yīng)用需求驅(qū)動(dòng)下快速發(fā)展。特別是超算、物聯(lián)網(wǎng)、智能終端產(chǎn)品等對(duì)芯片體積和功耗的苛求,這些

2023-08-25 17:06:10 300

300

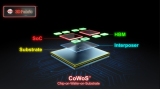

2023年以來,AIGC迅速發(fā)展,帶動(dòng)AI芯片與AI服務(wù)器熱潮,而由臺(tái)積電推出、被稱為CoWoS的2.5D先進(jìn)封裝技術(shù)更是扮演關(guān)鍵角色。然而,突如其來的需求讓臺(tái)積電應(yīng)接不暇,面對(duì)此情況,傳統(tǒng)封測(cè)大廠如日月光、Amkor也相繼展現(xiàn)技術(shù)實(shí)力,并未打算在此領(lǐng)域缺席。

2023-09-18 10:51:49 263

263

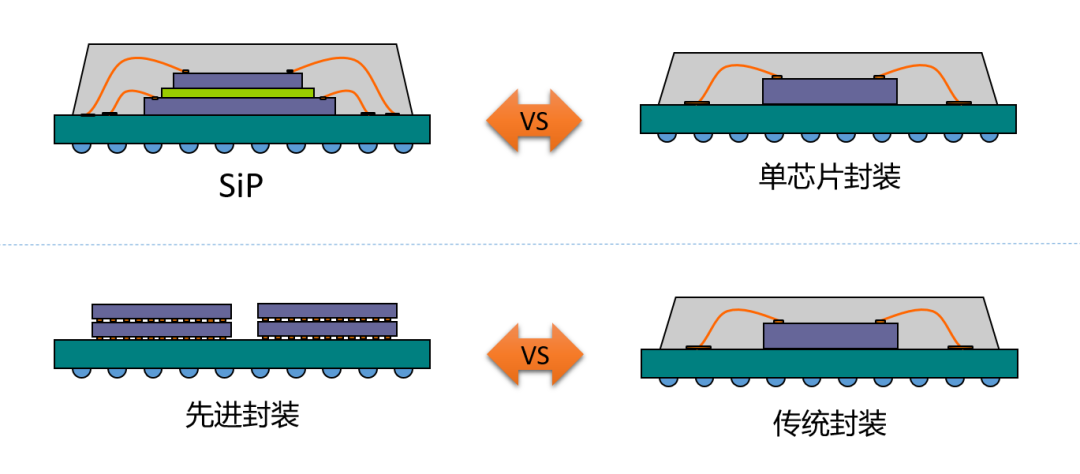

先進(jìn)封裝增速高于整體封裝,將成為全球封裝市場(chǎng)主要增量。根據(jù)Yole的數(shù)據(jù),全球封裝市場(chǎng)規(guī)模穩(wěn)步增長,2021 年全球封裝 市場(chǎng)規(guī)模 約達(dá) 777 億美元。其中,先進(jìn)封裝全球市場(chǎng)規(guī)模約 350 億美元,占比約 45%, 2025 年,先進(jìn)封裝在全部封裝市場(chǎng)的 占比將增長至 49.4%。

2023-09-22 10:43:18 1189

1189

先進(jìn)封裝技術(shù)以SiP、WLP、2.5D/3D為三大發(fā)展重點(diǎn)。先進(jìn)封裝核心技術(shù)包括Bumping凸點(diǎn)、RDL重布線、硅中介層和TSV通孔等,依托這些技術(shù)的組合各廠商發(fā)展出了滿足多樣化需求的封裝解決方案,SiP系統(tǒng)級(jí)封裝、WLP晶圓級(jí)封裝、2.5D/3D封裝為三大發(fā)展重點(diǎn)。

2023-09-28 15:29:37 1614

1614

此時(shí)先進(jìn)封裝開始嶄露頭角,以蘋果和臺(tái)積電為代表,開啟了一場(chǎng)新的革命,其主要分為兩大類,一種是基于XY平面延伸的先進(jìn)封裝技術(shù),主要通過RDL進(jìn)行信號(hào)的延伸和互連;第二種則是基于Z軸延伸的先進(jìn)封裝技術(shù),主要通過TSV進(jìn)行信號(hào)延伸和互連。

2023-10-10 17:04:30 573

573

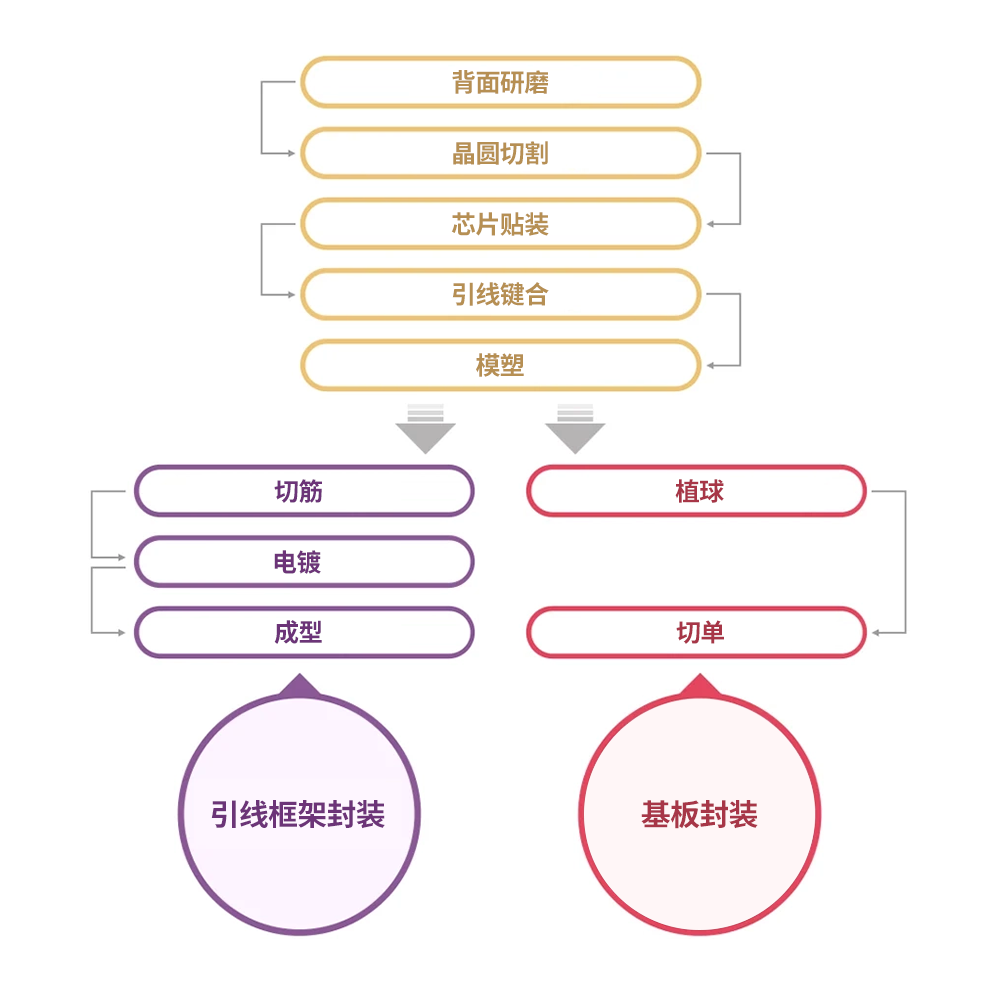

圖1顯示了塑料封裝的組裝工藝,塑料封裝是一種傳統(tǒng)封裝方法,分為引線框架封裝(Leadframe Package)和基板封裝(Substrate Package)。這兩種封裝工藝的前半部分流程相同,而后半部分流程則在引腳連接方式上存在差異。

2023-10-17 14:28:56 743

743

半導(dǎo)體產(chǎn)品在由二維向三維發(fā)展,從技術(shù)發(fā)展方向半導(dǎo)體產(chǎn)品出現(xiàn)了系統(tǒng)級(jí)封裝(SiP)等新的封裝方式,從技術(shù)實(shí)現(xiàn)方法出現(xiàn)了倒裝(FlipChip),凸塊(Bumping),晶圓級(jí)封裝(Waferlevelpackage),2.5D封裝(interposer,RDL等),3D封裝(TSV)等先進(jìn)封裝技術(shù)。

2023-10-31 09:16:29 836

836

近年來,隨著晶圓級(jí)封裝技術(shù)的不斷提升,眾多芯片設(shè)計(jì)及封測(cè)公司開始思考并嘗試采用晶圓級(jí)封裝技術(shù)替代傳統(tǒng)封裝。其中HRP(Heat Re-distribution Packaging)晶圓級(jí)先進(jìn)封裝工藝

2023-11-18 15:26:58 0

0 IGBT模塊的封裝技術(shù)難度高,高可靠性設(shè)計(jì)和封裝工藝控制是其技術(shù)難點(diǎn)。

2023-11-21 15:49:45 673

673

我們?yōu)槭裁葱枰私庖恍?b class="flag-6" style="color: red">先進(jìn)封裝?

2023-11-23 16:32:06 281

281

先進(jìn)封裝基本術(shù)語

2023-11-24 14:53:10 362

362

相比于晶圓制造,中國大陸封測(cè)環(huán)節(jié)較為成熟,占據(jù)全球封測(cè)接近40%的份額,但中國大陸先進(jìn)封裝的滲透率較低,2022年僅為14%,低于全球45%的滲透率。在制程工藝受到外部制裁的背景下

2023-11-25 15:44:25 740

740 LED顯示屏行業(yè)發(fā)展至今,已經(jīng)出現(xiàn)過多種生產(chǎn)封裝工藝,小間距市場(chǎng)目前以SMT貼片技術(shù)為主,在微間距市場(chǎng),COB封裝技術(shù)憑借更高像素密度,更精密的顯示效果,越來越獲得市場(chǎng)認(rèn)可。

2023-12-27 09:46:21 830

830 level package),2.5D封裝(interposer,RDL等),3D封裝(TSV)等先進(jìn)封裝技術(shù)。 審核編輯 黃宇

2024-02-21 10:34:20 178

178

因?yàn)锳I芯片需求的大爆發(fā),臺(tái)積電先進(jìn)封裝產(chǎn)能供不應(yīng)求,而且產(chǎn)能供不應(yīng)求的狀況可能延續(xù)到2025年;這是臺(tái)積電總裁魏哲家在法人說明會(huì)上透露的。 而且臺(tái)積電一直持續(xù)的擴(kuò)張先進(jìn)封裝產(chǎn)能,但是依然不能滿足AI的強(qiáng)勁需求;這在一定程度會(huì)使得其他相關(guān)封裝廠商因?yàn)榻邮苻D(zhuǎn)單而受益。

2024-01-22 18:48:08 565

565 共讀好書 張?chǎng)?苑明星 楊小渝 (重慶市聲光電有限公司) 摘 要: 對(duì)半導(dǎo)體封裝工藝的研究,先探析半導(dǎo)體工藝概述,能對(duì)其工作原理有一定的了解與掌握;再考慮半導(dǎo)體封裝工藝流程,目的是在作業(yè)階段嚴(yán)謹(jǐn)

2024-02-25 11:58:10 275

275

臺(tái)積電計(jì)劃在嘉義科學(xué)園區(qū)投資超過5000億元新臺(tái)幣,建設(shè)六座先進(jìn)封裝廠,這一舉措無疑將對(duì)半導(dǎo)體產(chǎn)業(yè)產(chǎn)生深遠(yuǎn)影響。

2024-03-20 11:28:14 335

335

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論